- Advanced Multibus Architecture With Three Separate 16-Bit Data Memory Buses and One Program Memory Bus

- 40-Bit Arithmetic Logic Unit (ALU) Including a 40-Bit Barrel Shifter and Two Independent 40-Bit Accumulators

- 17- × 17-Bit Parallel Multiplier Coupled to a 40-Bit Dedicated Adder for Non-Pipelined Single-Cycle Multiply/Accumulate (MAC) Operation

- Compare, Select, and Store Unit (CSSU) for the Add/Compare Selection of the Viterbi Operator

- Exponent Encoder to Compute an Exponent Value of a 40-Bit Accumulator Value in a Single Cycle

- Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Data Bus With a Bus Holder Feature

- Address Bus With a Bus Holder Feature ('548 and '549 Only)

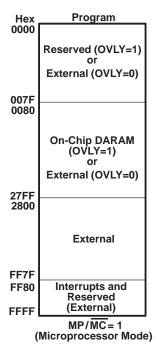

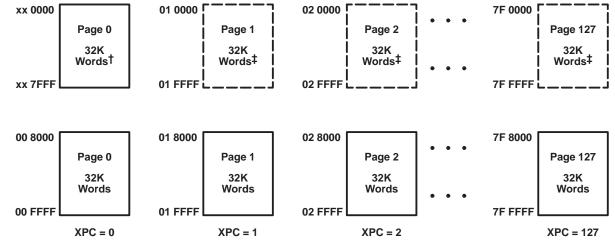

- Extended Addressing Mode for 8M × 16-Bit Maximum Addressable External Program Space ('548 and '549 Only)

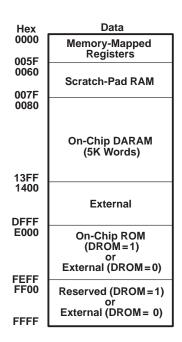

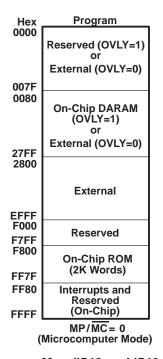

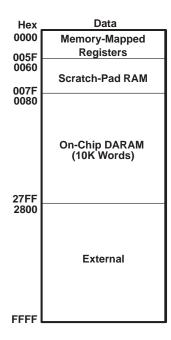

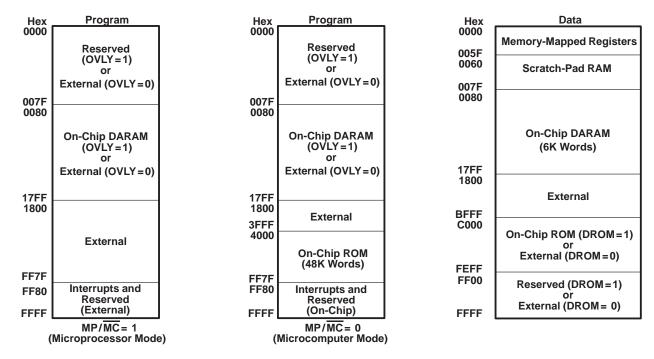

- 192K × 16-Bit Maximum Addressable Memory Space (64K Words Program, 64K Words Data, and 64K Words I/O)

- On-Chip ROM with Some Configurable to Program/Data Memory

- Dual-Access On-Chip RAM

- Single-Access On-Chip RAM ('548/'549)

- Single-Instruction Repeat and Block-Repeat Operations for Program Code

- Block-Memory-Move Instructions for Better Program and Data Management

- Instructions With a 32-Bit Long Word Operand

- Instructions With Two- or Three-Operand Reads

- Arithmetic Instructions With Parallel Store and Parallel Load

- Conditional Store Instructions

- Fast Return From Interrupt

- On-Chip Peripherals

- Software-Programmable Wait-State Generator and Programmable Bank Switching

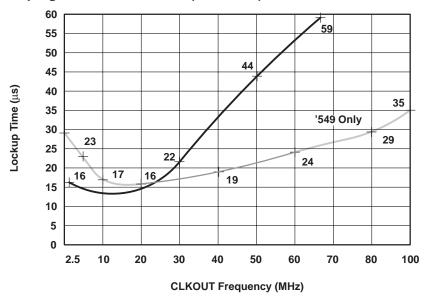

- On-Chip Phase-Locked Loop (PLL) Clock Generator With Internal Oscillator or External Clock Source

- Full-Duplex Serial Port to Support 8- or 16-Bit Transfers ('541, 'LC545, and 'LC546 Only)

- Time-Division Multiplexed (TDM) Serial Port ('542, '543, '548, and '549 Only)

- Buffered Serial Port (BSP) ('542, '543, 'LC545, 'LC546, '548, and '549 Only)

- 8-Bit Parallel Host-Port Interface (HPI)

('542, 'LC545, '548, and '549)

- One 16-Bit Timer

- External-Input/Output (XIO) Off Control to Disable the External Data Bus,

Address Bus and Control Signals

- Power Consumption Control With IDLE1, IDLE2, and IDLE3 Instructions With Power-Down Modes

- CLKOUT Off Control to Disable CLKOUT

- On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1<sup>†</sup> (JTAG) Boundary Scan Logic

- 25-ns Single-Cycle Fixed-Point Instruction Execution Time [40 MIPS] for 5-V Power Supply ('C541 and 'C542 Only)

- 20-ns and 25-ns Single-Cycle Fixed-Point Instruction Execution Time (50 MIPS and 40 MIPS) for 3.3-V Power Supply ('LC54x)

- 15-ns Single-Cycle Fixed-Point Instruction Execution Time (66 MIPS) for 3.3-V Power Supply ('LC54xA, '548, 'LC549)

- 12.5-ns Single-Cycle Fixed-Point Instruction Execution Time (80 MIPS) for 3.3-V Power Supply ('LC548, 'LC549)

- 10-ns and 8.3-ns Single-Cycle Fixed-Point Instruction Execution Time (100 and 120 MIPS) for 3.3-V Power Supply (2.5-V Core) ('VC549)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

## description

The TMS320C54x, TMS320LC54x, and TMS320VC54x fixed-point, digital signal processor (DSP) families (hereafter referred to as the '54x unless otherwise specified) are based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. These processors also provide an arithmetic logic unit (ALU) that has a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. These DSP families also provide a highly specialized instruction set, which is the basis of the operational flexibility and speed of these DSPs.

Separate program and data spaces allow simultaneous access to program instructions and data, providing the high degree of parallelism. Two reads and one write operation can be performed in a single cycle. Instructions with parallel store and application-specific instructions can fully utilize this architecture. In addition, data can be transferred between data and program spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. In addition, the 'C54x, LC54x, and VC54x versions include the control mechanisms to manage interrupts, repeated operations, and function calls.

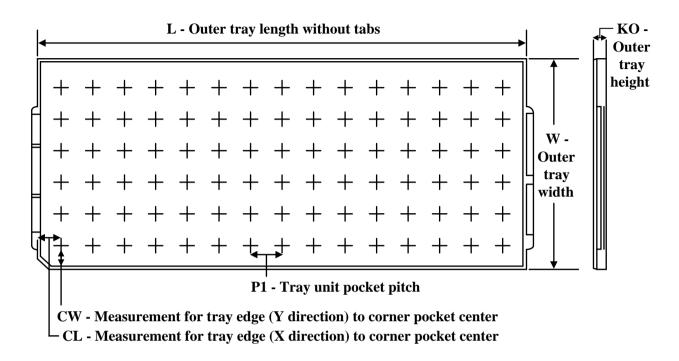

Table 1 provides an overview of the '54x generation of DSPs. The table shows significant features of each device including the capacity of on-chip RAM and ROM memories, the peripherals, the execution time of one machine cycle, and the type of package with its total pin count.

Table 1. Characteristics of the '54x Processors

| 202 7/25      | NOMINAL        | ON-C           |                  | PE             | RIPHERAL | _S  | CYCLE       |                           |

|---------------|----------------|----------------|------------------|----------------|----------|-----|-------------|---------------------------|

| DSP TYPE      | VOLTAGE (V)    | RAM†<br>(Word) | ROM<br>(Word)    | SERIAL<br>PORT | TIMER    | HPI | TIME (ns)   | PACKAGE TYPE              |

| TMS320C541    | 5.0            | 5K             | 28K <sup>‡</sup> | 2§             | 1        | No  | 25          | 100-pin TQFP              |

| TMS320LC541   | 3.3            | 5K             | 28K <sup>‡</sup> | 2§             | 1        | No  | 20/25       | 100-pin TQFP              |

| TMS320LC541B□ | 3.3            | 5K             | 28K‡             | 2§             | 1        | No  | 20/25       | 100-pin TQFP              |

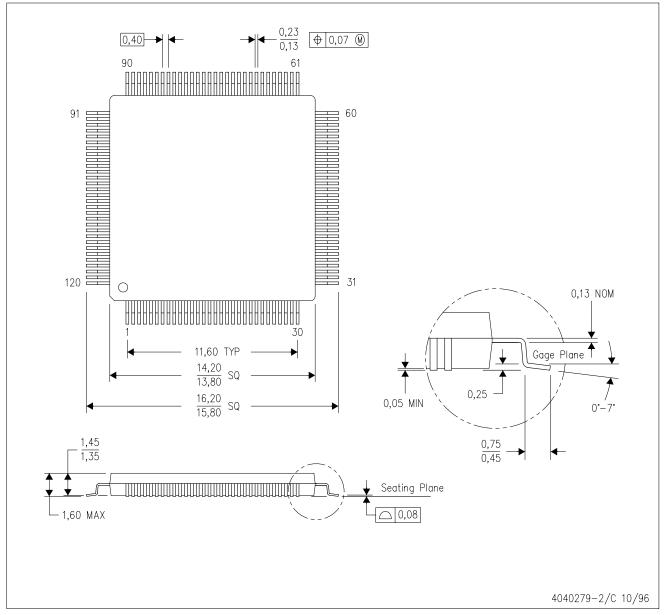

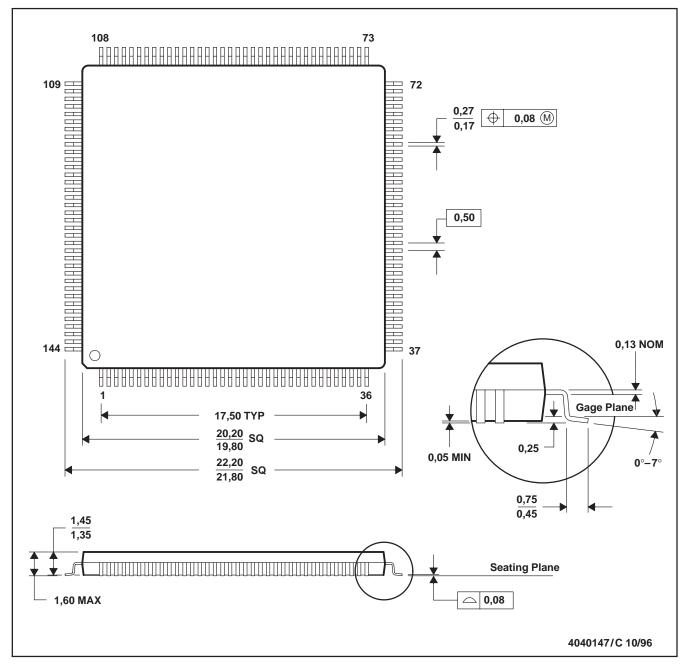

| TMS320C542    | 5.0            | 10K            | 2K               | 2¶             | 1        | Yes | 25          | 144-pin TQFP              |

| TMS320LC542   | 3.3            | 10K            | 2K               | 2¶             | 1        | Yes | 20/25       | 128-pin TQFP/144-pin TQFP |

| TMS320LC543   | 3.3            | 10K            | 2K               | 2¶             | 1        | No  | 20/25       | 100-pin TQFP              |

| TMS320LC545   | 3.3            | 6K             | 48K <sup>#</sup> | 2              | 1        | Yes | 20/25       | 128-pin TQFP              |

| TMS320LC545A□ | 3.3            | 6K             | 48K <sup>#</sup> | 2              | 1        | Yes | 15/20/25    | 128-pin TQFP              |

| TMS320LC545B□ | 3.3            | 6K             | 48K#             | 2              | 1        | Yes | 15/20/25    | 128-pin TQFP              |

| TMS320LC546   | 3.3            | 6K             | 48K#             | 2              | 1        | No  | 20/25       | 100-pin TQFP              |

| TMS320LC546A□ | 3.3            | 6K             | 48K#             | 2              | 1        | No  | 15/20/25    | 100-pin TQFP              |

| TMS320LC546B□ | 3.3            | 6K             | 48K#             | 2              | 1        | No  | 15/20/25    | 100-pin TQFP              |

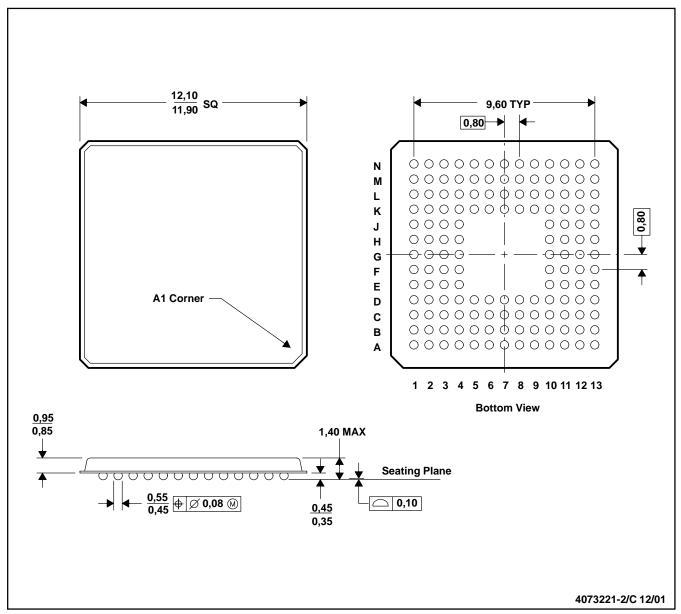

| TMS320LC548□  | 3.3            | 32K            | 2K               | 3☆             | 1        | Yes | 12.5/15/20  | 144-pin TQFP/144-pin BGA  |

| TMS320LC549□  | 3.3            | 32K            | 16K              | 3☆             | 1        | Yes | 12.5/15     | 144-pin TQFP/144-pin BGA  |

| TMS320VC549□  | 3.3 (2.5 core) | 32K            | 16K              | 3☆             | 1        | Yes | 8.3/10/12.5 | 144-pin TQFP/144-pin BGA  |

Legend:

TQFP = Thin Quad Flatpack

BGA = MicroStar BGA™ (Ball Grid Array)

- † The dual-access RAM (single access RAM on '548 and '549 devices) can be configured as data memory or program/data memory.

- For 'C541/'LC541, 8K words of ROM can be configured as program memory or program/data memory.

- § Two standard (general-purpose) serial ports

- ¶ One TDM and one BSP

- # For 'LC545/'LC546, 16K words of ROM can be configured as program memory or program/data memory.

- One standard and one BSP

- □ Refer to separate data sheet for electrical specifications.

MicroStar BGA is a trademark of Texas Instruments Incorporated.

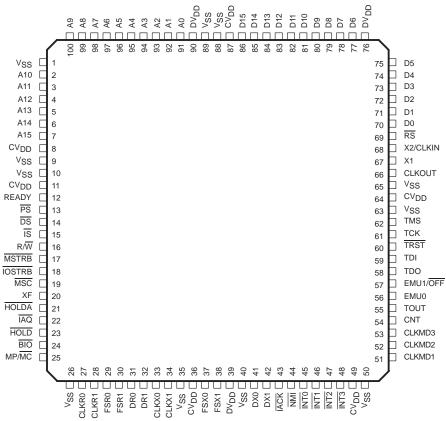

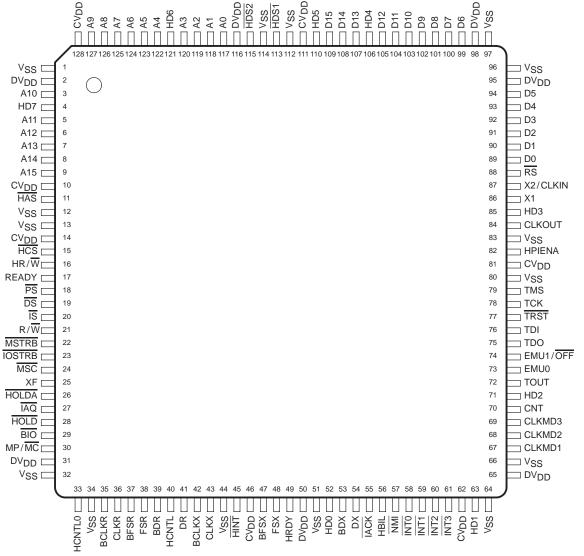

#### TMS320C541, TMS320LC541 PZ PACKAGE<sup>†</sup> (TOP VIEW)

<sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the TMS320C541PZ/TMS320LC541PZ (100-pin TQFP packages).

For the 'C541/'LC541 (100-pin packages), no letter in front of CLKRn, FSRn, DRn, CLKXn, FSXn, and DXn pin names denotes standard serial port (where n = 0 or 1 port).

#### TMS320C542/TMS320LC542 PGE PACKAGE<sup>†‡</sup> (TOP VIEW)

<sup>†</sup> NC = No connection

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the TMS320C542PGE/'LC542PGE (144-pin TQFP packages).

For the 'C542/'LC542 (144-pin TQFP packages), the letter B in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes buffered serial port (BSP). The letter T in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes time-division multiplexed (TDM) serial port.

<sup>&</sup>lt;sup>‡</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

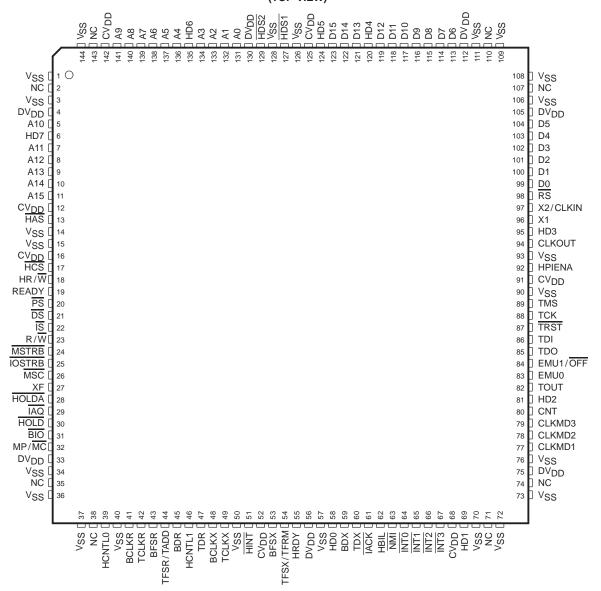

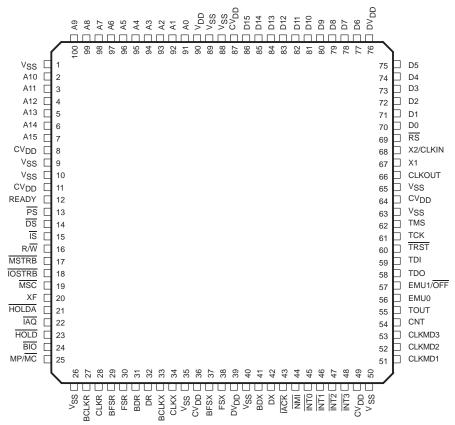

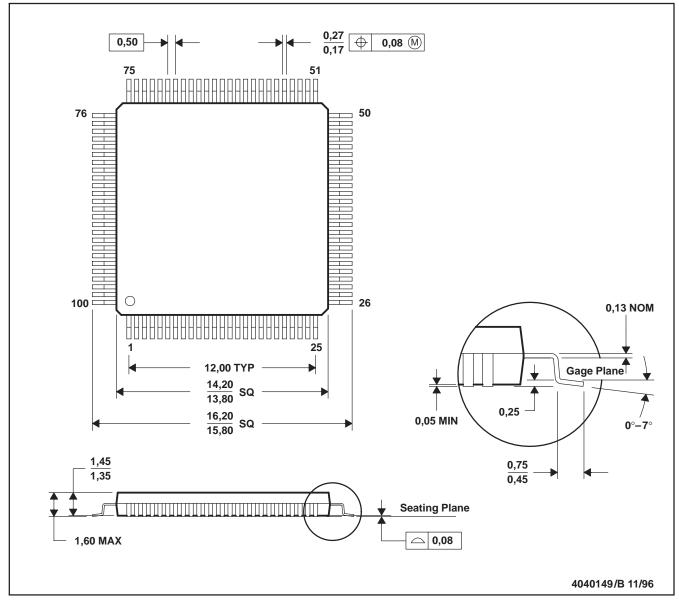

#### TMS320LC542 PBK PACKAGE<sup>†</sup> (TOP VIEW)

<sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the TMS320LC542PBK (128-pin TQFP package).

For the 'LC542 (128-pin TQFP package), the letter B in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes buffered serial port (BSP). The letter T in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes time-division multiplexed (TDM) serial port.

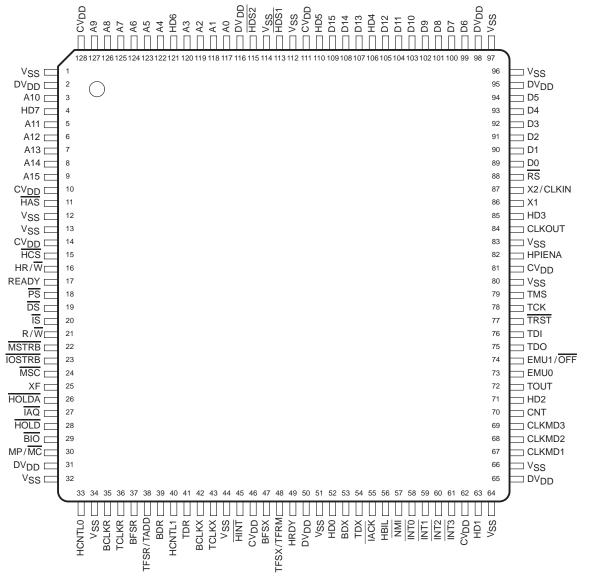

#### TMS320LC543 PZ PACKAGE<sup>†</sup> (TOP VIEW)

<sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the TMS320LC543PZ (100-pin TQFP package).

For the 'LC543 (100-pin TQFP package), the letter B in front of CLKR, FSR, DR, CLKX, FSX, and DX denotes buffered serial port (BSP). The letter T in front of CLKR, FSR, DR, CLKX, FSX, and DX denotes time-division multiplexed (TDM) serial port.

#### TMS320LC545 PBK PACKAGET (TOP VIEW)

<sup>&</sup>lt;sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the for the TMS320LC545PBK (128-pin TQFP package).

For the 'LC545 (128-pin TQFP package), the letter B in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes buffered serial port (BSP). No letter in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes standard serial port.

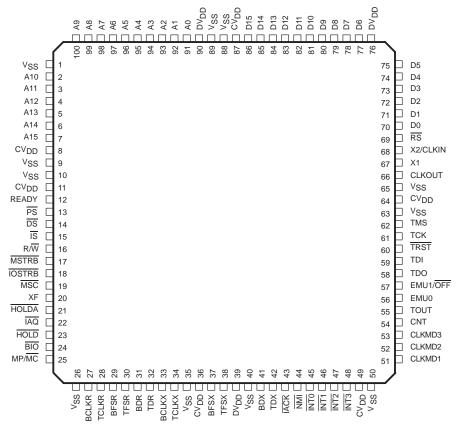

#### TMS320LC546 PZ PACKAGE<sup>†</sup> (TOP VIEW)

<sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the for the TMS320LC546PZ (100-pin TQFP package).

For the 'LC546 (100-pin TQFP package), the letter B in front of CLKR, FSR, DR, FSX, and DX denotes buffered serial port (BSP). No letter in front of CLKR, FSR, DR, FSX, and DX denotes standard serial port.

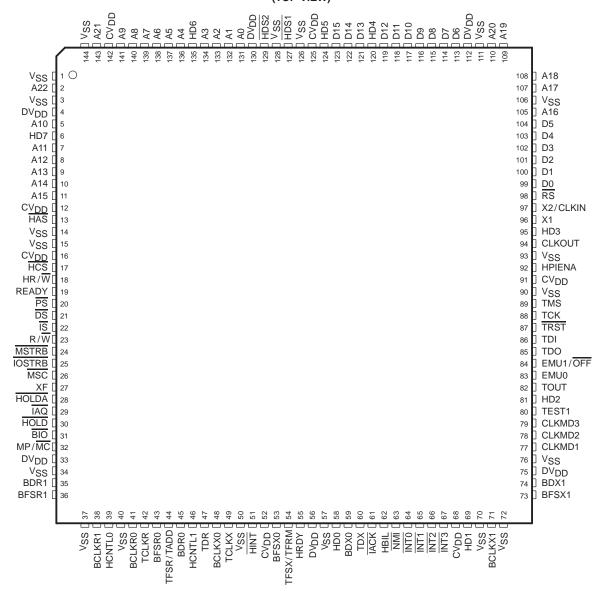

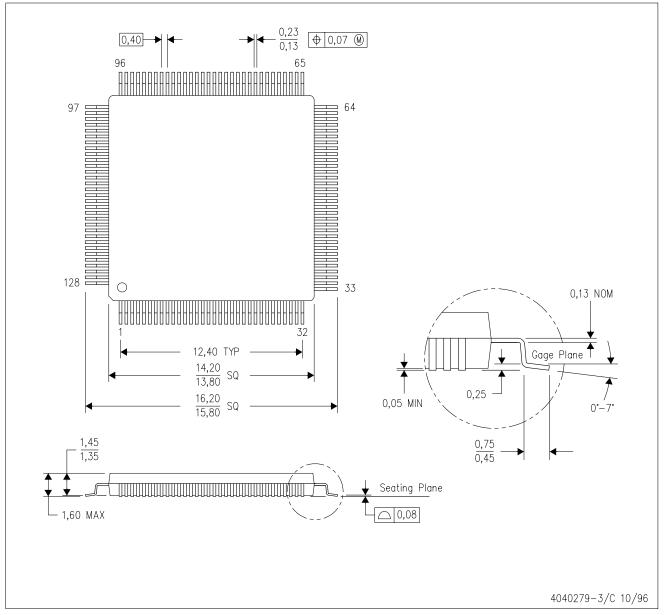

#### TMS320LC548, TMS320LC549, and TMS320VC549 PGE PACKAGE†‡ (TOP VIEW)

<sup>†</sup> NC = No connection

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the TMS320LC548PGE (144-pin TQFP package).

For the 'LC548, 'LC549 and 'VC549 (144-pin TQFP package), the letter B in front of CLKRn, FSRn, DRn, CLKXn, FSXn, and DXn pin names denotes buffered serial port (BSP), where n = 0 or 1 port. The letter T in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes time-division multiplexed (TDM) serial port.

<sup>&</sup>lt;sup>‡</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

#### TMS320LC548, TMS320LC549, TMS320VC549 GGU PACKAGE (BOTTOM VIEW)

| _ | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          |   |   |

|---|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---|---|

|   |            |            |            |            |            |            |            |            |            |            |            |            | `          | \ |   |

|   | $\bigcirc$ |   | Α |

|   | $\bigcirc$ |   | В |

|   | $\circ$    | $\bigcirc$ |   | С |

|   | $\bigcirc$ |   | D |

|   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |   | Е |

|   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |   | F |

|   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |   | G |

|   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |   | Н |

|   | $\circ$    | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |   | J |

|   | $\bigcirc$ |   | K |

|   | $\bigcirc$ |   | L |

|   | $\bigcirc$ |   | М |

|   | $\bigcirc$ |   | N |

| Ĺ |            |            |            |            |            |            |            |            |            |            |            |            |            |   |   |

The pin assignments table to follow lists each signal quadrant and BGA ball pin number for the TMS320LC548, TMS320LC549, and TMS320VC549 (144-pin BGA package).

The '54x signal descriptions table lists each terminal name, function, and operating mode(s) for the TMS320LC548GGU, TMS320LC549GGU, and TMS320VC549GGU.

## Pin Assignments for the TMS320LC548GGU, TMS320LC549GGU, and TMS320VC549GGU (144-Pin BGA Package)<sup>†</sup>

| SIGNAL<br>QUADRANT 1 | BGA BALL# | SIGNAL<br>QUADRANT 2 | BGA BALL# | SIGNAL<br>QUADRANT 3 | BGA BALL# | SIGNAL<br>QUADRANT 4 | BGA BALL# |

|----------------------|-----------|----------------------|-----------|----------------------|-----------|----------------------|-----------|

| Vss                  | A1        | BFSX1                | N13       | Vss                  | N1        | A19                  | A13       |

| A22                  | B1        | BDX1                 | M13       | BCLKR1               | N2        | A20                  | A12       |

| Vss                  | C2        | DV <sub>DD</sub>     | L12       | HCNTL0               | M3        | VSS                  | B11       |

| DV <sub>DD</sub>     | C1        | VSS                  | L13       | VSS                  | N3        | $DV_DD$              | A11       |

| A10                  | D4        | CLKMD1               | K10       | BCLKR0               | K4        | D6                   | D10       |

| HD7                  | D3        | CLKMD2               | K11       | TCLKR                | L4        | D7                   | C10       |

| A11                  | D2        | CLKMD3               | K12       | BFSR0                | M4        | D8                   | B10       |

| A12                  | D1        | TEST1                | K13       | TFSR/TADD            | N4        | D9                   | A10       |

| A13                  | E4        | HD2                  | J10       | BDR0                 | K5        | D10                  | D9        |

| A14                  | E3        | TOUT                 | J11       | HCNTL1               | L5        | D11                  | C9        |

| A15                  | E2        | EMU0                 | J12       | TDR                  | M5        | D12                  | В9        |

| CV <sub>DD</sub>     | E1        | EMU1/OFF             | J13       | BCLKX0               | N5        | HD4                  | A9        |

| HAS                  | F4        | TDO                  | H10       | TCLKX                | K6        | D13                  | D8        |

| Vss                  | F3        | TDI                  | H11       | VSS                  | L6        | D14                  | C8        |

| V <sub>SS</sub>      | F2        | TRST                 | H12       | HINT                 | M6        | D15                  | B8        |

| CV <sub>DD</sub>     | F1        | TCK                  | H13       | CVDD                 | N6        | HD5                  | A8        |

| HCS                  | G2        | TMS                  | G12       | BFSX0                | M7        | CV <sub>DD</sub>     | В7        |

| HR/W                 | G1        | V <sub>SS</sub>      | G13       | TFSX/TFRM            | N7        | V <sub>SS</sub>      | A7        |

| READY                | G3        | CV <sub>DD</sub>     | G11       | HRDY                 | L7        | HDS1                 | C7        |

| PS                   | G4        | HPIENA               | G10       | DV <sub>DD</sub>     | K7        | Vss                  | D7        |

| DS                   | H1        | V <sub>SS</sub>      | F13       | V <sub>SS</sub>      | N8        | HDS2                 | A6        |

| ĪS                   | H2        | CLKOUT               | F12       | HD0                  | M8        | $DV_DD$              | B6        |

| R/W                  | H3        | HD3                  | F11       | BDX0                 | L8        | A0                   | C6        |

| MSTRB                | H4        | X1                   | F10       | TDX                  | K8        | A1                   | D6        |

| IOSTRB               | J1        | X2/CLKIN             | E13       | ĪACK                 | N9        | A2                   | A5        |

| MSC                  | J2        | RS                   | E12       | HBIL                 | M9        | A3                   | B5        |

| XF                   | J3        | D0                   | E11       | NMI                  | L9        | HD6                  | C5        |

| HOLDA                | J4        | D1                   | E10       | ĪNT0                 | K9        | A4                   | D5        |

| ĪĀQ                  | K1        | D2                   | D13       | ĪNT1                 | N10       | A5                   | A4        |

| HOLD                 | K2        | D3                   | D12       | ĪNT2                 | M10       | A6                   | B4        |

| BIO                  | K3        | D4                   | D11       | ĪNT3                 | L10       | A7                   | C4        |

| MP/MC                | L1        | D5                   | C13       | CV <sub>DD</sub>     | N11       | A8                   | А3        |

| DV <sub>DD</sub>     | L2        | A16                  | C12       | HD1                  | M11       | A9                   | B3        |

| V <sub>SS</sub>      | L3        | V <sub>SS</sub>      | C11       | V <sub>SS</sub>      | L11       | CV <sub>DD</sub>     | C3        |

| BDR1                 | M1        | A17                  | B13       | BCLKX1               | N12       | A21                  | A2        |

| BFSR1                | M2        | A18                  | B12       | V <sub>SS</sub>      | M12       | V <sub>SS</sub>      | B2        |

<sup>†</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

## '54x Signal Descriptions

| TERMINAL                                                                                                                                            |       |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N.                                                                                                                                                  | AME   | TYPET |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                     |       |       | DATA SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | (MSB) | O/Z   | Parallel port address bus A22 (MSB) through A0 (LSB). The sixteen LSBs (A15–A0) are multiplexed to address external data/program memory or I/O. A15–A0 are placed in the high-impedance state in the hold mode. A15–A0 also go into the high-impedance state when EMU1/OFF is low. The seven MSBs (A22 to A16) are used for extended program memory addressing ('548 and '549 only).  On the '548 and '549 devices, the address bus have a feature called bus holder that eliminates passive components and the power dissipation associated with it. The bus holders keep the address bus at the previous logic level when the bus goes into a high-impedance state. The bus holders on the address bus are always enabled. |

| D15<br>D14<br>D13<br>D12<br>D11<br>D10<br>D9<br>D8<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                                  | (MSB) | I/O/Z | Parallel port data bus D15 (MSB) through D0 (LSB). D15–D0 are multiplexed to transfer data between the core CPU and external data/program memory or I/O devices. D15–D0 are placed in the high-impedance state when not output or when RS or HOLD is asserted. D15–D0 also go into the high-impedance state when EMU1/OFF is low.  The data bus has a feature called bus holder that eliminates passive components and the power dissipation associated with it. The bus holders keep the data bus at the previous logic level when the bus goes into a high-impedance state. These bus holders are enabled or disabled by the BH bit in the bank switching control register (BSCR).                                         |

|                                                                                                                                                     | . ,   |       | INITIALIZATION, INTERRUPT AND RESET OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

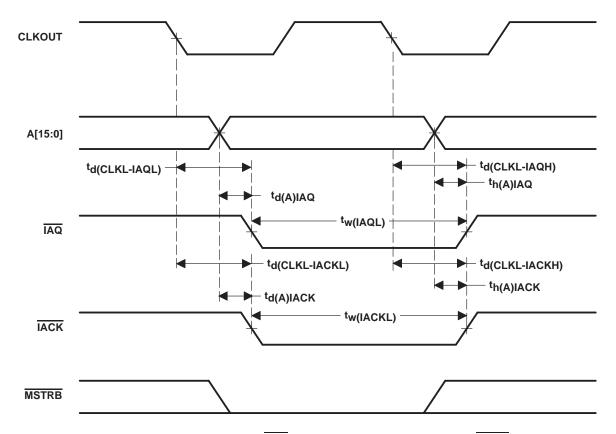

| ĪACK                                                                                                                                                |       | O/Z   | Interrupt acknowledge signal. IACK indicates the receipt of an interrupt and that the program counter is fetching the interrupt vector location designated by A15–0. IACK also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

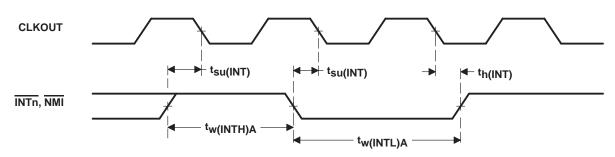

| INTO<br>INT1<br>INT2<br>INT3                                                                                                                        |       | I     | External user interrupt inputs. INT0-INT3 are prioritized and are maskable by the interrupt mask register and the interrupt mode bit. INT0 -INT3 can be polled and reset by the interrupt flag register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

$<sup>\</sup>dagger$  I = Input, O = Output, Z = High impedance

| TERMINAL<br>NAME TYPET |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IVANIL                 | 111121 | INITIALIZATION, INTERRUPT AND RESET OPERATIONS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                          |

| NMI                    | 1      | Nonmaskable interrupt. NMI is an external interrupt that cannot be masked by way of the INTM or the IMR. When NMI is activated, the processor traps to the appropriate vector location.                                                                                                                                                                                                                                             |

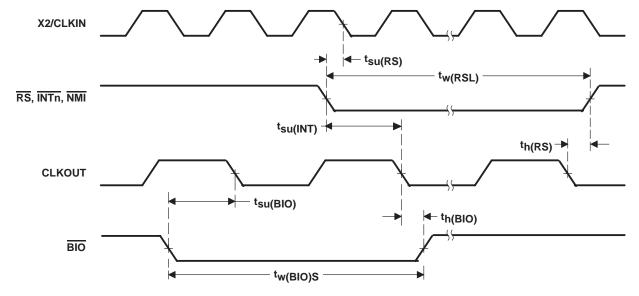

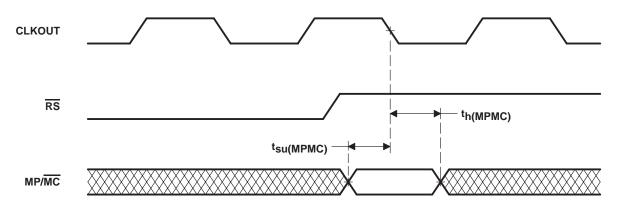

| RS                     | I      | Reset input. $\overline{\text{RS}}$ causes the DSP to terminate execution and forces the program counter to 0FF80h. When $\overline{\text{RS}}$ is brought to a high level, execution begins at location 0FF80h of the program memory. $\overline{\text{RS}}$ affects various registers and status bits.                                                                                                                            |

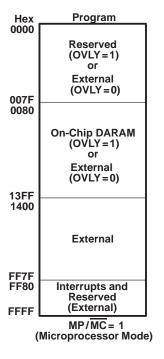

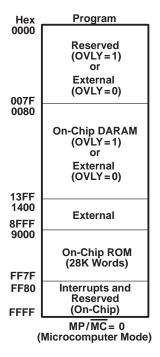

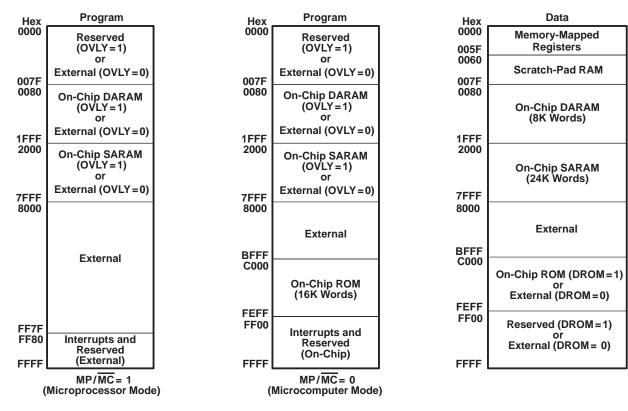

| MP/MC                  | I      | Microprocessor/microcomputer mode-select pin. If active-low at reset (microcomputer mode), MP/MC causes the internal program ROM to be mapped into the upper program memory space. In the microprocessor mode, off-chip memory and its corresponding addresses (instead of internal program ROM) are accessed by the DSP.                                                                                                           |

| CNT                    | I      | I/O level select. For 5-V operation, all input and output voltage levels are TTL-compatible when CNT is pulled down to a low level. For 3-V operation with CMOS-compatible I/O interface levels, CNT is pulled to a high level.                                                                                                                                                                                                     |

|                        |        | MULTIPROCESSING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                             |

| BIO                    | I      | Branch control input. A branch can be conditionally executed when $\overline{\text{BIO}}$ is active. If low, the processor executes the conditional instruction. The $\overline{\text{BIO}}$ condition is sampled during the decode phase of the pipeline for the XC instruction, and all other instructions sample $\overline{\text{BIO}}$ during the read phase of the pipeline.                                                  |

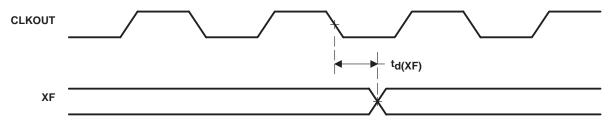

| XF                     | O/Z    | External flag output (latched software-programmable signal). XF is set high by the SSBX XF instruction, set low by RSBX XF instruction or by loading the ST1 status register. XF is used for signaling other processors in multiprocessor configurations or as a general-purpose output pin. XF goes into the high-impedance state when OFF is low, and is set high at reset.                                                       |

|                        |        | MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                              |

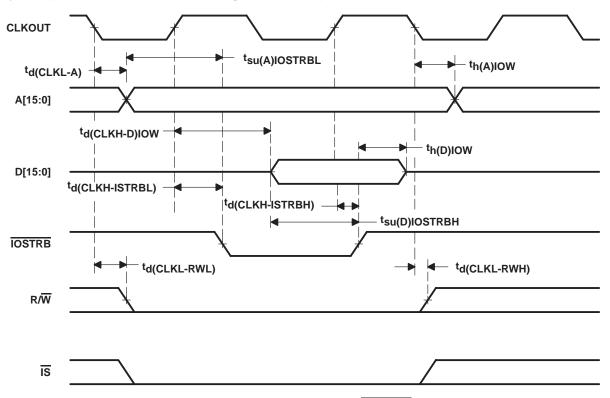

| DS<br>PS<br>IS         | O/Z    | Data, program, and I/O space select signals. $\overline{DS}$ , $\overline{PS}$ , and $\overline{IS}$ are always high unless driven low for communicating to a particular external space. Active period corresponds to valid address information. Placed into a high-impedance state in hold mode. $\overline{DS}$ , $\overline{PS}$ , and $\overline{IS}$ also go into the high-impedance state when EMU1/ $\overline{OFF}$ is low. |

| MSTRB                  | O/Z    | Memory strobe signal. MSTRB is always high unless low-level asserted to indicate an external bus access to data or program memory. Placed in high-impedance state in hold mode. MSTRB also goes into the high-impedance state when OFF is low.                                                                                                                                                                                      |

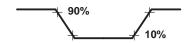

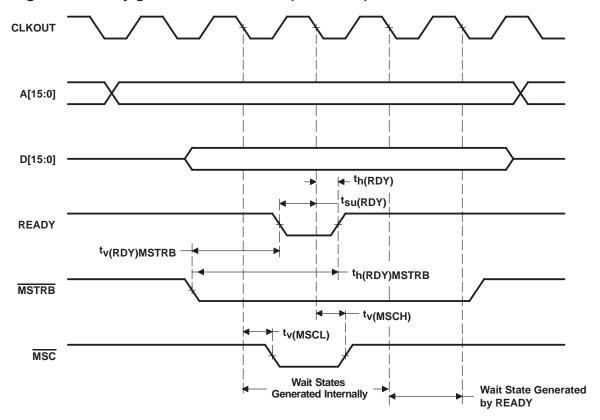

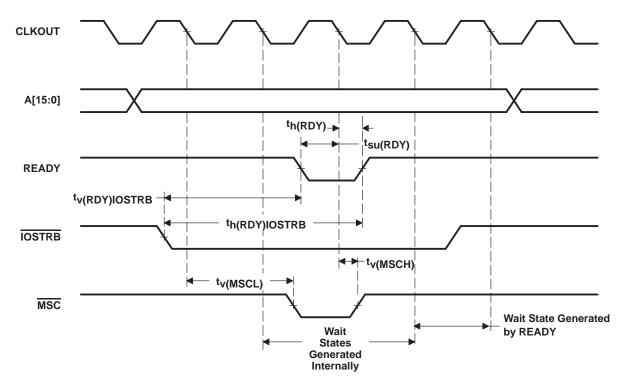

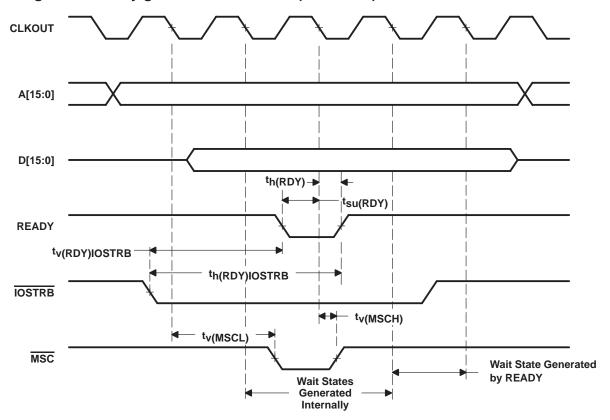

| READY                  | ſ      | Data-ready input. READY indicates that an external device is prepared for a bus transaction to be completed. If the device is not ready (READY is low), the processor waits one cycle and checks READY again. Note that the processor performs ready-detection if at least two software wait states are programmed. The READY signal is not sampled until the completion of the software wait states.                               |

| R/W                    | O/Z    | Read/write signal. R/\overline{W} indicates transfer direction during communication to an external device and is normally high (in read mode), unless asserted low when the DSP performs a write operation. Placed in the high-impedance state in hold mode, R/\overline{W} also goes into the high-impedance state when EMU1/OFF is low.                                                                                           |

| IOSTRB                 | O/Z    | I/O strobe signal. IOSTRB is always high unless low level asserted to indicate an external bus access to an I/O device. Placed in high-impedance state in hold mode. IOSTRB also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                           |

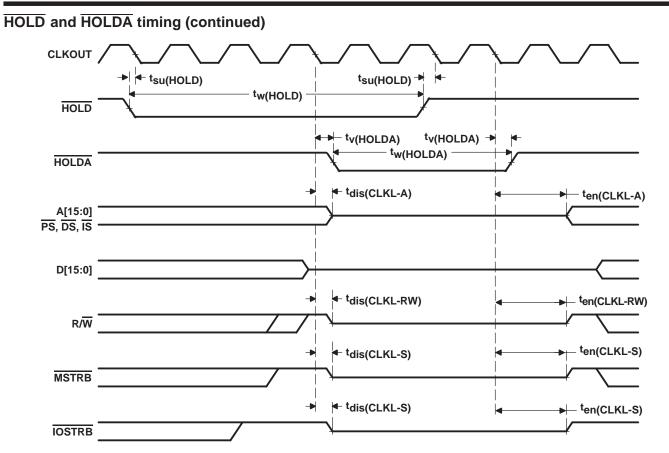

| HOLD                   | I      | Hold input. HOLD is asserted to request control of the address, data, and control lines. When acknowledged by the '54x, these lines go into high-impedance state.                                                                                                                                                                                                                                                                   |

| HOLDA                  | O/Z    | Hold acknowledge signal. HOLDA indicates to the external circuitry that the processor is in a hold state and that the address, data, and control lines are in a high-impedance state, allowing them to be available to the external circuitry. HOLDA also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                  |

| MSC                    | O/Z    | Microstate complete signal. Goes low on CLKOUT falling at the start of the first software wait state. Remains low until one CLKOUT cycle before the last programmed software wait state. If connected to the READY line, MSC forces one external wait state after the last internal wait state has been completed. MSC also goes into the high-impedance state when EM1/OFF is low.                                                 |

<sup>†</sup> I = Input, O = Output, Z = High impedance

| TERM                       | INAL                     | DECORIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|----------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| NAME                       | TYPET                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                            |                          | MEMORY CONTROL SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| ĪĀQ                        | O/Z                      | Instruction acquisition signal. $\overline{IAQ}$ is asserted (active low) when there is an instruction address on the address bus and goes into the high-impedance state when EMU1/ $\overline{OFF}$ is low.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|                            | OSCILLATOR/TIMER SIGNALS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

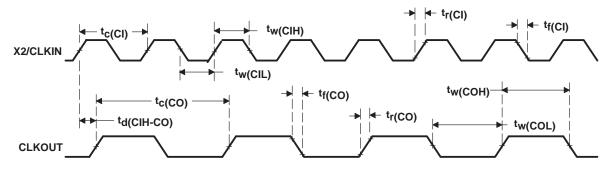

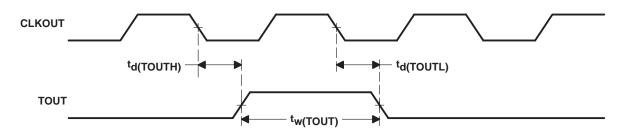

| CLKOUT                     | O/Z                      | Master clock output signal. CLKOUT cycles at the machine-cycle rate of the CPU. The internal machine cycle is bounded by the falling edges of this signal. CLKOUT also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| CLKMD1<br>CLKMD2<br>CLKMD3 | I                        | Clock mode external/internal input signals. CLKMD1, CLKMD2, and CLKMD3 allow you to select and configure different clock modes, such as crystal, external clock, and various PLL factors. Refer to PLL section for a detailed functional description of these pins.                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

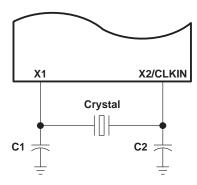

| X2/CLKIN                   | I                        | Input pin to internal oscillator from the crystal. If the internal (crystal) oscillator is not being used, a clock can become input to the device using this pin. The internal machine cycle time is determined by the clock operating-mode pins (CLKMD1, CLKMD2 and CLKMD3).                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| X1                         | 0                        | Output pin from the internal oscillator for the crystal. If the internal oscillator is not used, X1 should be left unconnected. X1 does not go into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| TOUT                       | O/Z                      | Timer output. TOUT signals a pulse when the on-chip timer counts down past zero. The pulse is a CLKOUT-cycle wide. TOUT also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|                            |                          | BUFFERED SERIAL PORT 0 AND BUFFERED SERIAL PORT 1 SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

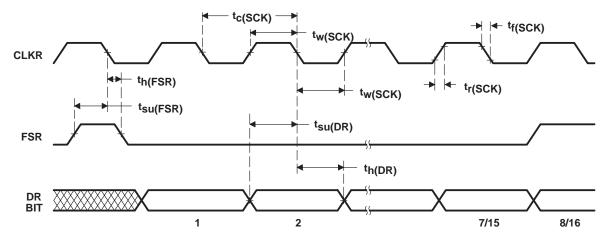

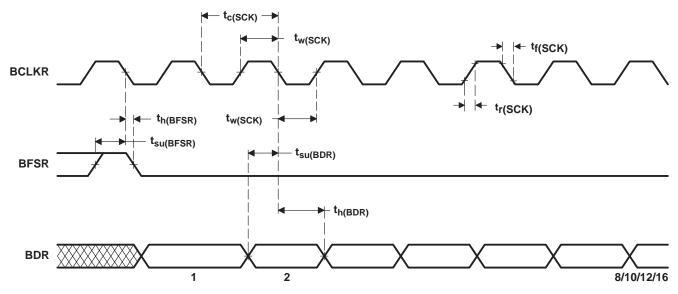

| BCLKR0<br>BCLKR1           | I                        | Receive clocks. External clock signal for clocking data from the data-receive (DR) pin into the buffered serial port receive shift registers (RSRs). Must be present during buffered serial port transfers. If the buffered serial port is not being used, BCLKR0 and BCLKR1 can be sampled as an input by way of IN0 bit of the SPC register.                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

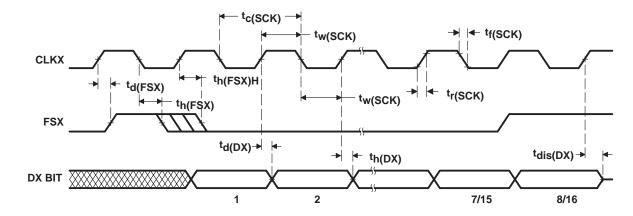

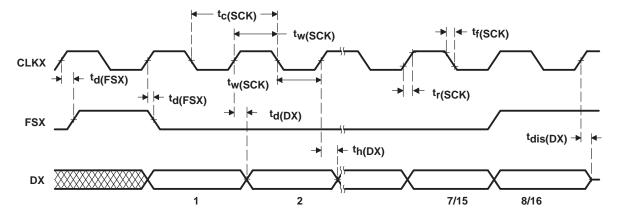

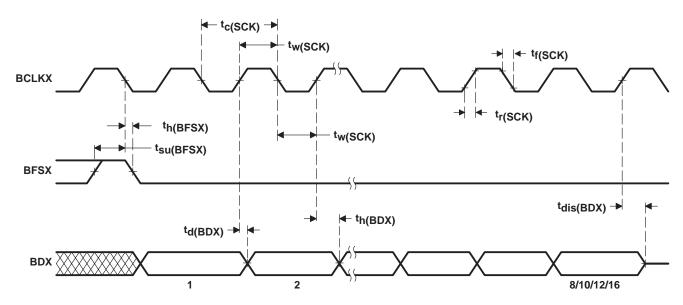

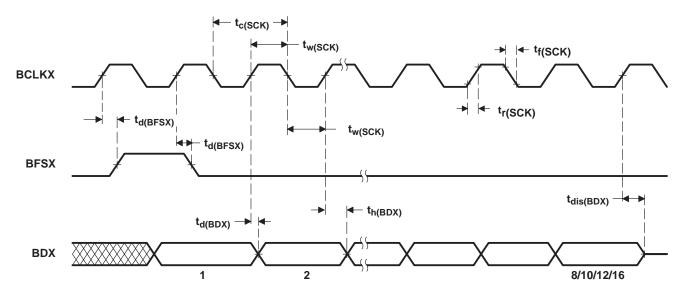

| BCLKX0<br>BCLKX1           | I/O/Z                    | Transmit clock. Clock signal for clocking data from the serial port transmit shift register (XSR) to the data transmit (DX) pin. BCLKX can be an input if MCM in the serial port control register is cleared to 0. It also can be driven by the device at 1/(CLKDV + 1) where CLKDV range is 0–31 CLKOUT frequency when MCM is set to 1. If the buffered serial port is not used, BCLKX can be sampled as an input by way of IN1 of the SPC register. BCLKX0 and BCLKX1 go into the high-impedance state when OFF is low. |  |  |  |  |  |  |  |  |  |

| BDR0<br>BDR1               | I                        | Buffered serial-data-receive input. Serial data is received in the RSR by BDR0/BDR1.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| BDX0<br>BDX1               | O/Z                      | Buffered serial-port-transmit output. Serial data is transmitted from the XSR by way of BDX. BDX0 and BDX1 are placed in the high-impedance state when not transmitting and when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| BFSR0<br>BFSR1             | I                        | Frame synchronization pulse for receive input. The falling edge of the BFSR pulse initiates the data-receive process, beginning the clocking of the RSR.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| BFSX0<br>BFSX1             | I/O/Z                    | Frame synchronization pulse for transmit input/output. The falling edge of the BFSX pulse initiates the data-transmit process, beginning the clocking of the XSR. Following reset, the default operating condition of BFSX is an input. BFSX0 and BFSX1 can be selected by software to be an output when TXM in the serial control register is set to 1. This pin goes into the high-impedance state when EMU1/OFF is low.                                                                                                |  |  |  |  |  |  |  |  |  |

|                            |                          | SERIAL PORT 0 AND SERIAL PORT 1 SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| CLKR0<br>CLKR1             | I                        | Receive clocks. External clock signal for clocking data from the data receive (DR) pin into the serial port receive shift register (RSR). Must be present during serial port transfers. If the serial port is not being used, CLKR0 and CLKR1 can be sampled as an input via IN0 bit of the SPC register.                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| CLKX0<br>CLKX1             | I/O/Z                    | Transmit clock. Clock signal for clocking data from the serial port transmit shift register (XSR) to the data transmit (DX) pin. CLKX can be an input if MCM in the serial port control register is cleared to 0. It also can be driven by the device at 1/4 CLKOUT frequency when MCM is set to 1. If the serial port is not used, CLKX can be sampled as an input via IN1 of the SPC register. CLKX0 and CLKX1 go into the high-impedance state when EMU1/OFF is low.                                                   |  |  |  |  |  |  |  |  |  |

| DR0<br>DR1                 | I                        | Serial-data-receive input. Serial data is received in the RSR by DR.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

$<sup>\</sup>dagger$  I = Input, O = Output, Z = High impedance

| TERMINAL<br>NAME TYPE <sup>†</sup> |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                    |        | SERIAL PORT 0 AND SERIAL PORT 1 SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| DX0<br>DX1                         | O/Z    | Serial port transmit output. Serial data is transmitted from the XSR via DX. DX0 and DX1 are placed in the high-impedance state when not transmitting and when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| FSR0<br>FSR1                       | I      | rame synchronization pulse for receive input. The falling edge of the FSR pulse initiates the data-receirocess, beginning the clocking of the RSR.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| FSX0<br>FSX1                       | I/O/Z  | Frame synchronization pulse for transmit input/output. The falling edge of the FSX pulse initiates the data transmit process, beginning the clocking of the XSR. Following reset, the default operating condition of FSX is an input. FSX0 and FSX1 can be selected by software to be an output when TXM in the serial control register is set to 1. This pin goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                 |  |  |  |

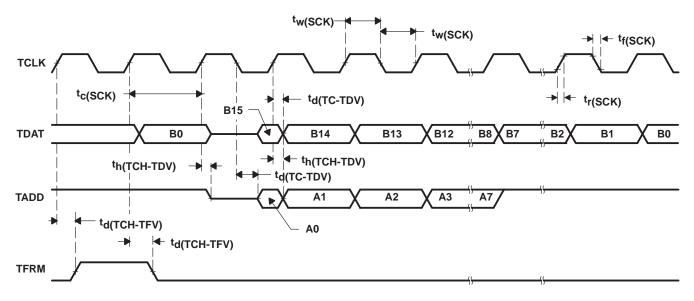

|                                    |        | TDM SERIAL PORT SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

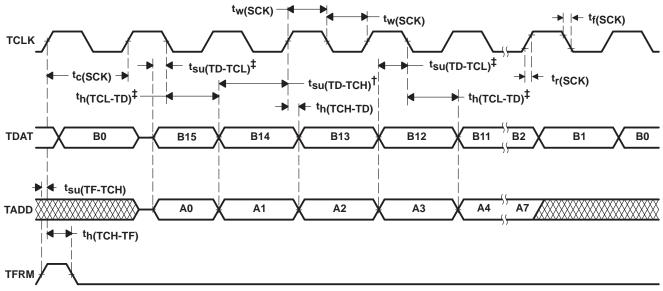

| TCLKR                              | I      | TDM receive clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TDR                                | I      | TDM serial data-receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TFSR/TADD                          | I/O    | TDM receive frame synchronization or TDM address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| TCLKX                              | I/O/Z  | TDM transmit clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TDX                                | O/Z    | TDM serial data-transmit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| TFSX/TFRM                          | I/O/Z  | TDM transmit frame synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

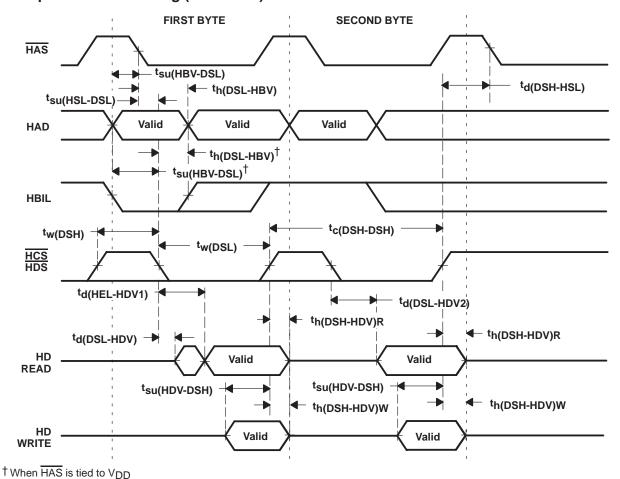

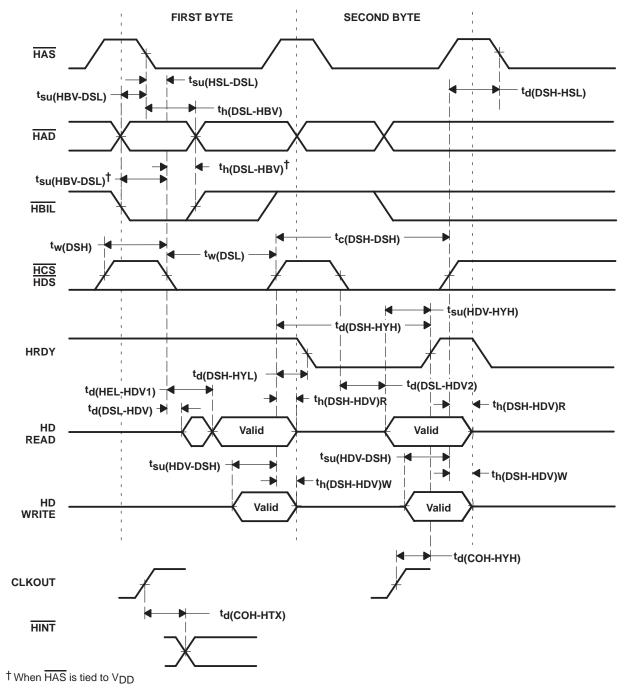

|                                    |        | HOST-PORT INTERFACE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| HD0-HD7                            | I/O/Z  | Parallel bidirectional data bus. HD0–HD7 are placed in the high-impedance state when not outputting data. The signals go into the high-impedance state when EMU1/OFF is low. These pins each have bus holders similar to those on the address/data bus, but which are always enabled.                                                                                                                                                                                                                                                                  |  |  |  |

| HCNTL0<br>HCNTL1                   | I      | Control inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| HBIL                               | I      | Byte-identification input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

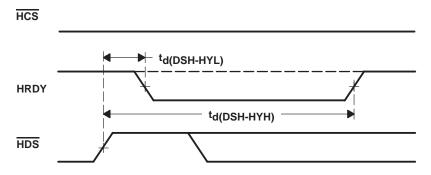

| HCS                                | I      | Chip-select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| HDS1<br>HDS2                       | I      | Data strobe inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| HAS                                | I      | Address strobe input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| HR/W                               | 1      | Read/write input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| HRDY                               | O/Z    | Ready output. This signal goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| HINT                               | O/Z    | Interrupt output. When the DSP is in reset, this signal is driven high. The signal goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| HPIENA                             | I      | HPI module select input. This signal must be tied to a logic 1 state to have HPI selected. If this input is left open or connected to ground, the HPI module will not be selected, internal pullup for the HPI input pins are enabled, and the HPI data bus has keepers set. This input is provided with an internal pull-down resistor which is active only when RS is low. HPIENA is sampled when RS goes high and ignored until RS goes low again. Refer to the Electrical Characteristics section for the input current requirements for this pin. |  |  |  |

|                                    |        | SUPPLY PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| $CV_{DD}$                          | Supply | +V <sub>DD</sub> . CV <sub>DD</sub> is the dedicated power supply for the core CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| $DV_DD$                            | Supply | +V <sub>DD</sub> . DV <sub>DD</sub> is the dedicated power supply for I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| V <sub>SS</sub>                    | Supply | Ground. VSS is the dedicated power ground for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High impedance

| TERMINAL<br>NAME TYPET |                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                        | IEEE1149.1 TEST PINS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| тск                    | I                    | IEEE standard 1149.1 test clock. Pin with internal pullup device. This is normally a free-running clock signal with a 50% duty cycle. The changes on the test-access port (TAP) of input signals TMS and TDI are clocked into the TAP controller, instruction register, or selected test data register on the rising edge of TCK. Changes at the TAP output signal (TDO) occur on the falling edge of TCK.                                                                                                                                                                                    |  |  |  |  |  |  |  |

| TDI                    | I                    | IEEE standard 1149.1 test data input. Pin with internal pullup device. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| TDO                    | O/Z                  | IEEE standard 1149.1 test data output. The contents of the selected register (instruction or data) is shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state except when the scanning of data is in progress. TDO also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| TMS                    | I                    | IEEE standard 1149.1 test mode select. Pin with internal pullup device. This serial control input is clocked into the TAP controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| TRST                   | I                    | IEEE standard 1149.1 test reset. TRST, when high, gives the IEEE standard 1149.1 scan system control of the operations of the device. If TRST is not connected or driven low, the device operates in its functional mode, and the IEEE standard 1149.1 signals are ignored. Pin with internal pulldown device.                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| EMU0                   | I/O/Z                | Emulator interrupt 0 pin. When TRST is driven low, EMU0 must be high for the activation of the EMU1/OFF condition. When TRST is driven high, EMU0 is used as an interrupt to or from the emulator system and is defined as input/output by way of IEEE standard 1149.1 scan system.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| EMU1/OFF               | I/O/Z                | Emulator interrupt 1 pin/disable all outputs. When TRST is driven high, EMU1/OFF is used as an interrupt to or from the emulator system and is defined as input/output by way of IEEE standard 1149.1 scan system. When TRST is driven low, EMU1/OFF is configured as OFF. The EMU1/OFF signal, when active low, puts all output drivers into the high-impedance state. Note that OFF is used exclusively for testing and emulation purposes (not for multiprocessing applications). Therefore, for the OFF condition, the following conditions apply: TRST = low, EMU0 = high EMU1/OFF = low |  |  |  |  |  |  |  |

|                        |                      | DEVICE TEST PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| TEST1                  | I                    | Test1 – Reserved for internal use only ('LC548, 'LC549, and 'VC549 only). <b>This pin must not be connected (NC).</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

$<sup>\</sup>dagger$  I = Input, O = Output, Z = High impedance

#### architecture

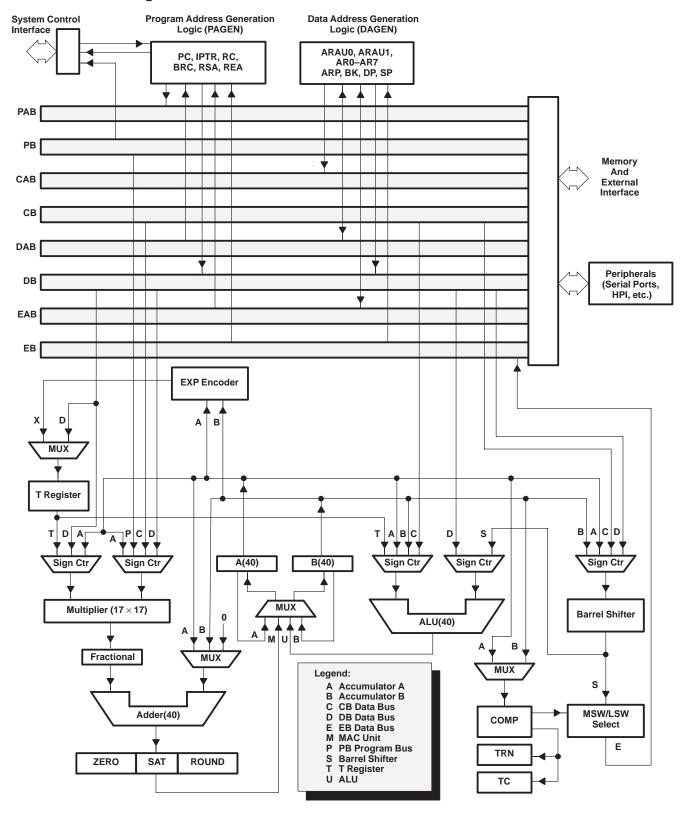

The '54x DSPs use an advanced, modified Harvard architecture that maximizes processing power by maintaining three separate bus structures for data memory and one for program memory. Separate program and data spaces allow simultaneous access to program instructions and data, providing a high degree of parallelism. For example, two read and one write operations can be performed in a single cycle. Instructions with parallel store and application-specific instructions fully utilize this architecture. In addition, data can be transferred between data and program spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. In addition, the '54x include the control mechanisms to manage interrupts, repeated operations, and function calls.

The functional block diagram includes the principal blocks and bus structure in the '54x devices.

## functional block diagram of the '54x internal hardware

SPRS039C - FEBRUARY 1996 - REVISED DECEMBER 1999

## central processing unit (CPU)

The CPU of the '54x devices contains:

- A 40-bit arithmetic logic unit (ALU)

- Two 40-bit accumulators

- A barrel shifter

- A 17 × 17-bit multiplier/adder

- A compare, select and store unit (CSSU)

## arithmetic logic unit (ALU)

The '54x devices perform 2s-complement arithmetic using: a 40-bit arithmetic logic unit (ALU) and two 40-bit accumulators (ACCA and ACCB). The ALU also can perform Boolean operations.

The ALU can function as two 16-bit ALUs and perform two 16-bit operations simultaneously when the C16 bit in status register 1 (ST1) is set.

#### accumulators

The accumulators, ACCA and ACCB, store the output from the ALU or the multiplier / adder block; the accumulators can also provide a second input to the ALU or the multiplier / adder. The accumulators are divided into three parts:

- Guard bits (bits 32–39)

- A high-order word (bits 16–31)

- A low-order word (bits 0–15)

Instructions are provided for storing the guard bits, the high- and the low-order accumulator words in data memory, and for manipulating 32-bit accumulator words in or out of data memory. Also, any of the accumulators can be used as temporary storage for the other.

#### barrel shifter

The '54x's barrel shifter has a 40-bit input connected to the accumulator, or data memory (CB, DB) and a 40-bit output connected to the ALU, or data memory (EB). The barrel shifter produces a left shift of 0 to 31 bits and a right shift of 0 to 16 bits on the input data. The shift requirements are defined in the shift-count field (ASM) of ST1 or defined in the temporary register (TREG), which is designated as a shift-count register. This shifter and the exponent detector normalize the values in an accumulator in a single cycle. The least significant bits (LSBs) of the output are filled with 0s and the most significant bits (MSBs) can be either zero-filled or sign-extended, depending on the state of the sign-extended mode bit (SXM) of ST1. Additional shift capabilities enable the processor to perform numerical scaling, bit extraction, extended arithmetic, and overflow prevention operations.

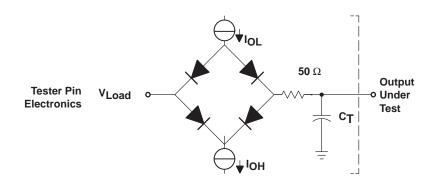

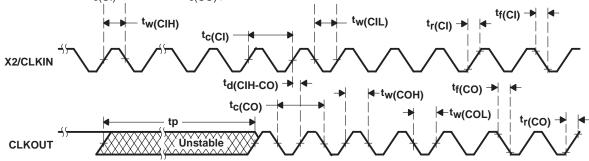

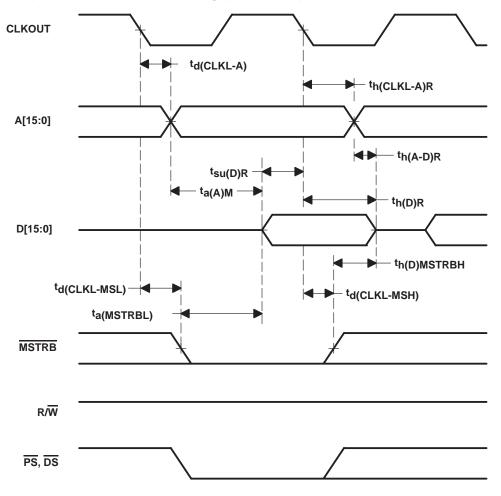

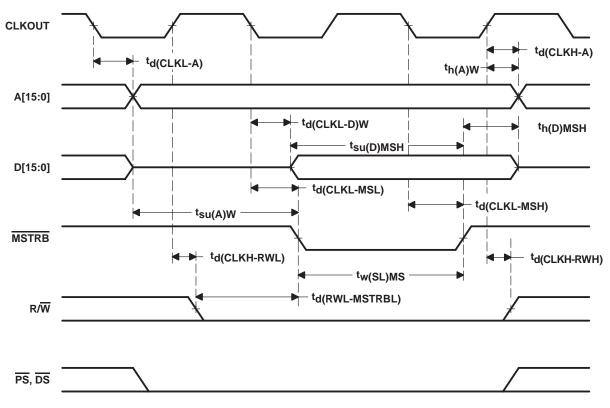

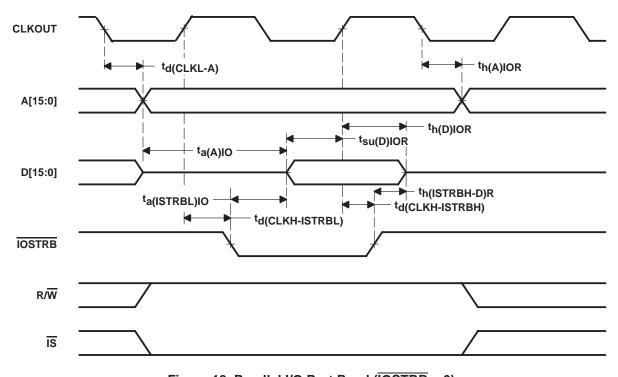

#### multiplier/adder