SPRS976E - NOVEMBER 2016-REVISED MAY 2018

**DM505**

# **DM505 SoC for Vision Analytics** 15mm Package (ABF) Silicon Revision 2.0

#### **Device Overview**

#### **Features**

- Architecture Designed for Vision Analytics **Applications**

- Video and Image Processing Support

- Full-HD Video (1920 x 1080p, 60 fps)

- Video Input and Video Output

- Up to 2 C66x Floating-Point VLIW DSP

- Fully Object-Code Compatible With C67x and C64x+

- Up to Thirty-two 16 x 16-Bit Fixed-Point Multiplies per Cycle

- Up to 512kB of On-Chip L3 RAM

- Level 3 (L3) and Level 4 (L4) Interconnects

- Memory Interface (EMIF) Module

- Supports DDR3/DDR3L up to DDR-1066

- Supports DDR2 up to DDR-800

- Supports LPDDR2 up to DDR-667

- Up to 2GB Supported

- Dual Arm<sup>®</sup> Cortex<sup>®</sup>-M4 Image Processor (IPU)

- Vision AccelerationPac

- Embedded Vision Engine (EVE)

- Display Subsystem

- Display Controller With DMA Engine

- CVIDEO / SD-DAC TV Analog Composite Output

- Video Input Port (VIP) Module

- Support for up to 4 Multiplexed Input Ports

- On-chip Temperature Sensor That is Capable of **Generating Temperature Alerts**

- General-Purpose Memory Controller (GPMC)

- Enhanced Direct Memory Access (EDMA) Controller

- 3-Port (2 External) Gigabit Ethernet (GMAC) Switch

- Controller Area Network (DCAN) Module

- CAN 2.0B Protocol

- Modular Controller Area Network (MCAN) Module

- CAN 2.0B Protocol

- Eight 32-Bit General-Purpose Timers

- Three Configurable UART Modules

- Four Multichannel Serial Peripheral Interfaces (McSPI)

- Quad SPI Interface

- Two Inter-Integrated Circuit (I<sup>2</sup>C) Ports

- Three Multichannel Audio Serial Ports (McASP)

- MultiMedia Card/Secure Digital/Secure Digital Input Output Interface (MMC/SD/SDIO)

- Up to 126 General-Purpose I/O (GPIO) Pins

- Power, Reset, and Clock Management

- On-Chip Debug With CTools Technology

- Automotive AEC-Q100 Qualified

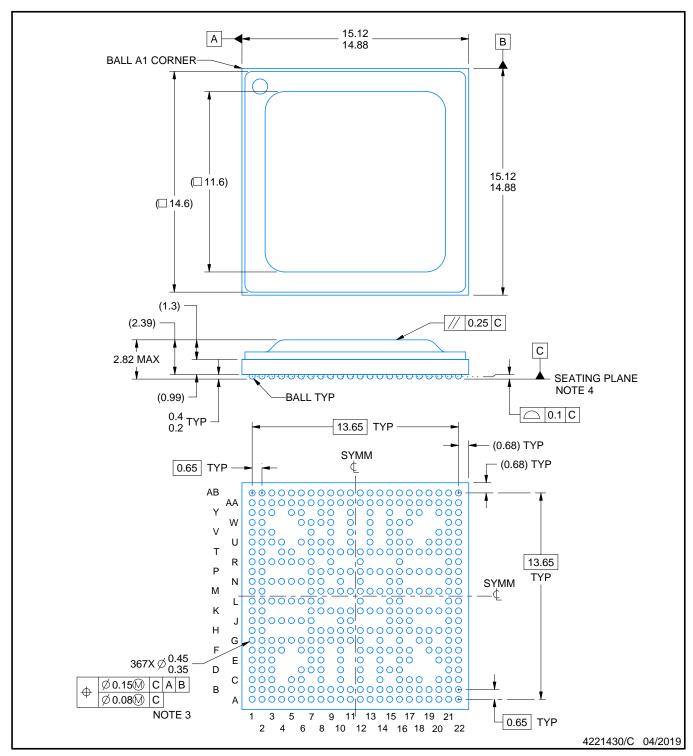

- 15 x 15mm, 0.65-mm Pitch, 367-Pin PBGA (ABF)

- 8-Channel 10-bit ADC

- MIPI CSI-2 Camera Serial Interface

- **PWMSS**

- Full HW Image Pipe: DPC, CFA, 3D-NF, RGB-YUV

- WDR, HW LDC and Perspective

#### 1.2 Applications

- Drones

- Robotics

- Industrial Transportation (Forklift, Rail, Agriculture)

- Factory and Building Automation cameras

#### 1.3 Description

The DM505 is a highly optimized device for Vision Analytics and Machine Vision processing in Industrial products such as drones, robots, forklifts, railroad and agriculture equipment. The Processor enables sophisticated embedded vision processing integrating an optimal mix of real time performance, low power, small form factor and camera processing for systems to interact in more intelligent, useful ways with the physical world and the people in it.

The DM505 incorporates a heterogeneous, scalable architecture that includes a mix of TI's fixed and floating-point TMS320C66x digital signal processor (DSP) generation cores, Vision AccelerationPac (EVE), and dual-Cortex-M4 processors. The device allows low power designs to meet demanding embedded system budgets without sacrificing real-time processing performance to enable small form factor designs. The DM505 also integrates a host of peripherals including interfaces for multi-camera input (both parallel and serial), display outputs, audio and serial I/O, CAN and GigB Ethernet AVB.

TI provides application specific hardware and software through our Design Network Partners and a complete set of development tools for the Arm, and DSP, including C compilers with TI RTOS to accelerate time to market.

#### **Device Information**

| PART NUMBER | PACKAGE      | BODY SIZE         |

|-------------|--------------|-------------------|

| DM505       | S-PBGA (367) | 15.0 mm × 15.0 mm |

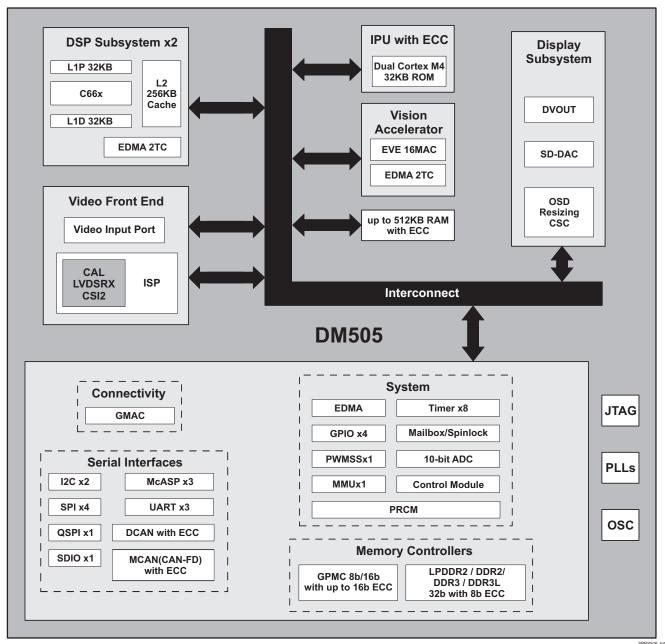

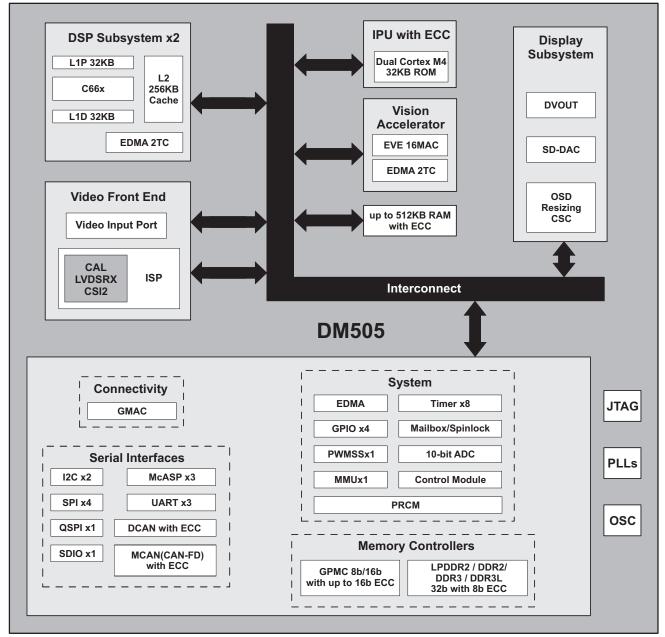

#### 1.4 Functional Block Diagram

Figure 1-1 is functional block diagram of the superset.

Copyright © 2016, Texas Instruments Incorporated

Figure 1-1. DM505 Block Diagram

#### **Table of Contents**

| 1 | Devi | ice Overview 1                      |   | 6.6  | Memory Subsystem                                 | 189         |

|---|------|-------------------------------------|---|------|--------------------------------------------------|-------------|

|   | 1.1  | Features 1                          |   | 6.7  | Interprocessor Communication                     | 192         |

|   | 1.2  | Applications 2                      |   | 6.8  | Interrupt Controller                             | 193         |

|   | 1.3  | Description                         |   | 6.9  | EDMA                                             | 193         |

|   | 1.4  | Functional Block Diagram3           |   | 6.10 | Peripherals                                      | 195         |

| 2 | Revi | ision History <u>5</u>              |   | 6.11 | On-Chip Debug                                    | 207         |

| 3 | Devi | ice Comparison <u>6</u>             | 7 | Appl | lications, Implementation, and Layout            | <b>21</b> 1 |

|   | 3.1  | Device Comparison Table 6           |   | 7.1  | Introduction                                     | 211         |

| 4 | Tern | ninal Configuration and Functions 8 |   | 7.2  | Power Optimizations                              | 212         |

|   | 4.1  | Pin Diagram <u>8</u>                |   | 7.3  | Core Power Domains                               | 223         |

|   | 4.2  | Pin Attributes 8                    |   | 7.4  | Single-Ended Interfaces                          | 233         |

|   | 4.3  | Signal Descriptions                 |   | 7.5  | Differential Interfaces                          | 235         |

|   | 4.4  | Pin Multiplexing64                  |   | 7.6  | Clock Routing Guidelines                         | 237         |

|   | 4.5  | Connections for Unused Pins 75      |   | 7.7  | LPDDR2 Board Design and Layout Guidelines        | 238         |

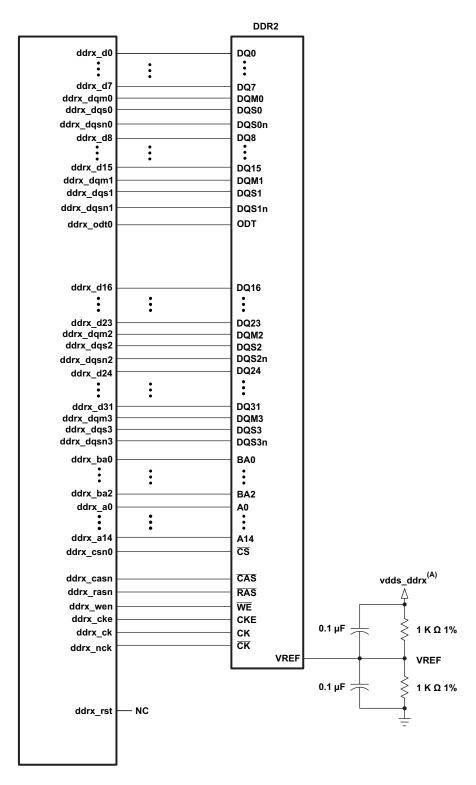

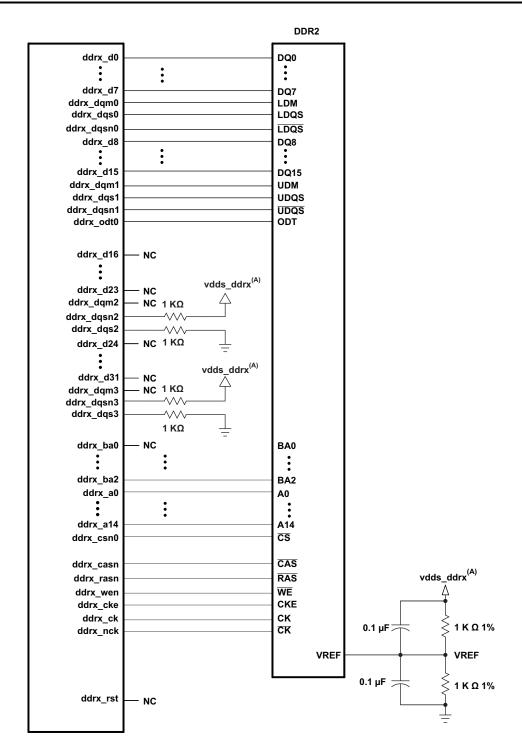

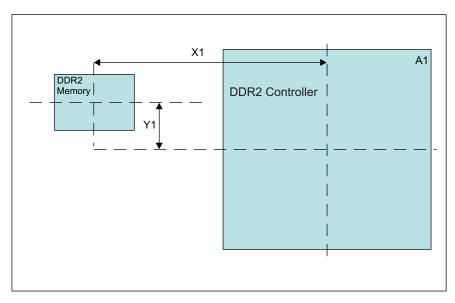

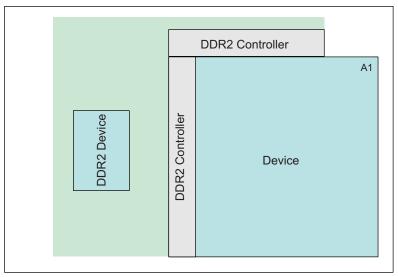

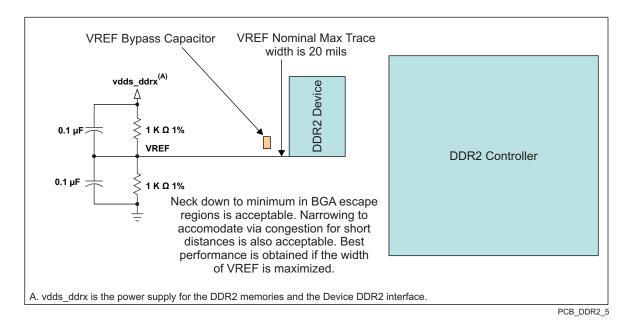

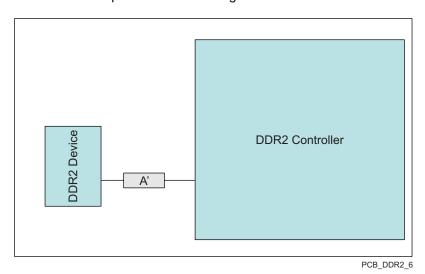

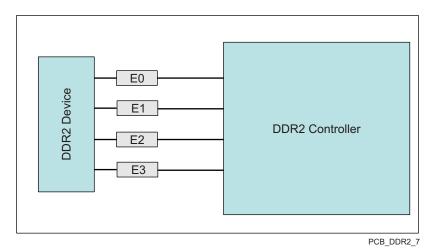

| 5 | Spec | cifications <u>76</u>               |   | 7.8  | DDR2 Board Design and Layout Guidelines          | 247         |

|   | 5.1  | Absolute Maximum Ratings 77         |   | 7.9  | DDR3 Board Design and Layout Guidelines          | 259         |

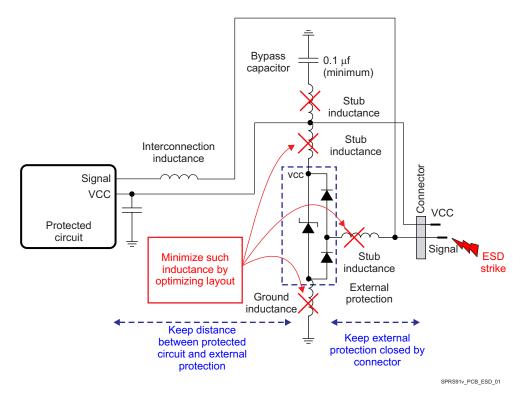

|   | 5.2  | ESD Ratings 77                      |   | 7.10 | CVIDEO/SD-DAC Guidelines and Electrical          |             |

|   | 5.3  | Power on Hour (POH) Limits          |   |      | Data/Timing                                      |             |

|   | 5.4  | Recommended Operating Conditions    | 8 | Devi | ce and Documentation Support                     |             |

|   | 5.5  | Operating Performance Points81      |   | 8.1  | Device Nomenclature                              | 284         |

|   | 5.6  | Power Consumption Summary 90        |   | 8.2  | Tools and Software                               | 286         |

|   | 5.7  | Electrical Characteristics 90       |   | 8.3  | Documentation Support                            | 286         |

|   | 5.8  | Thermal Characteristics 97          |   | 8.4  | Receiving Notification of Documentation Updates. |             |

|   | 5.9  | Timing Requirements and Switching   |   | 8.5  | Community Resources                              | 287         |

|   |      | Characteristics                     |   | 8.6  | Trademarks                                       | 287         |

| 6 | Deta | illed Description                   |   | 8.7  | Electrostatic Discharge Caution                  | 288         |

|   | 6.1  | Description                         |   | 8.8  | Export Control Notice                            | 288         |

|   | 6.2  | Functional Block Diagram 180        |   | 8.9  | Glossary                                         | _           |

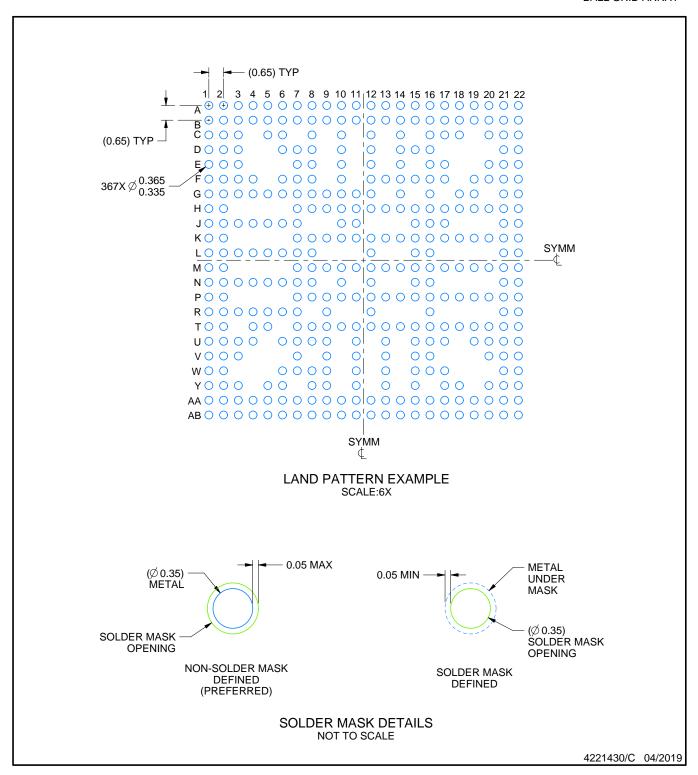

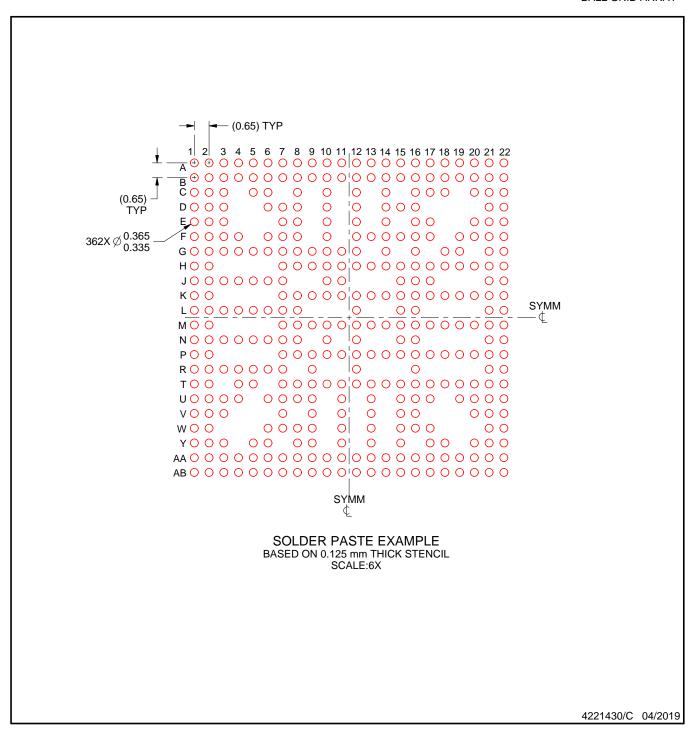

|   | 6.3  | DSP Subsystem <u>181</u>            | 9 | Mec  | hanical Packaging Information                    | 289         |

|   | 6.4  | IPU <u>186</u>                      |   | 9.1  | Mechanical Data                                  | 290         |

|   | 6.5  | EVE 187                             |   |      |                                                  |             |

# 2 Revision History

| Chang | ges from July 31, 2017 to May 5, 2018 (from D Revision (July 2017) to E Revision)                                                                                                       | Page  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| •     | Updated "ARM" references to "Arm" in Section 1.1, Features. Updated "ARM" references to "Arm" in Table 3-1, Device Comparison. Added clarification notes to Section 4.2, Pin Attributes | 8     |

| •     | Updated I/O VOLTAGE VALUE column in Table 4-1, Pin Attributes to include 1.2V to all ddr signals                                                                                        | 10    |

| •     | Updated some GPMC ball reset release muxmode values in Table 4-1, Pin Attributes  Removed balls from Table 4-16, McASP Signal Descriptions                                              | 52    |

| •     | Updated "ARM" references to "Arm" in Table 4-26, INTC Signal Descriptions                                                                                                               |       |

| •     | DDR2 are used                                                                                                                                                                           | 82    |

| •     | Removed voltage high level limits from Table 5-11, LVCMOS CSI2 DC Electrical Characteristics                                                                                            | 94    |

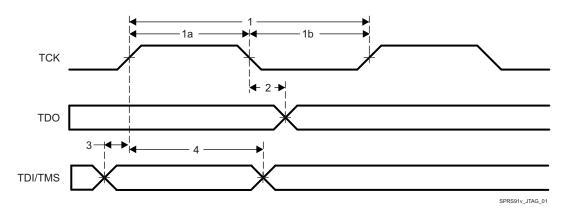

| •     | Updated Section 5.9.1, Timing Parameters and Information                                                                                                                                | 102   |

| •     | Updated DPLL CLKOUT output frequency in Table 5-26, DPLL Characteristics                                                                                                                | . 114 |

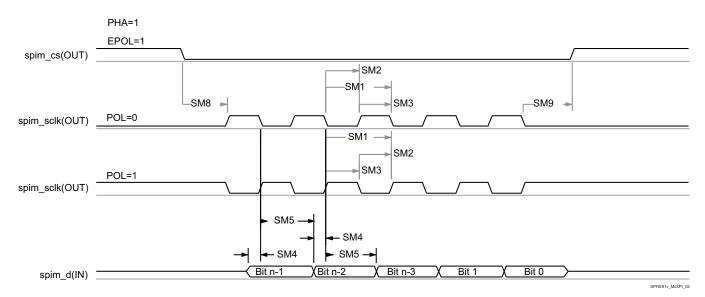

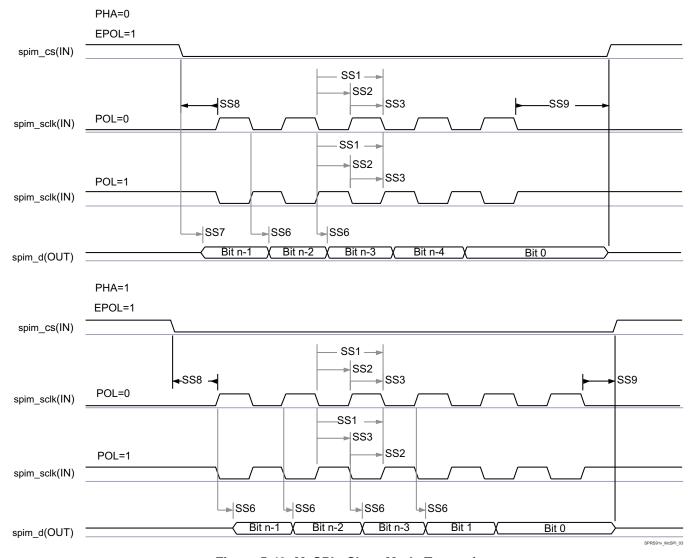

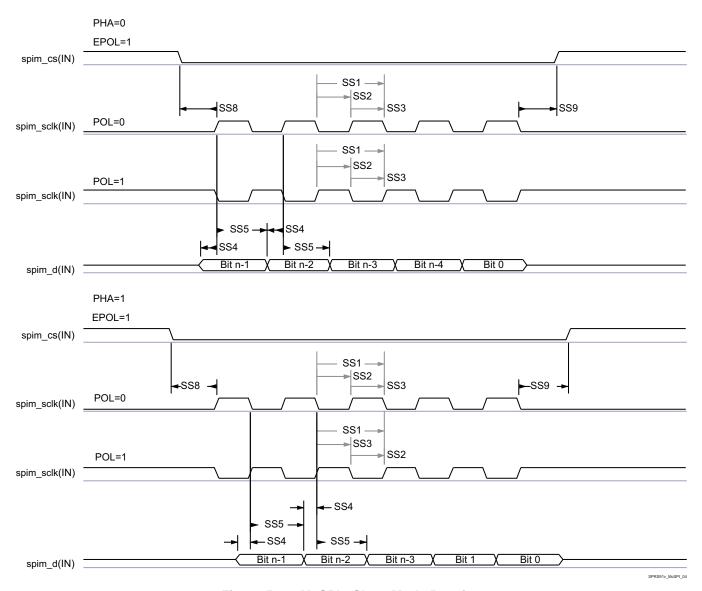

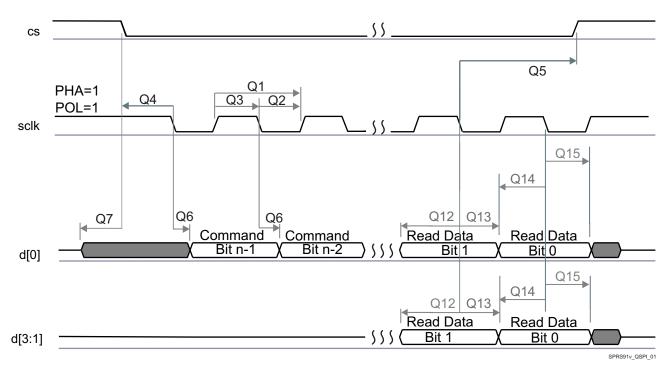

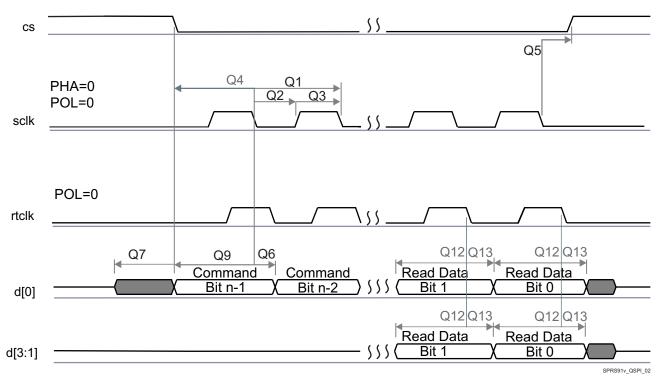

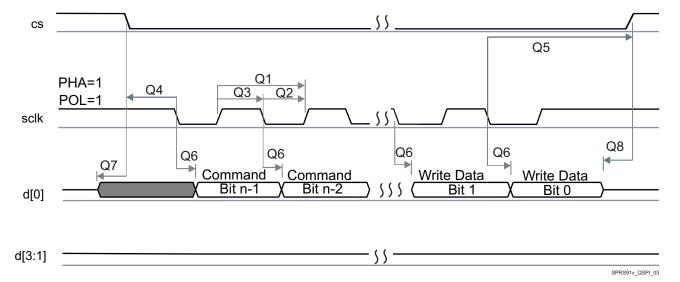

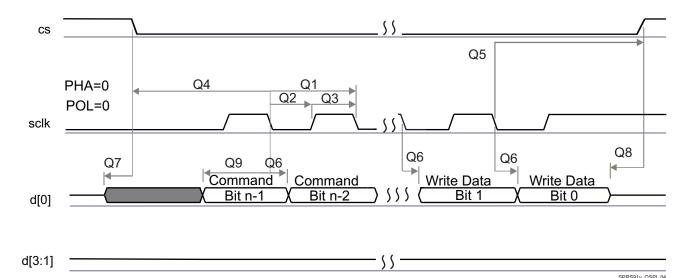

| •     | Updated Phase polarity in all QSPI timing figures                                                                                                                                       | 156   |

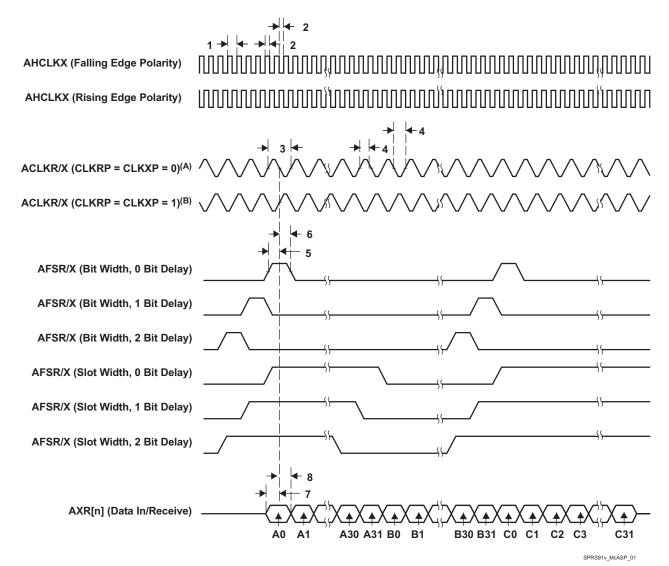

| •     | Added Table 5-59, McASP2 IOSETs                                                                                                                                                         | 165   |

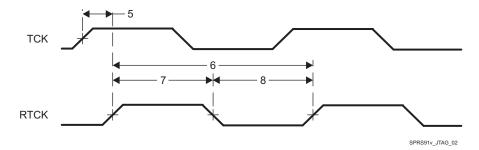

| •     | Updated "ARM" references to "Arm" Table 5-82, Switching Characteristics Over Recommended Operating Conditions for IEEE 1149.1 JTAG With RTCK                                            |       |

| •     | Updated "ARM" references to "Arm" in Section 6, Detailed Description  Added Section 7.3.7, Loss of Input Power Event                                                                    | . 228 |

| •     | Added new parameter in Table 7-11, Length Mismatch Guidelines for CSI-2 (1.5 Gbps)                                                                                                      |       |

### 3 Device Comparison

#### 3.1 Device Comparison Table

Table 3-1 shows a comparison between devices, highlighting the differences.

**Table 3-1. Device Comparison**

| Features                              |                    |                               | Dev                | ice                |

|---------------------------------------|--------------------|-------------------------------|--------------------|--------------------|

|                                       |                    |                               | DM505M             | DM505L             |

| Features                              |                    |                               |                    |                    |

| CTRL_WKUP_STD_FU value <sup>(3)</sup> | JSE_DIE_ID_2 [31:2 | 24] Base PN register bitfield | 156 (0x9C65)       | 156 (0x9C5D)       |

| Processors/ Accelerat                 | tors               | -1                            |                    |                    |

| Speed Grades                          |                    |                               | R                  | R                  |

| C66x™ VLIW DSP                        |                    | DSP1                          | Yes                | Yes                |

|                                       |                    | DSP2                          | Yes                | No                 |

| Display Subsystem                     |                    | VOUT1                         | Yes                | Yes                |

|                                       |                    | SD_DAC                        | Yes                | Yes                |

| Embedded Vision Engir                 | ne (EVE)           | EVE1                          | Yes                | Yes                |

| Arm Dual Cortex-M4 Im<br>Unit (IPU)   | nage Processing    | IPU1                          | Yes                | Yes                |

| Imaging Subsystem Pro                 |                    | ISP                           | Yes                | Yes                |

| MIPI CSI-2 and CPI por                | rts                | WDR & Mesh LDC <sup>(1)</sup> | Yes                | Yes                |

|                                       |                    | CAL_A                         | Yes                | Yes                |

|                                       |                    | CAL_B                         | Yes                | Yes                |

|                                       |                    | LVDS-RX                       | Yes                | Yes                |

|                                       |                    | СРІ                           | Yes                | Yes                |

|                                       | /IP1               | vin1a                         | Yes                | Yes                |

| (VIP)                                 |                    | vin1b                         | Yes                | Yes                |

|                                       |                    | vin2a                         | Yes                | Yes                |

|                                       |                    | vin2b                         | Yes                | Yes                |

| Program/Data Storage                  | )                  |                               |                    |                    |

| On-Chip Shared Memor                  | ry (RAM)           | OCMC_RAM1                     | 512kB              | 256kB              |

| General-Purpose Memo<br>(GPMC)        | ory Controller     | GPMC                          | Yes                | Yes                |

| LPDDR2/DDR2/DDR3/I<br>Controller      | DDR3L Memory       | EMIF1 (optional with SECDED)  | up to 2GB          | up to 2GB          |

| Peripherals                           |                    | •                             | •                  |                    |

| Controller Area Network               | k Interface (CAN)  | DCAN1                         | Yes                | Yes                |

|                                       |                    | MCAN                          | Yes <sup>(2)</sup> | Yes <sup>(2)</sup> |

| Enhanced DMA (EDMA                    | A)                 | EDMA                          | Yes                | Yes                |

| Embedded 8 channel A                  | DC                 | ADC                           | Yes                | Yes                |

| Ethernet Subsystem (Et                | thernet SS)        | GMAC_SW[0]                    | RGMII Only         | RGMII Only         |

|                                       |                    | GMAC_SW[1]                    | RGMII Only         | RGMII Only         |

| General-Purpose IO (G                 | PIO)               | GPIO                          | Up to 126          | Up to 126          |

| Inter-Integrated Circuit I            | Interface (I2C)    | I2C                           | 2                  | 2                  |

| System Mailbox Module                 | e                  | MAILBOX                       | 2                  | 2                  |

| Multichannel Audio Seri               | ial Port (McASP)   | McASP1                        | 16 serializers     | 16 serializers     |

|                                       |                    | McASP2                        | 6 serializers      | 6 serializers      |

|                                       |                    | McASP3                        | 6 serializers      | 6 serializers      |

**Table 3-1. Device Comparison (continued)**

| Features                                                                                 |          | Devi       | ce         |

|------------------------------------------------------------------------------------------|----------|------------|------------|

|                                                                                          |          | DM505M     | DM505L     |

| MultiMedia Card/Secure Digital/Secure<br>Digital Input Output Interface<br>(MMC/SD/SDIO) | MMC      | 1x SDIO 4b | 1x SDIO 4b |

| Multichannel Serial Peripheral Interface (McSPI)                                         | McSPI    | 4          | 4          |

| Quad SPI (QSPI)                                                                          | QSPI     | Yes        | Yes        |

| Spinlock Module                                                                          | SPINLOCK | Yes        | Yes        |

| Timers, General-Purpose                                                                  | TIMER    | 8          | 8          |

| Pulse-Width Modulation Subsystem (PWMSS)                                                 | PWMSS1   | Yes        | Yes        |

| Universal Asynchronous<br>Receiver/Transmitter (UART)                                    | UART     | 3          | 3          |

- (1) Wide Dynamic Range and Lens Distortion Correction.

- (2) Device supports FD (Flexible Data Rate)

- (3) For more details about the CTRL\_WKUP\_STD\_FUSE\_DIE\_ID\_2 register and Base PN bitfield, see the *DM50x Technical Reference Manual*.

#### 4 Terminal Configuration and Functions

#### 4.1 Pin Diagram

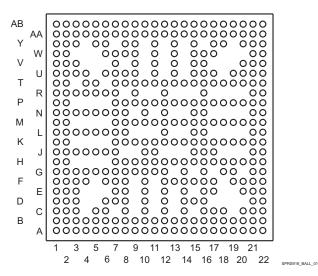

Figure 4-1 shows the ball locations for the 367 plastic ball grid array (PBGA) package and are used in conjunction with Table 4-1 through Table 4-27 to locate signal names and ball grid numbers.

Figure 4-1. ABF S-PBGA-N367 Package (Bottom View)

#### **NOTE**

The following bottom balls are not connected: C4 / C7 / C9 / C11 / C13 / C15 / C19 / D4 / D5 / D9 / D11 / D13 / D17 / D18 / D19 / D20 / E4 / E5 / E6 / E9 / E11 / E13 / E15 / E18 / E19 / F5 / F9 / F11 / F18 / G13 / G15 / G17 / G20 / H3 / H4 / H5 / H6 / J8 / J9 / J12 / J13 / J14 / J18 / J19 / J20 / K3 / K4 / K5 / K6 / L9 / L10 / L11 / L13 / L14 / L17 / L18 / L19 / L20 / M3 / M4 / M5 / M6 / N9 / N11 / N13 / N14 / N17 / N18 / N19 / N20 / P3 / P4 / P5 / P6 / R8 / R10 / R11 / R13 / R14 / R15 / R17 / R18 / R19 / R20 / T3 / T6 / U5 / U10 / U12 / U14 / U18 / V4 / V5 / V6 / V8 / V10 / V12 / V14 / V17 / V18 / V19 / W3 / W4 / W5 / W10 / W12 / W14 / W18 / W19 / W20 / Y4 / Y7 / Y10 / Y12 / Y14 / Y16 / Y19.

These balls do not exist on the package.

#### 4.2 Pin Attributes

Table 4-1 describes the terminal characteristics and the signals multiplexed on each ball. The following list describes the table column headers:

- 1. BALL NUMBER: Ball number(s) on the bottom side associated with each signal on the bottom.

- 2. BALL NAME: Mechanical name from package device (name is taken from muxmode 0).

- 3. **SIGNAL NAME:** Names of signals multiplexed on each ball (also notice that the name of the ball is the signal name in muxmode 0).

#### **NOTE**

Table 4-1 does not take into account the subsystem multiplexing signals. Subsystem multiplexing signals are described in Section 4.3, Signal Descriptions.

#### NOTE

In the Driver off mode, the buffer is configured in high-impedance.

- 4. **MUXMODE:** Multiplexing mode number:

- a. MUXMODE 0 is the primary mode; this means that when MUXMODE=0 is set, the function mapped on the pin corresponds to the name of the pin. The primary muxmode is not necessarily the default muxmode.

#### NOTE

The default mode is the mode at the release of the reset; also see the RESET REL. MUXMODE column.

- b. MUXMODE 1 through 15 are possible muxmodes for alternate functions. On each pin, some muxmodes are effectively used for alternate functions, while some muxmodes are not used. Only MUXMODE values which correspond to defined functions should be used.

- c. An empty box means Not Applicable.

- 5. **TYPE:** Signal type and direction:

- I = Input

- O = Output

- IO = Input or Output

- D = Open drain

- DS = Differential Signaling

- -A = Analog

- PWR = Power

- GND = Ground

- CAP = LDO Capacitor

- 6. **BALL RESET STATE:** The state of the terminal at power-on reset:

- drive 0 (OFF): The buffer drives V<sub>OL</sub> (pulldown or pullup resistor not activated).

- drive 1 (OFF): The buffer drives V<sub>OH</sub> (pulldown or pullup resistor not activated).

- OFF: High-impedance

- PD: High-impedance with an active pulldown resistor

- PU: High-impedance with an active pullup resistor

- An empty box means Not Applicable

- 7. **BALL RESET REL. STATE:** The state of the terminal at the deactivation of the rstoutn signal (also mapped to the PRCM SYS\_WARM\_OUT\_RST signal).

- drive 0 (OFF): The buffer drives V<sub>OL</sub> (pulldown or pullup resistor not activated).

- drive clk (OFF): The buffer drives a toggling clock (pulldown or pullup resistor not activated).

- drive 1 (OFF): The buffer drives V<sub>OH</sub> (pulldown or pullup resistor not activated).

- OFF: High-impedance

- PD: High-impedance with an active pulldown resistor

- PU: High-impedance with an active pullup resistor

- An empty box means Not Applicable

#### NOTE

For more information on the CORE\_PWRON\_RET\_RST reset signal and its reset sources, see the Power, Reset, and Clock Management / Reset Management Functional Description section of the Device TRM.

BALL RESET REL. MUXMODE: This muxmode is automatically configured at the release of the rstoutn signal (also mapped to the PRCM SYS\_WARM\_OUT\_RST signal).

An empty box means Not Applicable.

IO VOLTAGE VALUE: This column describes the IO voltage value (the corresponding power supply).

An empty box means Not Applicable.

10. **POWER:** The voltage supply that powers the terminal IO buffers.

An empty box means Not Applicable.

- 11. **HYS:** Indicates if the input buffer is with hysteresis:

- Yes: With hysteresis

- No: Without hysteresis

- An empty box: Not Applicable

#### NOTE

For more information, see the hysteresis values in Section 5.7, DC Electrical Characteristics.

12. **BUFFER TYPE:** Drive strength of the associated output buffer.

An empty box means Not Applicable.

#### NOTE

For programmable buffer strength:

- The default value is given in Table 4-1.

- A note describes all possible values according to the selected muxmode.

- 13. **PULL UP / DOWN TYPE:** Denotes the presence of an internal pullup or pulldown resistor. Pullup and pulldown resistors can be enabled or disabled via software.

- PU: Internal pullup

- PD: Internal pulldown

- PU/PD: Internal pullup and pulldown

- PUx/PDy: Programmable internal pullup and pulldown

- PDy: Programmable internal pulldown

- An empty box means No pull

- 14. **DSIS:** The deselected input state (DSIS) indicates the state driven on the peripheral input (logic "0" or logic "1") when the peripheral pin function is not selected by any of the CTRL\_CORE\_PADx registers.

- 0: Logic 0 driven on the peripheral's input signal port.

- 1: Logic 1 driven on the peripheral's input signal port.

- blank: Pin state driven on the peripheral's input signal port.

#### NOTE

Configuring two pins to the same input signal is not supported as it can yield unexpected results. This can be easily prevented with the proper software configuration (Hi-Z mode is not an input signal).

#### NOTE

When a pad is set into a multiplexing mode which is not defined by pin multiplexing, that pad's behavior is undefined. This should be avoided.

### Table 4-1. Pin Attributes<sup>(1)</sup>

| BALL NUMBER [1] | BALL NAME [2]     | SIGNAL NAME [3]   | MUXMODE [4] | TYPE [5] | BALL<br>RESET<br>STATE [6] | BALL<br>RESET REL.<br>STATE [7] | BALL<br>RESET REL.<br>MUXMODE<br>[8] | I/O<br>VOLTAGE<br>VALUE [9] | POWER [10] | HYS [11] | BUFFER<br>TYPE [12] | PULL<br>UP/DOWN<br>TYPE [13] | DSIS [14] |

|-----------------|-------------------|-------------------|-------------|----------|----------------------------|---------------------------------|--------------------------------------|-----------------------------|------------|----------|---------------------|------------------------------|-----------|

| M19             | adc_in0           | adc_in0           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| M20             | adc_in1           | adc_in1           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| M21             | adc_in2           | adc_in2           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| M22             | adc_in3           | adc_in3           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| N22             | adc_in4           | adc_in4           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| N21             | adc_in5           | adc_in5           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| P19             | adc_in6           | adc_in6           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| P18             | adc_in7           | adc_in7           | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| P20             | adc_vrefp         | adc_vrefp         | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_adc   |          | GPADC               |                              |           |

| N15             | cap_vddram_core1  | cap_vddram_core1  |             | CAP      |                            |                                 |                                      |                             |            |          |                     |                              |           |

| M15             | cap_vddram_core2  | cap_vddram_core2  |             | CAP      |                            |                                 |                                      |                             |            |          |                     |                              |           |

| M14             | cap_vddram_dspeve | cap_vddram_dspeve |             | CAP      |                            |                                 |                                      |                             |            |          |                     |                              |           |

| A11             | csi2_0_dx0        | csi2_0_dx0        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| A12             | csi2_0_dx1        | csi2_0_dx1        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| A13             | csi2_0_dx2        | csi2_0_dx2        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| A15             | csi2_0_dx3        | csi2_0_dx3        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| A16             | csi2_0_dx4        | csi2_0_dx4        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| B11             | csi2_0_dy0        | csi2_0_dy0        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| B12             | csi2_0_dy1        | csi2_0_dy1        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| B13             | csi2_0_dy2        | csi2_0_dy2        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| B15             | csi2_0_dy3        | csi2_0_dy3        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| B16             | csi2_0_dy4        | csi2_0_dy4        | 0           | I        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_csi   | Yes      | LVCMOS<br>CSI2      | PU/PD                        |           |

| T18             | cvideo_rset       | cvideo_rset       | 0           | Α        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_dac   |          | AVDAC               |                              |           |

| T17             | cvideo_tvout      | cvideo_tvout      | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_dac   |          | AVDAC               |                              |           |

| P17             | cvideo_vfb        | cvideo_vfb        | 0           | A        | OFF                        | OFF                             | 0                                    | 1.8                         | vdda_dac   |          | AVDAC               |                              |           |

| N6              | dcan1_rx          | dcan1_rx          | 0           | Ю        | PU                         | PU                              | 15                                   | 1.8/3.3                     | vddshv1    | Yes      | Dual Voltage        | PU/PD                        |           |

|                 |                   | gpio4_10          | 14          | Ю        |                            |                                 |                                      |                             |            |          | LVCMOS              |                              |           |

|                 |                   | Driver off        | 15          | I        |                            |                                 |                                      |                             |            |          |                     |                              |           |

| N5              | dcan1_tx          | dcan1_tx          | 0           | Ю        | PU                         | PU                              | 15                                   | 1.8/3.3                     | vddshv1    | Yes      | Dual Voltage        | PU/PD                        |           |

|                 |                   | gpio4_9           | 14          | Ю        |                            |                                 |                                      |                             |            |          | LVCMOS              |                              |           |

|                 |                   | Driver off        | 15          | I        |                            |                                 |                                      |                             |            |          |                     |                              |           |

| BALL NUMBER [1] | BALL NAME [2] | SIGNAL NAME [3] | MUXMODE [4] | TYPE [5] | BALL<br>RESET<br>STATE [6] | BALL<br>RESET REL<br>STATE [7] | BALL<br>RESET REL<br>MUXMODE<br>[8] | I/O<br>VOLTAGE<br>VALUE [9] | POWER [10] | HYS [11] | BUFFER<br>TYPE [12] | PULL<br>UP/DOWN<br>TYPE [13] | DSIS [14] |

|-----------------|---------------|-----------------|-------------|----------|----------------------------|--------------------------------|-------------------------------------|-----------------------------|------------|----------|---------------------|------------------------------|-----------|

| F2              | ddr1_casn     | ddr1_casn       | 0           | 0        | PD                         | drive 1 (OFF                   | ) 0                                 | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| G1              | ddr1_ck       | ddr1_ck         | 0           | 0        | PD                         | drive clk<br>(OFF)             | 0                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB13            | ddr1_dqm_ecc  | ddr1_dqm_ecc    | 0           | Ю        | PD                         | PD                             | 0                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB10            | ddr1_dqsn_ecc | ddr1_dqsn_ecc   | 0           | Ю        | PU                         | PU                             | 0                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA10            | ddr1_dqs_ecc  | ddr1_dqs_ecc    | 0           | Ю        | PD                         | PD                             | 0                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| G2              | ddr1_nck      | ddr1_nck        | 0           | 0        | PD                         | drive clk<br>(OFF)             | 0                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| F1              | ddr1_rasn     | ddr1_rasn       | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| N1              | ddr1_rst      | ddr1_rst        | 0           | 0        | PD                         | drive 0 (OFF                   | ,                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| E3              | ddr1_wen      | ddr1_wen        | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U4              | ddr1_a0       | ddr1_a0         | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| C1              | ddr1_a1       | ddr1_a1         | 0           | 0        | PD                         | drive 1 (OFF                   |                                     | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| D3              | ddr1_a2       | ddr1_a2         | 0           | 0        | PD                         | drive 1 (OFF                   |                                     | 1.2/1.35/1.5/               | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| R4              | ddr1_a3       | ddr1_a3         | 0           | 0        | PD                         | drive 1 (OFF                   |                                     | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| T4              | ddr1_a4       | ddr1_a4         | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| N3              | ddr1_a5       | ddr1_a5         | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| T2              | ddr1_a6       | ddr1_a6         | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| N2              | ddr1_a7       | ddr1_a7         | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| T1              | ddr1_a8       | ddr1_a8         | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U1              | ddr1_a9       | ddr1_a9         |             |          | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| D1              | ddr1_a10      | ddr1_a10        | 0           | 0        | PD                         | drive 1 (OFF                   | ,                                   | 1.2/1.35/1.5/               |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| R3              | ddr1_a11      | ddr1_a11        | 0           | 0        | PD                         | drive 1 (OFF                   | <u></u>                             | 1.2/1.35/1.5/               |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U2              | ddr1_a12      | ddr1_a12        | 0           | 0        | PD                         | drive 1 (OFF                   | <u></u>                             | 1.2/1.35/1.5/               |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| C3              | ddr1_a13      | ddr1_a13        | 0           | 0        | PD                         | drive 1 (OFF                   | ) 0                                 | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| BALL NUMBER [1] | BALL NAME [2] | SIGNAL NAME [3] | MUXMODE [4] | TYPE [5] | BALL<br>RESET<br>STATE [6] | BALL<br>RESET REL.<br>STATE [7] | BALL<br>RESET REL.<br>MUXMODE<br>[8] | I/O<br>VOLTAGE<br>VALUE [9] | POWER [10] | HYS [11] | BUFFER<br>TYPE [12] | PULL<br>UP/DOWN<br>TYPE [13] | DSIS [14] |

|-----------------|---------------|-----------------|-------------|----------|----------------------------|---------------------------------|--------------------------------------|-----------------------------|------------|----------|---------------------|------------------------------|-----------|

| R2              | ddr1_a14      | ddr1_a14        | 0           | 0        | PD                         | drive 1 (OFF)                   | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| V1              | ddr1_a15      | ddr1_a15        | 0           | 0        | PD                         | drive 1 (OFF)                   | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| B3              | ddr1_ba0      | ddr1_ba0        | 0           | 0        | PD                         | drive 1 (OFF)                   | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| A3              | ddr1_ba1      | ddr1_ba1        | 0           | 0        | PD                         | drive 1 (OFF)                   | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| D2              | ddr1_ba2      | ddr1_ba2        | 0           | 0        | PD                         | drive 1 (OFF)                   |                                      | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| F3              | ddr1_cke0     | ddr1_cke0       | 0           | 0        | PD                         | drive 0 (OFF)                   |                                      | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| B2              | ddr1_csn0     | ddr1_csn0       | 0           | 0        | PD                         | drive 1 (OFF)                   |                                      | 1.2/1.35/1.5/<br>1.8        | vdds_ddr2  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA6             | ddr1_d0       | ddr1_d0         | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA8             | ddr1_d1       | ddr1_d1         | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y8              | ddr1_d2       | ddr1_d2         | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA7             | ddr1_d3       | ddr1_d3         | 0           | 10       | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB4             | ddr1_d4       | ddr1_d4         | 0           | 10       | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/               | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y5              | ddr1_d5       | ddr1_d5         | 0           | 10       | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA4             | ddr1_d6       | ddr1_d6         | 0           | 10       | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y6              | ddr1_d7       | ddr1_d7         | 0           | 10       | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA18            | ddr1_d8       | ddr1_d8         | 0           | 10       | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y21             | ddr1_d9       | ddr1_d9         | 0           | 10       | PD<br>PD                   | PD<br>PD                        | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA21            | ddr1_d10      | ddr1_d10        |             | 10       |                            | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y22             | ddr1_d11      | ddr1_d11        | 0           |          | PD                         |                                 |                                      | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA19            | ddr1_d12      | ddr1_d12        | 0           | 10       | PD<br>PD                   | PD<br>PD                        | 0                                    | 1.2/1.35/1.5/<br>1.8        |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB20            | ddr1_d13      | ddr1_d13        |             |          | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y17             | ddr1_d14      | ddr1_d14        | 0           | 10       |                            | PD<br>PD                        | 0                                    | 1.2/1.35/1.5/<br>1.8        |            |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB18            | ddr1_d15      | ddr1_d15        | 0           | IU       | PD                         | טא                              | U                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| BALL NUMBER [1] | BALL NAME [2] | SIGNAL NAME [3] | MUXMODE [4] | TYPE [5] | BALL<br>RESET<br>STATE [6] | BALL<br>RESET REL.<br>STATE [7] | BALL<br>RESET REL.<br>MUXMODE<br>[8] | VOLTAGE<br>VALUE [9] | POWER [10] | HYS [11] | BUFFER<br>TYPE [12] | PULL<br>UP/DOWN<br>TYPE [13] | DSIS [14] |

|-----------------|---------------|-----------------|-------------|----------|----------------------------|---------------------------------|--------------------------------------|----------------------|------------|----------|---------------------|------------------------------|-----------|

| AA3             | ddr1_d16      | ddr1_d16        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA2             | ddr1_d17      | ddr1_d17        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y3              | ddr1_d18      | ddr1_d18        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| V2              | ddr1_d19      | ddr1_d19        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U3              | ddr1_d20      | ddr1_d20        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| V3              | ddr1_d21      | ddr1_d21        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y2              | ddr1_d22      | ddr1_d22        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y1              | ddr1_d23      | ddr1_d23        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U21             | ddr1_d24      | ddr1_d24        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| T20             | ddr1_d25      | ddr1_d25        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| R21             | ddr1_d26      | ddr1_d26        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U20             | ddr1_d27      | ddr1_d27        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| R22             | ddr1_d28      | ddr1_d28        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| V20             | ddr1_d29      | ddr1_d29        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| W22             | ddr1_d30      | ddr1_d30        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| U22             | ddr1_d31      | ddr1_d31        | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB8             | ddr1_dqm0     | ddr1_dqm0       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| Y18             | ddr1_dqm1     | ddr1_dqm1       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AB3             | ddr1_dqm2     | ddr1_dqm2       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| W21             | ddr1_dqm3     | ddr1_dqm3       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA5             | ddr1_dqs0     | ddr1_dqs0       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| AA20            | ddr1_dqs1     | ddr1_dqs1       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr3  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| W1              | ddr1_dqs2     | ddr1_dqs2       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8 | vdds_ddr1  |          | LVCMOS<br>DDR       | PUx/PDy                      |           |

| BALL NUMBER [1] | BALL NAME [2] | SIGNAL NAME [3] | MUXMODE [4] | TYPE [5] | BALL<br>RESET<br>STATE [6] | BALL<br>RESET REL.<br>STATE [7] | BALL<br>RESET REL.<br>MUXMODE<br>[8] | I/O<br>VOLTAGE<br>VALUE [9] | POWER [10] | HYS [11] | BUFFER<br>TYPE [12]    | PULL<br>UP/DOWN<br>TYPE [13] | DSIS [14] |

|-----------------|---------------|-----------------|-------------|----------|----------------------------|---------------------------------|--------------------------------------|-----------------------------|------------|----------|------------------------|------------------------------|-----------|

| T21             | ddr1_dqs3     | ddr1_dqs3       | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AB5             | ddr1_dqsn0    | ddr1_dqsn0      | 0           | Ю        | PU                         | PU                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| Y20             | ddr1_dqsn1    | ddr1_dqsn1      | 0           | Ю        | PU                         | PU                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| W2              | ddr1_dqsn2    | ddr1_dqsn2      | 0           | Ю        | PU                         | PU                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| T22             | ddr1_dqsn3    | ddr1_dqsn3      | 0           | Ю        | PU                         | PU                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr3  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| Y11             | ddr1_ecc_d0   | ddr1_ecc_d0     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AA12            | ddr1_ecc_d1   | ddr1_ecc_d1     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AA11            | ddr1_ecc_d2   | ddr1_ecc_d2     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| Y9              | ddr1_ecc_d3   | ddr1_ecc_d3     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AA13            | ddr1_ecc_d4   | ddr1_ecc_d4     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AB11            | ddr1_ecc_d5   | ddr1_ecc_d5     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AA9             | ddr1_ecc_d6   | ddr1_ecc_d6     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| AB9             | ddr1_ecc_d7   | ddr1_ecc_d7     | 0           | Ю        | PD                         | PD                              | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| P2              | ddr1_odt0     | ddr1_odt0       | 0           | 0        | PD                         | drive 0 (OFF)                   | 0                                    | 1.2/1.35/1.5/<br>1.8        | vdds_ddr1  |          | LVCMOS<br>DDR          | PUx/PDy                      |           |

| H1              | emu0          | emu0            | 0           | IO       | PU                         | PU                              | 0                                    | 1.8/3.3                     | vddshv1    | Yes      | Dual Voltage<br>LVCMOS | PU/PD                        |           |

|                 |               | gpio4_28        | 14          | IO       |                            |                                 |                                      |                             |            |          | LVCIVIOS               |                              |           |

|                 |               | Driver off      | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| H2              | emu1          | emu1            | 0           | Ю        | PU                         | PU                              | 0                                    | 1.8/3.3                     | vddshv1    | Yes      | Dual Voltage           | PU/PD                        |           |

|                 |               | gpio4_29        | 14          | IO       |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              |           |

|                 |               | Driver off      | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| E8              | gpmc_ad0      | gpmc_ad0        | 0           | IO       | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | rgmii1_rxd2     | 1           | I        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              | 0         |

|                 |               | gpio1_14        | 14          | IO       |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | sysboot0        | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| A7              | gpmc_ad1      | gpmc_ad1        | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | rgmii1_rxd1     | 1           | I        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              | 0         |

|                 |               | gpio1_15        | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | sysboot1        | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| BALL NUMBER [1] | BALL NAME [2] | SIGNAL NAME [3]             | MUXMODE [4] | TYPE [5] | BALL<br>RESET<br>STATE [6] | BALL<br>RESET REL.<br>STATE [7] | BALL<br>RESET REL.<br>MUXMODE<br>[8] | I/O<br>VOLTAGE<br>VALUE [9] | POWER [10] | HYS [11] | BUFFER<br>TYPE [12]    | PULL<br>UP/DOWN<br>TYPE [13] | DSIS [14] |

|-----------------|---------------|-----------------------------|-------------|----------|----------------------------|---------------------------------|--------------------------------------|-----------------------------|------------|----------|------------------------|------------------------------|-----------|

| F8              | gpmc_ad2      | gpmc_ad2                    | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | rgmii1_rxd0                 | 1           | I        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              | 0         |

|                 |               | gpio1_16                    | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | sysboot2                    | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| B7              | gpmc_ad3      | gpmc_ad3                    | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | qspi1_rtclk                 | 1           | I        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              | 0         |

|                 |               | gpio1_17                    | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | sysboot3                    | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| A6              | gpmc_ad4      | gpmc_ad4                    | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | cam_strobe                  | 1           | 0        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              |           |

|                 |               | gpio1_18                    | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | sysboot4                    | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| F7              | gpmc_ad5      | gpmc_ad5                    | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage<br>LVCMOS | PU/PD                        | 0         |

|                 |               | uart2_txd                   | 2           | 0        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              |           |

|                 |               | timer6                      | 3           | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | spi3_d1                     | 4           | Ю        |                            |                                 |                                      |                             |            |          |                        |                              | 0         |

|                 |               | gpio1_19                    | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        | PU/PD PU/PD PU/PD            |           |

|                 |               | sysboot5<br>mcasp2_aclkx    | 15          | 1        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| E7              | gpmc_ad6      | gpmc_ad6                    | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | uart2_rxd                   | 2           | I        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              | 1         |

|                 |               | timer5                      | 3           | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | spi3_d0                     | 4           | Ю        |                            |                                 |                                      |                             |            |          |                        |                              | 0         |

|                 |               | gpio1_20                    | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | sysboot6<br>mcasp2_fsx      | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| C6              | gpmc_ad7      | gpmc_ad7                    | 0           | Ю        | OFF                        | OFF                             | 0                                    | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | cam_shutter                 | 1           | 0        |                            |                                 |                                      |                             |            |          | LVCMOS                 |                              |           |

|                 |               | timer4                      | 3           | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | spi3_sclk                   | 4           | Ю        |                            |                                 |                                      |                             |            |          |                        |                              | 0         |

|                 |               | gpio1_21                    | 14          | Ю        |                            |                                 |                                      |                             |            |          |                        |                              |           |

|                 |               | Driver off<br>mcasp2_ahclkx | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |

| B6              | gpmc_ad8      | gpmc_ad8                    | 0           | Ю        | OFF                        | OFF                             | 15                                   | 1.8/3.3                     | vddshv2    | Yes      | Dual Voltage           | PU/PD                        | 0         |

|                 |               | timer7                      | 3           | Ю        | 1                          |                                 |                                      |                             |            |          | LVCMOS                 |                              |           |

|                 |               | spi3_cs0                    | 4           | Ю        | 1                          |                                 |                                      |                             |            |          |                        |                              | 1         |

|                 |               | gpio1_22                    | 14          | Ю        | 1                          |                                 |                                      |                             |            |          |                        |                              |           |

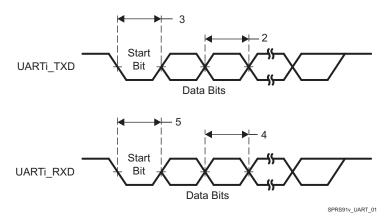

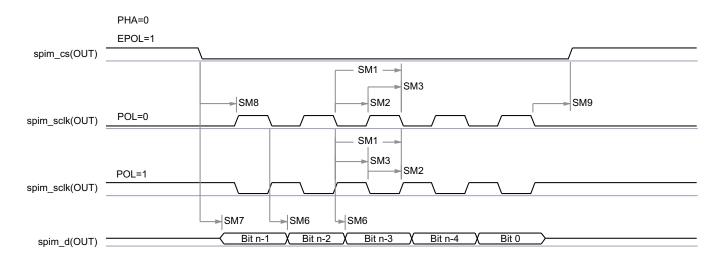

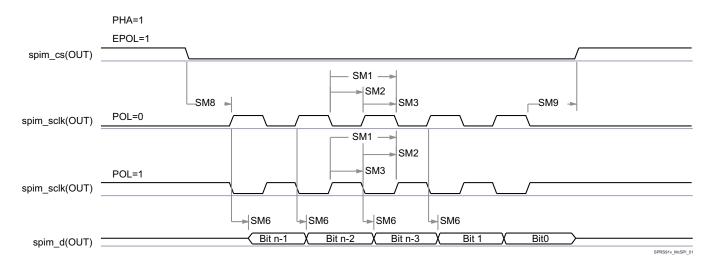

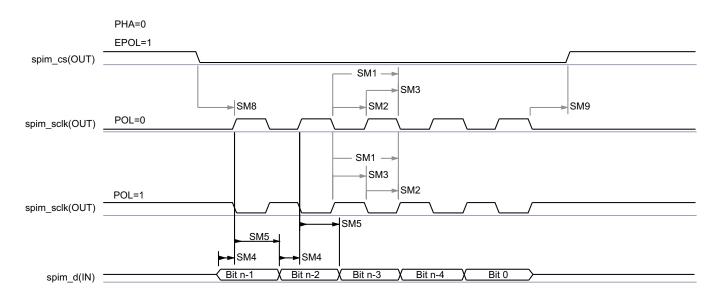

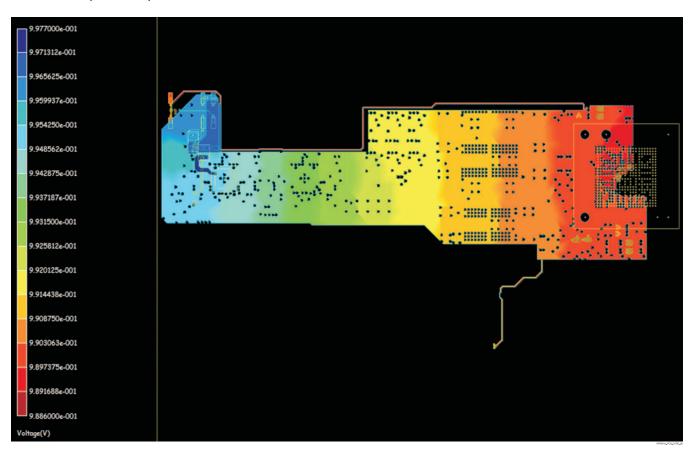

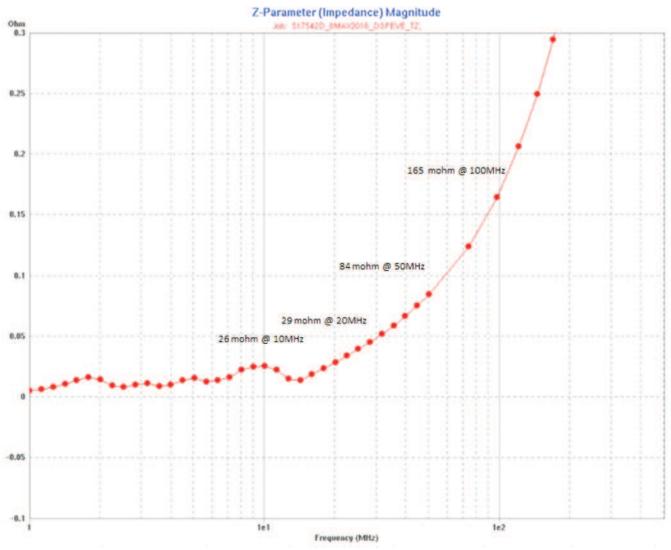

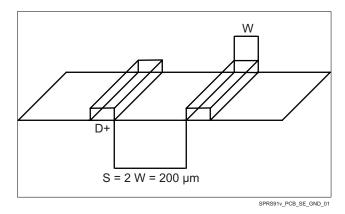

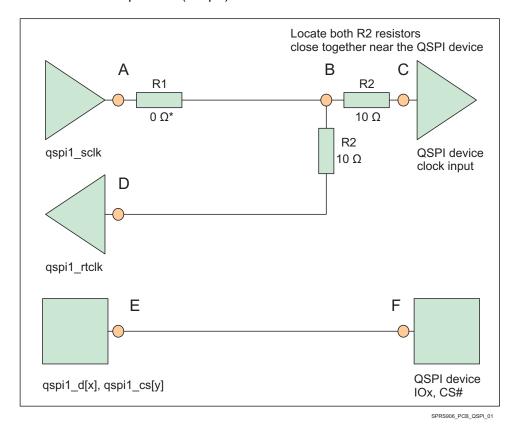

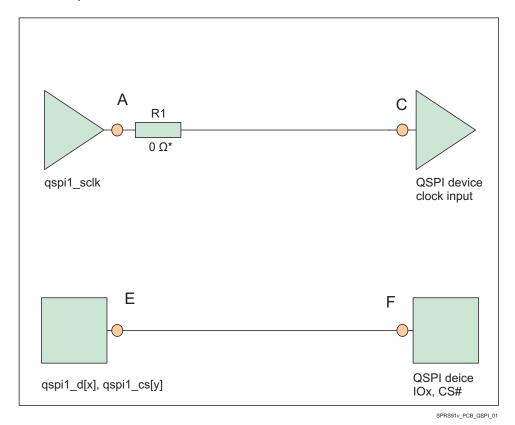

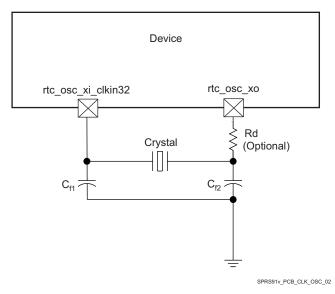

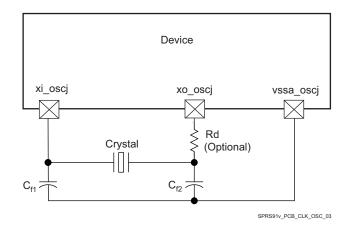

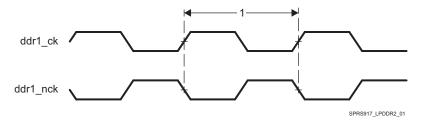

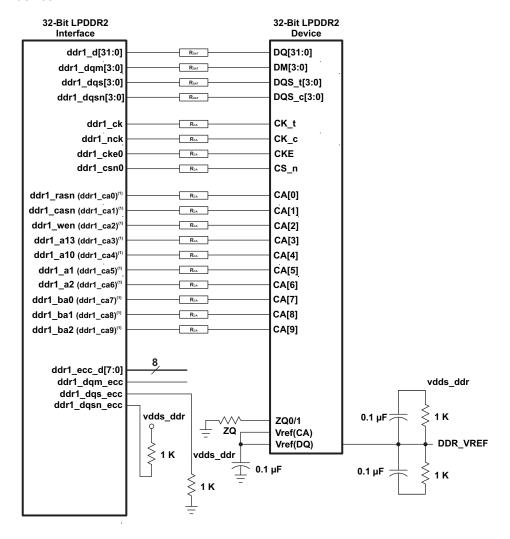

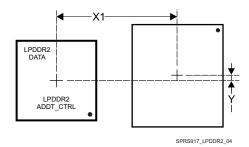

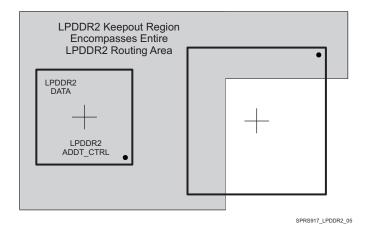

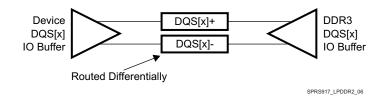

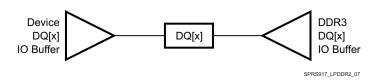

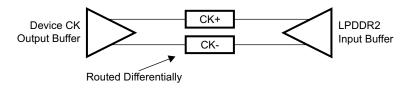

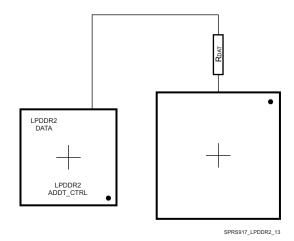

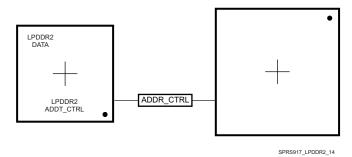

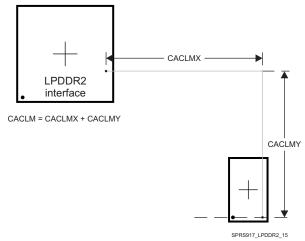

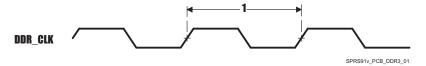

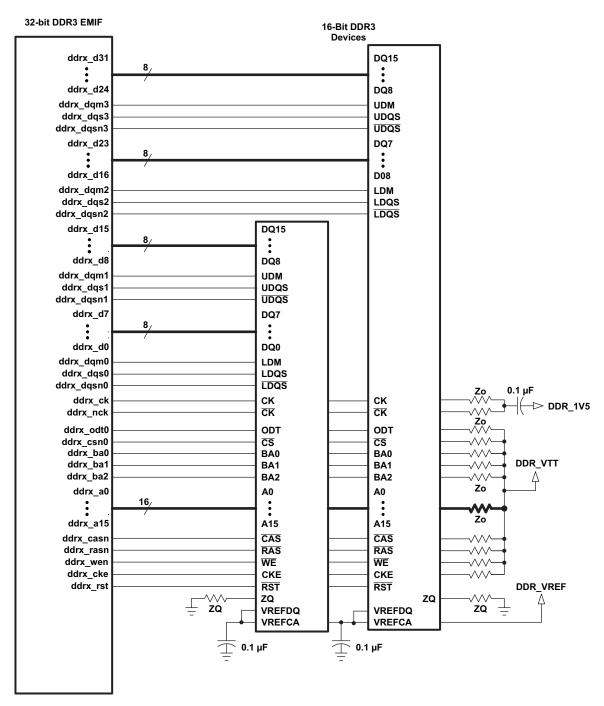

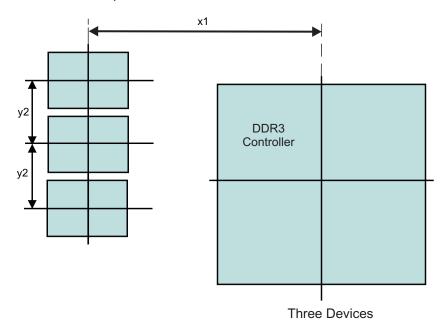

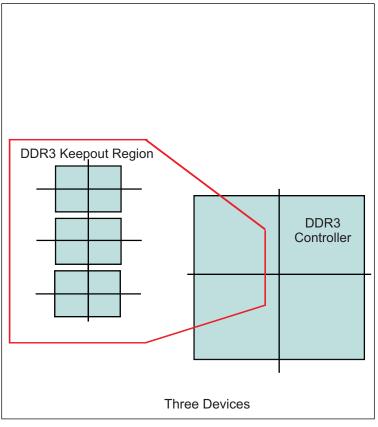

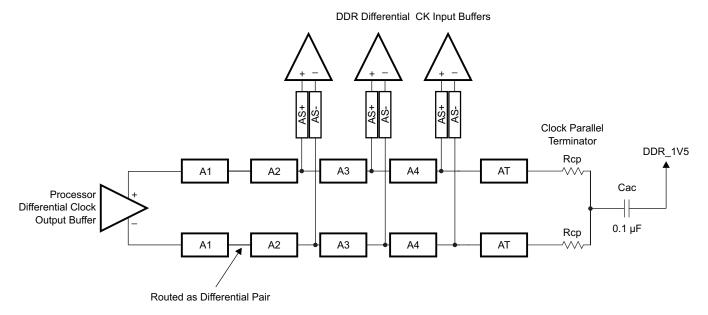

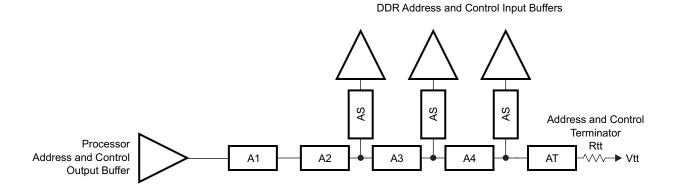

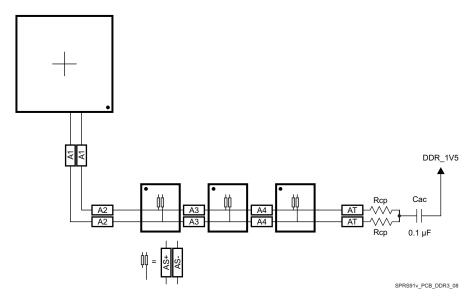

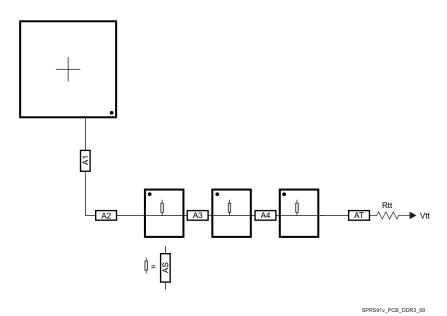

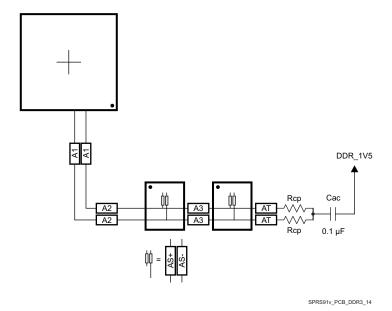

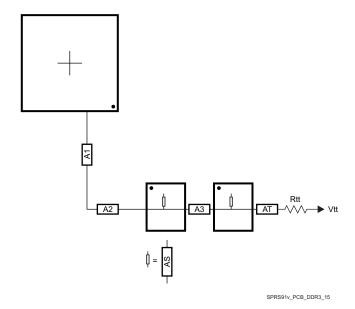

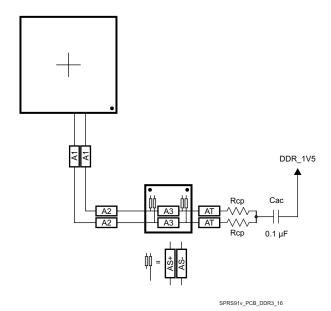

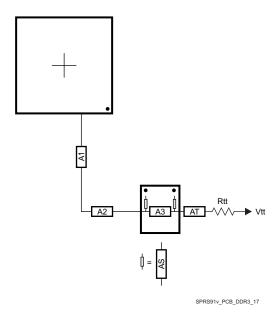

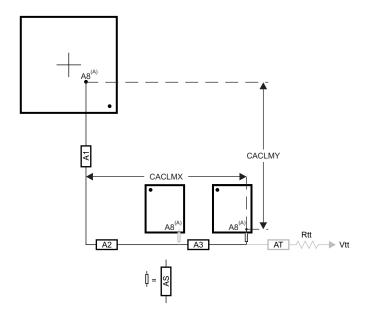

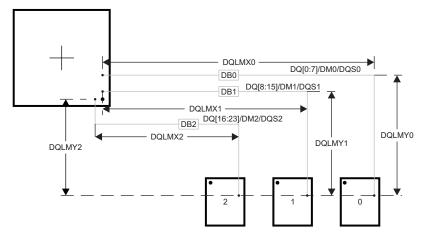

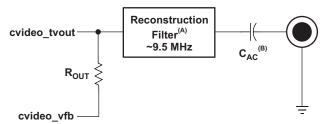

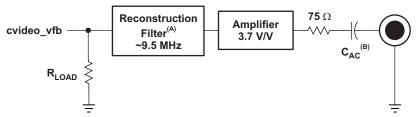

|                 |               | sysboot8<br>mcasp2_aclkr    | 15          | I        |                            |                                 |                                      |                             |            |          |                        |                              |           |