16

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# H8/3694Group

## Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8 Family/H8/300H Tiny Series

| H8/3694N | HD64N3694G, | HD6483694G, |

|----------|-------------|-------------|

| H8/3694F | HD64F3694,  | HD64F3694G, |

| H8/3694  | HD6433694,  | HD6433694G, |

| H8/3693  | HD6433693,  | HD6433693G, |

| H8/3692  | HD6433692,  | HD6433692G, |

| H8/3691  | HD6433691,  | HD6433691G, |

| H8/3690  | HD6433690,  | HD6433690G  |

Hardware Manua

Rev.4.00 Revision Date: Mar. 18, 2004

RenesasTechnology www.renesas.com

Rev. 4.00, 03/04, page ii of xxviii

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

Renesas

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

Rev. 4.00, 03/04, page iii of xxviii

#### **General Precautions on Handling of Product**

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

- 2. Treatment of Unused Input Pins

- Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

- 3. Processing before Initialization

- Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately

- 4. Prohibition of Access to Undefined or Reserved Addresses

after the power supply has been turned on.

Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

## Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

Renesas

11. Index

Rev. 4.00, 03/04, page v of xxviii

## Preface

The H8/3694 Group are single-chip microcomputers made up of the high-speed H8/300H CPU employing Renesas Technology original architecture as their cores, and the peripheral functions required to configure a system. The H8/300H CPU has an instruction set that is compatible with the H8/300 CPU.

- Target Users: This manual was written for users who will be using the H8/3694 Group in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of the H8/3694 Group to the target users. Refer to the H8/300H Series Programming Manual for a detailed description of the instruction set.

Notes on reading this manual:

- In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

- In order to understand the details of the CPU's functions Read the H8/300H Series Programming Manual.

- In order to understand the details of a register when its name is known

Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 20, List of Registers.

Example: Bit order: The MSB is on the left and the LSB is on the right.

Notes:

When using the on-chip emulator (E10T) for H8/3694 program development and debugging, the following restrictions must be noted (the on-chip debugging emulator (E7) can also be used).

- 1. The  $\overline{\text{NMI}}$  pin is reserved for the E10T, and cannot be used.

- 2. Pins P85, P86, and P87 cannot be used. In order to use these pins, additional hardware must be provided on the user board.

- 3. Area H'7000 to H'7FFF is used by the E10T, and is not available to the user.

- 4. Area H'F780 to H'FB7F must on no account be accessed.

- 5. When the E10T is used, address breaks can be set as either available to the user or for use by the E10T. If address breaks are set as being used by the E10T, the address break control registers must not be accessed.

Rev. 4.00, 03/04, page vi of xxviii

- 6. When the E10T is used, NMI is an input/output pin (open-drain in output mode), P85 and P87 are input pins, and P86 is an output pin.

- Related Manuals: The latest versions of all related manuals are available from our web site. Please ensure you have the latest versions of all documents you require. http://www.renesas.com/eng/

H8/3694 Group manuals:

| Document Title                    | Document No. |

|-----------------------------------|--------------|

| H8/3694 Group Hardware Manual     | This manual  |

| H8/300H Series Programming Manual | ADE-602-053  |

User's manuals for development tools:

| Document Title                                                                                          | Document No. |

|---------------------------------------------------------------------------------------------------------|--------------|

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual                   | ADE-702-247  |

| H8S, H8/300 Series Simulator/Debugger User's Manual                                                     | ADE-702-282  |

| H8S, H8/300 Series High-Performance Embedded Workshop,<br>High-Performance Debugging Interface Tutorial | ADE-702-231  |

| High-Performance Embedded Workshop User's Manual                                                        | ADE-702-201  |

Application notes:

| Document Title                                               | Document No. |

|--------------------------------------------------------------|--------------|

| Single Power Supply F-ZTAT <sup>™</sup> On-Board Programming | ADE-502-055  |

Rev. 4.00, 03/04, page viii of xxviii

## Contents

| Secti    | on 1 (                 | Dverview1                                    |  |  |

|----------|------------------------|----------------------------------------------|--|--|

| 1.1      | Feature                | s1                                           |  |  |

| 1.2      | Internal Block Diagram |                                              |  |  |

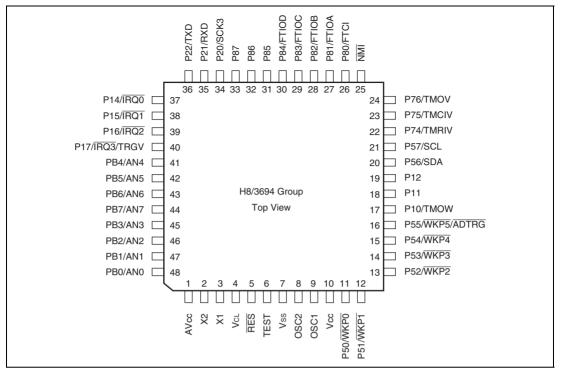

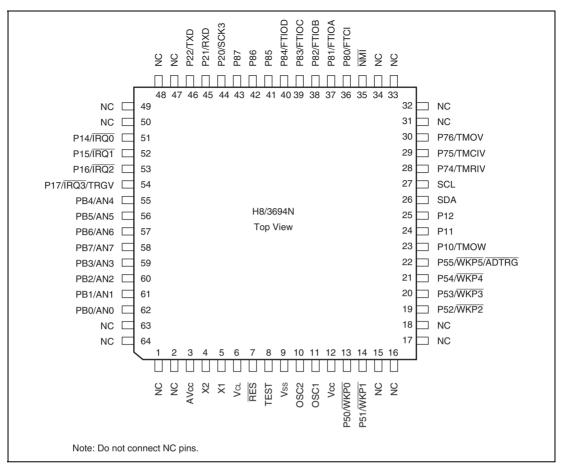

| 1.3      | Pin Arr                | angement                                     |  |  |

| 1.4      | Pin Fun                | actions                                      |  |  |

| <b>a</b> |                        |                                              |  |  |

|          |                        | CPU11                                        |  |  |

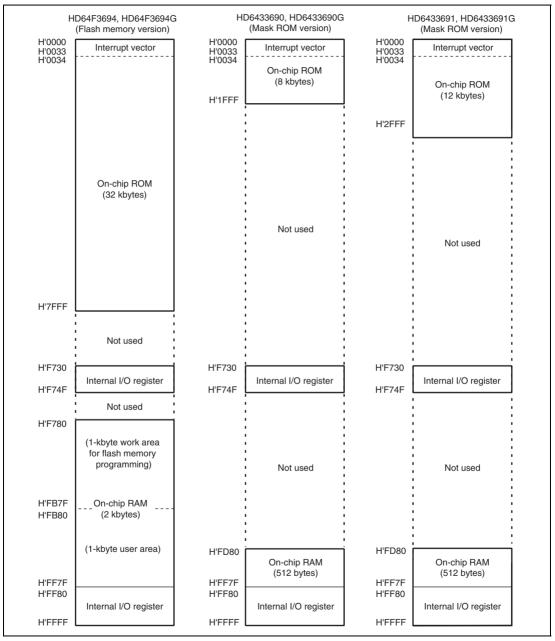

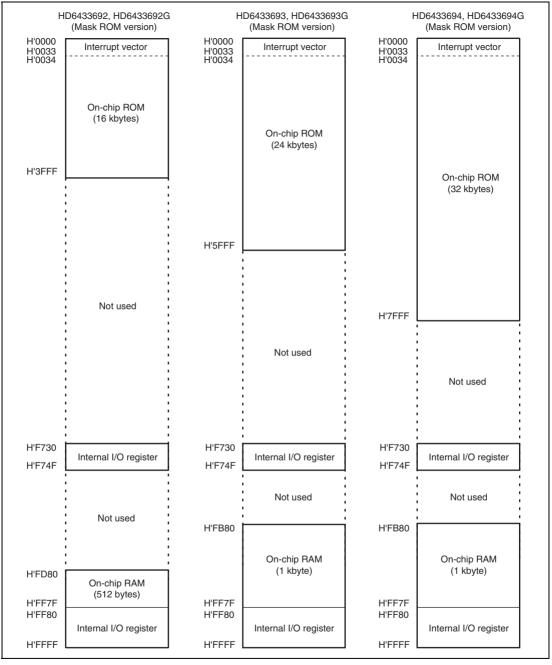

| 2.1      |                        | s Space and Memory Map12                     |  |  |

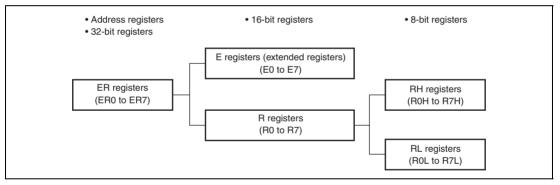

| 2.2      | 0                      | r Configuration15                            |  |  |

|          | 2.2.1                  | General Registers                            |  |  |

|          | 2.2.2                  | Program Counter (PC)                         |  |  |

|          | 2.2.3                  | Condition-Code Register (CCR)                |  |  |

| 2.3      | Data Fo                | ormats19                                     |  |  |

|          | 2.3.1                  | General Register Data Formats                |  |  |

|          | 2.3.2                  | Memory Data Formats                          |  |  |

| 2.4      | Instruct               | ion Set                                      |  |  |

|          | 2.4.1                  | Table of Instructions Classified by Function |  |  |

|          | 2.4.2                  | Basic Instruction Formats                    |  |  |

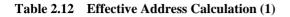

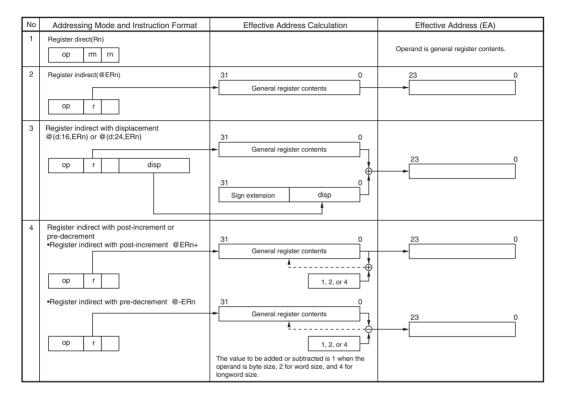

| 2.5      | Address                | sing Modes and Effective Address Calculation |  |  |

|          | 2.5.1                  | Addressing Modes                             |  |  |

|          | 2.5.2                  | Effective Address Calculation                |  |  |

| 2.6      | Basic B                | us Cycle                                     |  |  |

|          | 2.6.1                  | Access to On-Chip Memory (RAM, ROM)          |  |  |

|          | 2.6.2                  | On-Chip Peripheral Modules                   |  |  |

| 2.7      | CPU St                 | ates                                         |  |  |

| 2.8      | Usage I                | Notes                                        |  |  |

|          | 2.8.1                  | Notes on Data Access to Empty Areas          |  |  |

|          | 2.8.2                  | EEPMOV Instruction                           |  |  |

|          | 2.8.3                  | Bit Manipulation Instruction                 |  |  |

|          |                        |                                              |  |  |

| Secti    |                        | Exception Handling47                         |  |  |

| 3.1      | -                      | on Sources and Vector Address47              |  |  |

| 3.2      | Registe                | r Descriptions                               |  |  |

|          | 3.2.1                  | Interrupt Edge Select Register 1 (IEGR1)     |  |  |

|          | 3.2.2                  | Interrupt Edge Select Register 2 (IEGR2)     |  |  |

|          | 3.2.3                  | Interrupt Enable Register 1 (IENR1)          |  |  |

|          | 3.2.4                  | Interrupt Flag Register 1 (IRR1)             |  |  |

|          | 3.2.5                  | Wakeup Interrupt Flag Register(IWPR)         |  |  |

| 3.3      | Reset E                | xception Handling54                          |  |  |

Rev. 4.00, 03/04, page ix of xxviii

| 3.4   | 3.4 Interrupt Exception Handling |                                            |     |

|-------|----------------------------------|--------------------------------------------|-----|

|       | 3.4.1                            | External Interrupts                        | 55  |

|       | 3.4.2                            | Internal Interrupts                        | 56  |

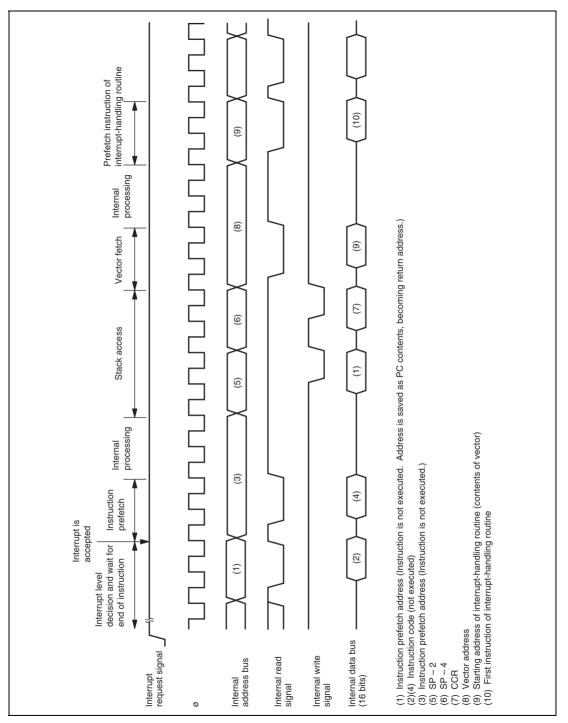

|       | 3.4.3                            | Interrupt Handling Sequence                | 56  |

|       | 3.4.4                            | Interrupt Response Time                    | 58  |

| 3.5   | Usage                            | Notes                                      | 60  |

|       | 3.5.1                            | Interrupts after Reset                     | 60  |

|       | 3.5.2                            | Notes on Stack Area Use                    | 60  |

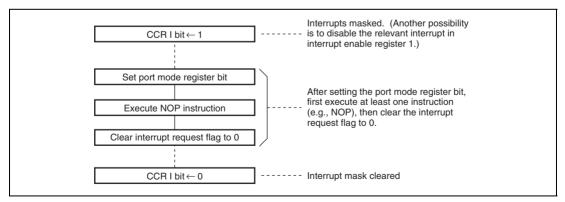

|       | 3.5.3                            | Notes on Rewriting Port Mode Registers     | 60  |

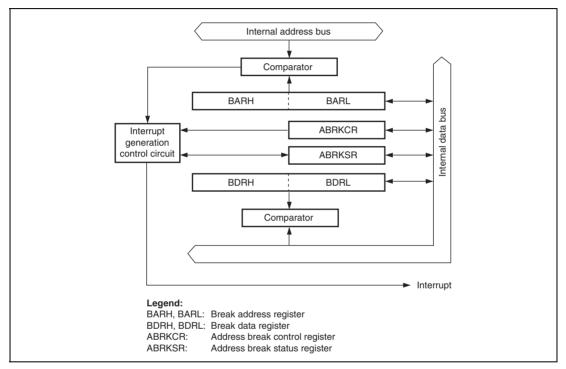

| Secti | on 4                             | Address Break                              | .61 |

| 4.1   |                                  | er Descriptions                            |     |

|       | 4.1.1                            | Address Break Control Register (ABRKCR)    |     |

|       | 4.1.2                            | Address Break Status Register (ABRKSR)     |     |

|       | 4.1.3                            | Break Address Registers (BARH, BARL)       |     |

|       | 4.1.4                            | Break Data Registers (BDRH, BDRL)          |     |

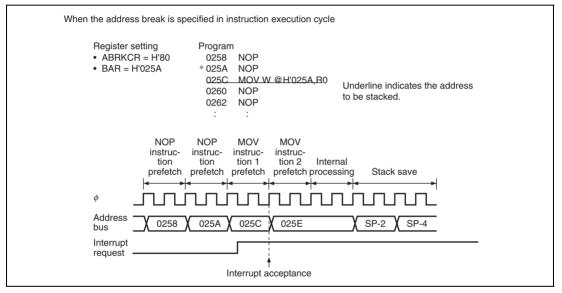

| 4.2   |                                  | ion                                        |     |

|       | operat                           |                                            | 0.  |

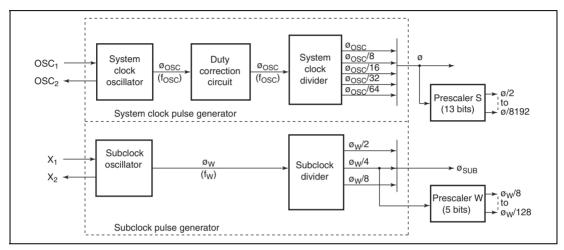

| Secti | on 5                             | Clock Pulse Generators                     | 67  |

| 5.1   | System                           | Clock Generator                            | 68  |

|       | 5.1.1                            | Connecting Crystal Resonator               | 68  |

|       | 5.1.2                            | Connecting Ceramic Resonator               | 69  |

|       | 5.1.3                            | External Clock Input Method                | 69  |

| 5.2   | Subclo                           | ck Generator                               | 70  |

|       | 5.2.1                            | Connecting 32.768-kHz Crystal Resonator    | 70  |

|       | 5.2.2                            | Pin Connection when Not Using Subclock     | 71  |

| 5.3   | Prescal                          | ers                                        | 71  |

|       | 5.3.1                            | Prescaler S                                | 71  |

|       | 5.3.2                            | Prescaler W                                | 71  |

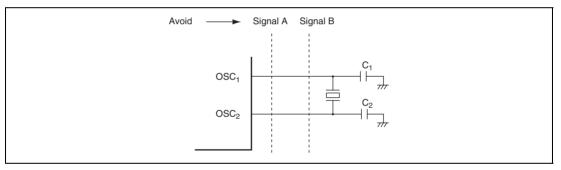

| 5.4   | Usage                            | Notes                                      | 72  |

|       | 5.4.1                            | Note on Resonators                         | 72  |

|       | 5.4.2                            | Notes on Board Design                      | 72  |

| Secti | on 6                             | Power-Down Modes                           | .73 |

| 6.1   |                                  | er Descriptions                            |     |

|       | 6.1.1                            | System Control Register 1 (SYSCR1)         |     |

|       | 6.1.2                            | System Control Register 2 (SYSCR2)         |     |

|       | 6.1.3                            | Module Standby Control Register 1 (MSTCR1) |     |

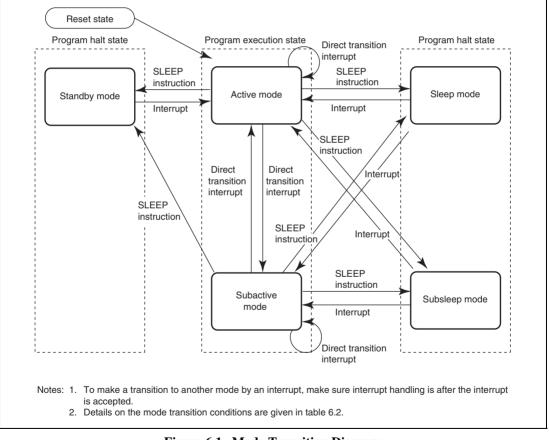

| 6.2   |                                  | Fransitions and States of LSI.             |     |

| ~     | 6.2.1                            | Sleep Mode                                 |     |

|       | 6.2.2                            | Standby Mode                               |     |

|       | 6.2.3                            | Subsleep Mode                              |     |

|       | 6.2.4                            | Subactive Mode                             |     |

| _     | ·                                |                                            |     |

| 6.3        | Operating Frequency in Active Mode                             |     |

|------------|----------------------------------------------------------------|-----|

| 6.4        | Direct Transition                                              |     |

|            | 6.4.1 Direct Transition from Active Mode to Subactive Mode     |     |

|            | 6.4.2 Direct Transition from Subactive Mode to Active Mode     |     |

| 6.5        | Module Standby Function                                        |     |

| <b>C</b> ( | · 7 DOM                                                        | 07  |

|            | ion 7 ROM                                                      |     |

| 7.1        | Block Configuration                                            |     |

| 7.2        | Register Descriptions                                          |     |

|            | 7.2.1 Flash Memory Control Register 1 (FLMCR1)                 |     |

|            | 7.2.2 Flash Memory Control Register 2 (FLMCR2)                 |     |

|            | 7.2.3 Erase Block Register 1 (EBR1)                            |     |

|            | 7.2.4 Flash Memory Power Control Register (FLPWCR)             |     |

|            | 7.2.5 Flash Memory Enable Register (FENR)                      |     |

| 7.3        | On-Board Programming Modes                                     |     |

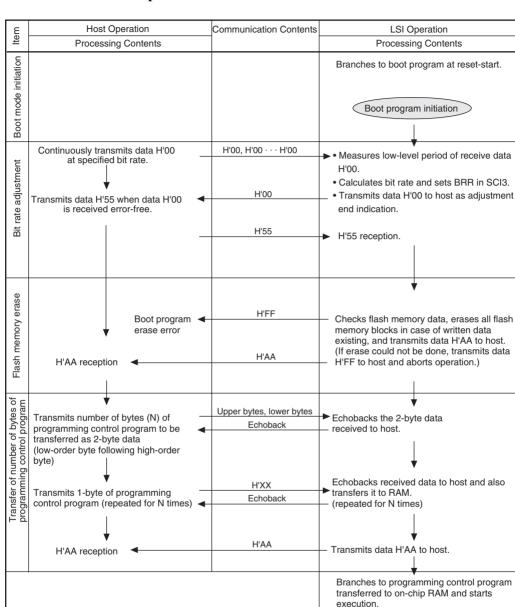

|            | 7.3.1 Boot Mode                                                |     |

|            | 7.3.2 Programming/Erasing in User Program Mode                 |     |

| 7.4        | Flash Memory Programming/Erasing                               |     |

|            | 7.4.1 Program/Program-Verify                                   |     |

|            | 7.4.2 Erase/Erase-Verify                                       |     |

|            | 7.4.3 Interrupt Handling when Programming/Erasing Flash Memory |     |

| 7.5        | Program/Erase Protection                                       |     |

|            | 7.5.1 Hardware Protection                                      |     |

|            | 7.5.2 Software Protection                                      |     |

|            | 7.5.3 Error Protection                                         |     |

| 7.6        | Programmer Mode                                                |     |

| 7.7        | Power-Down States for Flash Memory                             |     |

| Sect       | ion 8 RAM                                                      | 101 |

| Cast       |                                                                | 102 |

|            | ion 9 I/O Ports                                                |     |

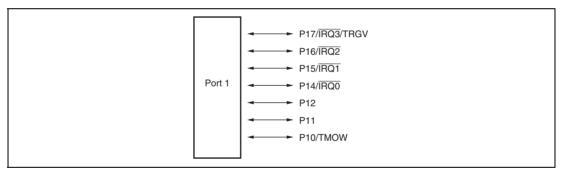

| 9.1        | Port 1                                                         |     |

|            | 9.1.1 Port Mode Register 1 (PMR1)                              |     |

|            | 9.1.2 Port Control Register 1 (PCR1)                           |     |

|            | 9.1.3 Port Data Register 1 (PDR1)                              |     |

|            | 9.1.4 Port Pull-Up Control Register 1 (PUCR1)                  |     |

|            | 9.1.5 Pin Functions                                            |     |

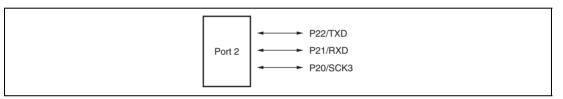

| 9.2        | Port 2                                                         |     |

|            | 9.2.1 Port Control Register 2 (PCR2)                           |     |

|            | 9.2.2 Port Data Register 2 (PDR2)                              |     |

|            | 9.2.3 Pin Functions                                            |     |

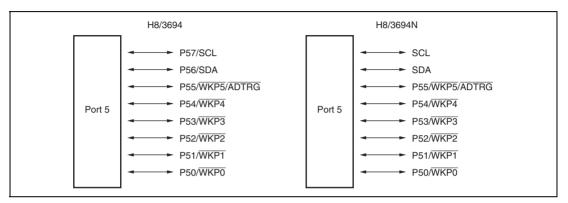

| 9.3        | Port 5                                                         |     |

|            | 9.3.1 Port Mode Register 5 (PMR5)                              |     |

|            |                                                                |     |

Rev. 4.00, 03/04, page xi of xxviii

|      | 9.3.2   | Port Control Register 5 (PCR5)                                                                              | 113 |

|------|---------|-------------------------------------------------------------------------------------------------------------|-----|

|      | 9.3.3   | Port Data Register 5 (PDR5)                                                                                 | 113 |

|      | 9.3.4   | Port Pull-Up Control Register 5 (PUCR5)                                                                     | 114 |

|      | 9.3.5   | Pin Functions                                                                                               | 114 |

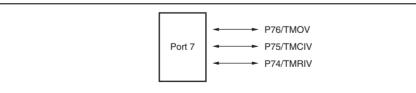

| 9.4  | Port 7. |                                                                                                             | 116 |

|      | 9.4.1   | Port Control Register 7 (PCR7)                                                                              | 117 |

|      | 9.4.2   | Port Data Register 7 (PDR7)                                                                                 | 117 |

|      | 9.4.3   | Pin Functions                                                                                               | 118 |

| 9.5  | Port 8. |                                                                                                             | 119 |

|      | 9.5.1   | Port Control Register 8 (PCR8)                                                                              | 119 |

|      | 9.5.2   | Port Data Register 8 (PDR8)                                                                                 | 120 |

|      | 9.5.3   | Pin Functions                                                                                               | 120 |

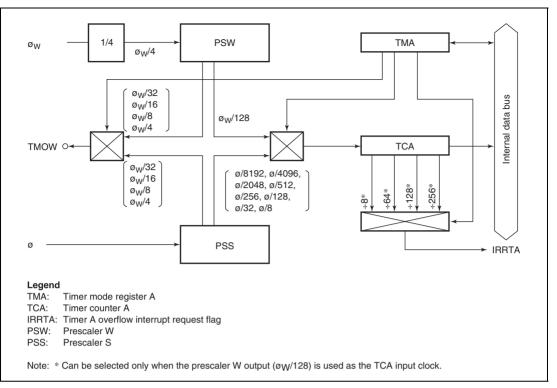

| 9.6  | Port B  |                                                                                                             | 123 |

|      | 9.6.1   | Port Data Register B (PDRB)                                                                                 | 123 |

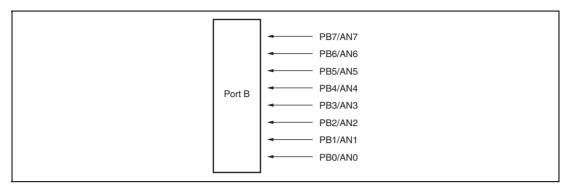

| Sect | ion 10  | Timer A                                                                                                     | 125 |

| 10.1 |         |                                                                                                             |     |

| 10.2 |         | Dutput Pins                                                                                                 |     |

| 10.3 | -       | er Descriptions                                                                                             |     |

|      | 10.3.1  | •                                                                                                           |     |

|      |         | Timer Counter A (TCA)                                                                                       |     |

| 10.4 |         | ion                                                                                                         |     |

|      | -       | Interval Timer Operation                                                                                    |     |

|      |         | Clock Time Base Operation                                                                                   |     |

|      |         | Clock Output                                                                                                |     |

| 10.5 |         | Note                                                                                                        |     |

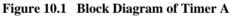

| Sect | ion 11  | Timer V                                                                                                     | 131 |

| 11.1 |         |                                                                                                             |     |

| 11.1 |         | Dutput Pins                                                                                                 |     |

| 11.2 | -       | er Descriptions                                                                                             |     |

| 11.5 | 11.3.1  | -                                                                                                           |     |

|      | 11.3.2  | Time Constant Registers A and B (TCORA, TCORB)                                                              |     |

|      | 11.3.3  | Timer Control Register V0 (TCRV0)                                                                           |     |

|      |         | Timer Control/Status Register V (TCSRV)                                                                     |     |

|      |         | Timer Control Register V1 (TCRV1)                                                                           |     |

| 11.4 |         | ion                                                                                                         |     |

| 11.4 | -       | Timer V Operation                                                                                           |     |

| 11.5 |         | V Application Examples                                                                                      |     |

| 11.3 |         | Pulse Output with Arbitrary Duty Cycle                                                                      |     |

|      |         | Pulse Output with Arbitrary Duty Cycle<br>Pulse Output with Arbitrary Pulse Width and Delay from TRGV Input |     |

| 11.6 |         |                                                                                                             |     |

| 11.0 | Usage   | Notes                                                                                                       | 143 |

Rev. 4.00, 03/04, page xii of xxviii

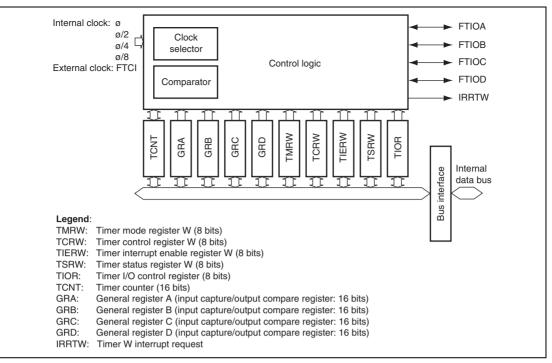

| Secti    | on 12   | Timer W                                              | 145  |

|----------|---------|------------------------------------------------------|------|

| 12.1     | Feature | S                                                    | 145  |

| 12.2     | Input/C | Output Pins                                          | 147  |

| 12.3     | Registe | r Descriptions                                       | 148  |

|          | 12.3.1  | Timer Mode Register W (TMRW)                         | 149  |

|          | 12.3.2  | Timer Control Register W (TCRW)                      | 150  |

|          | 12.3.3  | Timer Interrupt Enable Register W (TIERW)            | 151  |

|          | 12.3.4  | Timer Status Register W (TSRW)                       | 152  |

|          | 12.3.5  | Timer I/O Control Register 0 (TIOR0)                 | 153  |

|          |         | Timer I/O Control Register 1 (TIOR1)                 |      |

|          | 12.3.7  | Timer Counter (TCNT)                                 | 156  |

|          | 12.3.8  | General Registers A to D (GRA to GRD)                | 156  |

| 12.4     | Operati | on                                                   | 157  |

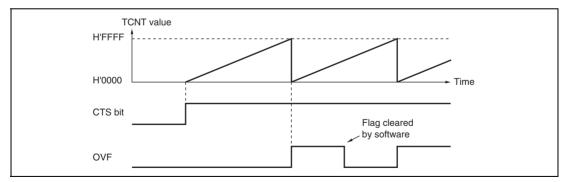

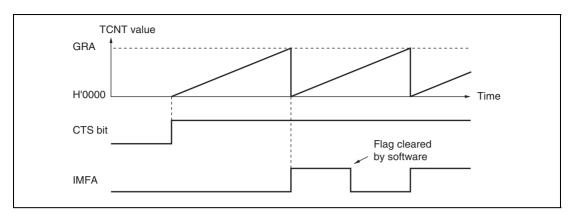

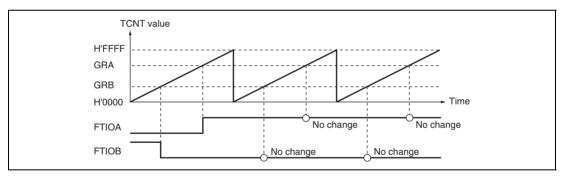

|          | 12.4.1  | Normal Operation                                     | 157  |

|          |         | PWM Operation                                        |      |

| 12.5     | Operati | on Timing                                            | 165  |

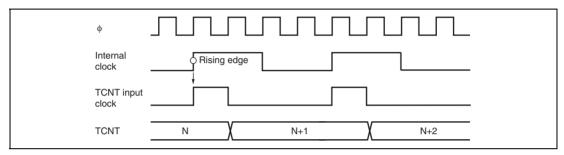

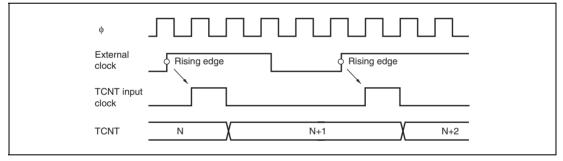

|          |         | TCNT Count Timing                                    |      |

|          | 12.5.2  | Output Compare Output Timing                         | 165  |

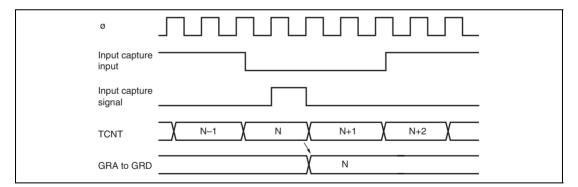

|          | 12.5.3  | Input Capture Timing                                 | 166  |

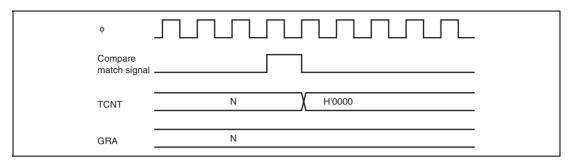

|          | 12.5.4  | Timing of Counter Clearing by Compare Match          | 167  |

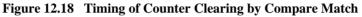

|          | 12.5.5  | Buffer Operation Timing                              | 167  |

|          | 12.5.6  | Timing of IMFA to IMFD Flag Setting at Compare Match |      |

|          | 12.5.7  | Timing of IMFA to IMFD Setting at Input Capture      |      |

|          | 12.5.8  | Timing of Status Flag Clearing                       | 169  |

| 12.6     | Usage 1 | Notes                                                | 170  |

| <b>c</b> | 10      |                                                      | 170  |

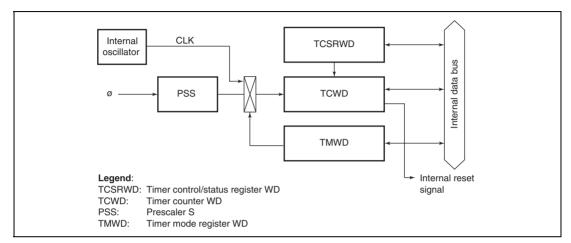

|          |         | Watchdog Timer                                       |      |

| 13.1     |         | s                                                    |      |

| 13.2     | -       | r Descriptions                                       |      |

|          |         | Timer Control/Status Register WD (TCSRWD)            |      |

|          |         | Timer Counter WD (TCWD)                              |      |

| 10.0     |         | Timer Mode Register WD (TMWD)                        |      |

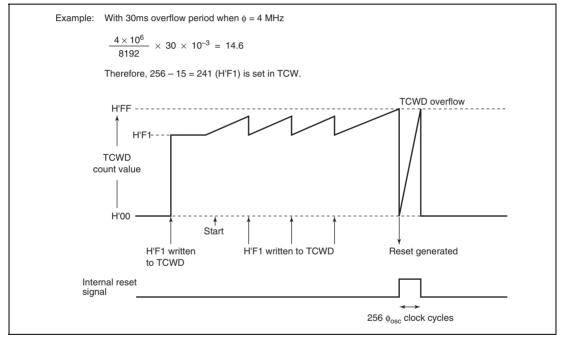

| 13.3     | Operati | on                                                   | 177  |

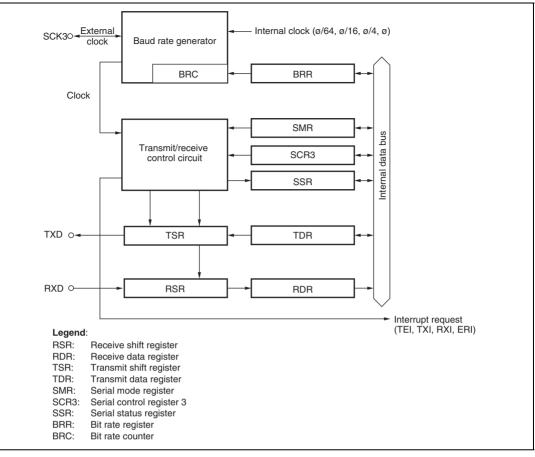

| Secti    | on 14   | Serial Communication Interface3 (SCI3)               | 179  |

| 14.1     |         | s                                                    |      |

| 14.2     |         | Output Pins                                          |      |

| 14.3     |         | r Descriptions                                       |      |

| 1 1.5    |         | Receive Shift Register (RSR)                         |      |

|          |         | Receive Data Register (RDR)                          |      |

|          | 14.3.3  | Transmit Shift Register (TSR)                        |      |

|          | 14.3.4  | -                                                    |      |

|          | 14.3.5  | -                                                    |      |

|          | 1 1.5.5 |                                                      | - 05 |

Rev. 4.00, 03/04, page xiii of xxviii

|       | 14.3.6  | Serial Control Register 3 (SCR3)                       | . 184 |

|-------|---------|--------------------------------------------------------|-------|

|       | 14.3.7  | Serial Status Register (SSR)                           | 186   |

|       | 14.3.8  | Bit Rate Register (BRR)                                | . 188 |

| 14.4  | Operati | ion in Asynchronous Mode                               | . 195 |

|       | 14.4.1  | Clock                                                  | 195   |

|       | 14.4.2  | SCI3 Initialization                                    | . 196 |

|       | 14.4.3  | Data Transmission                                      | . 197 |

|       | 14.4.4  | Serial Data Reception                                  | 199   |

| 14.5  | Operati | on in Clocked Synchronous Mode                         | 203   |

|       | 14.5.1  | Clock                                                  | 203   |

|       | 14.5.2  | SCI3 Initialization                                    | 203   |

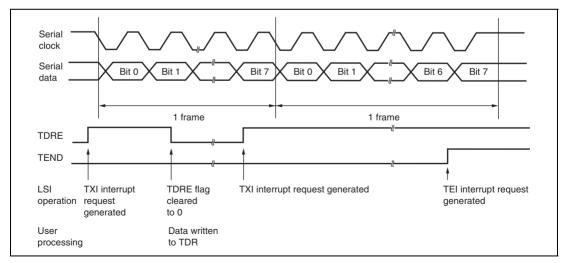

|       | 14.5.3  | Serial Data Transmission                               | 204   |

|       | 14.5.4  | Serial Data Reception (Clocked Synchronous Mode)       | 206   |

|       | 14.5.5  | Simultaneous Serial Data Transmission and Reception    | 208   |

| 14.6  | Multip  | rocessor Communication Function                        | 210   |

|       | 14.6.1  | Multiprocessor Serial Data Transmission                | 211   |

|       | 14.6.2  | Multiprocessor Serial Data Reception                   | .212  |

| 14.7  | Interru | pts                                                    | 216   |

| 14.8  | Usage   | Notes                                                  | 217   |

|       | 14.8.1  | Break Detection and Processing                         | 217   |

|       | 14.8.2  | Mark State and Break Sending                           | 217   |

|       | 14.8.3  | Receive Error Flags and Transmit Operations            |       |

|       |         | (Clocked Synchronous Mode Only)                        | 217   |

|       | 14.8.4  | Receive Data Sampling Timing                           |       |

|       |         | and Reception Margin in Asynchronous Mode              | .218  |

| Secti | ion 15  | I <sup>2</sup> C Bus Interface 2 (IIC2)                | 219   |

| 15.1  |         | S                                                      |       |

| 15.2  |         | Dutput Pins                                            |       |

| 15.3  | -       | er Descriptions                                        |       |

| 15.5  | -       | I <sup>2</sup> C Bus Control Register 1 (ICCR1)        |       |

|       |         | I <sup>2</sup> C Bus Control Register 2 (ICCR2)        |       |

|       |         | I <sup>2</sup> C Bus Mode Register (ICMR)              |       |

|       |         | I <sup>2</sup> C Bus Interrupt Enable Register (ICIER) |       |

|       |         | I <sup>2</sup> C Bus Status Register (ICSR)            |       |

|       |         | Slave Address Register (SAR)                           |       |

|       |         | I <sup>2</sup> C Bus Transmit Data Register (ICDRT)    |       |

|       |         | I <sup>2</sup> C Bus Receive Data Register (ICDRF)     |       |

|       |         | I <sup>2</sup> C Bus Shift Register (ICDRS)            |       |

| 15.4  |         | ion                                                    |       |

| 1.5.4 | -       | I <sup>2</sup> C Bus Format                            |       |

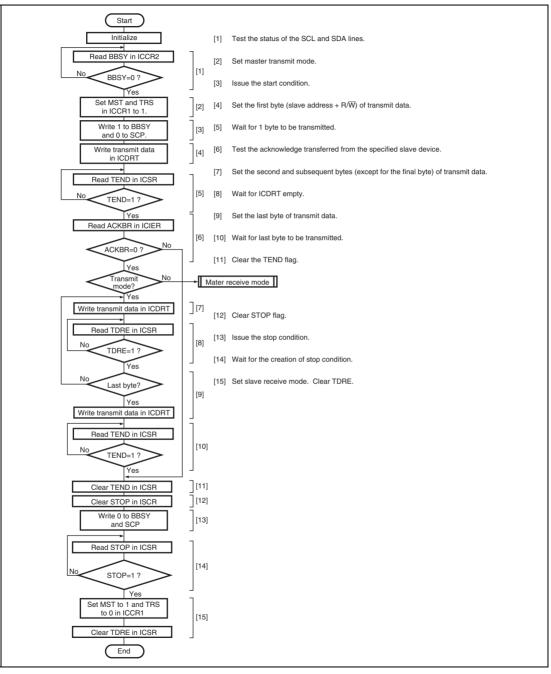

|       |         | Master Transmit Operation                              |       |

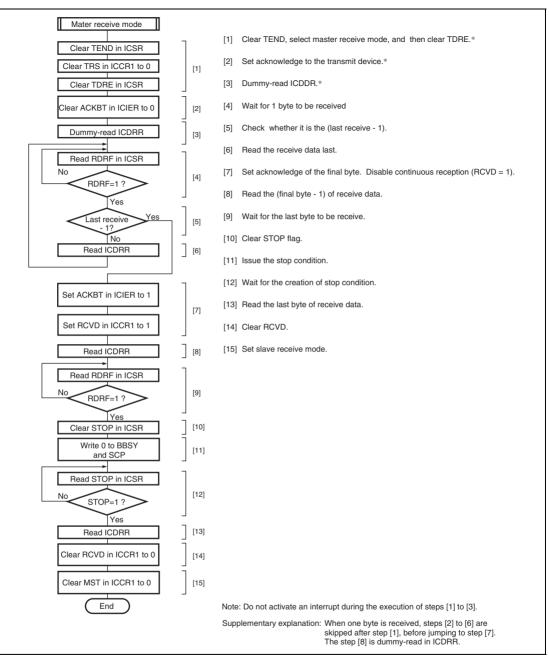

|       |         | Master Receive Operation                               |       |

|       | 1.7.4)  |                                                        | . 200 |

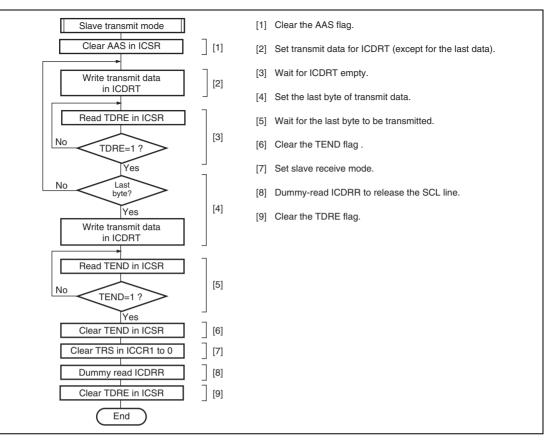

|      | 15.4.4  | Slave Transmit Operation                   | .238  |

|------|---------|--------------------------------------------|-------|

|      | 15.4.5  | Slave Receive Operation                    | .240  |

|      | 15.4.6  | Clocked Synchronous Serial Format          | .242  |

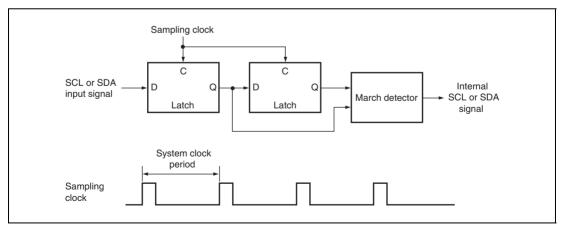

|      | 15.4.7  | Noise Canceler                             | .244  |

|      | 15.4.8  | Example of Use                             | . 245 |

| 15.5 | Interru | pt Request                                 | . 249 |

| 15.6 | Bit Syr | nchronous Circuit                          | .250  |

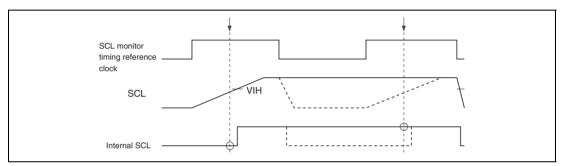

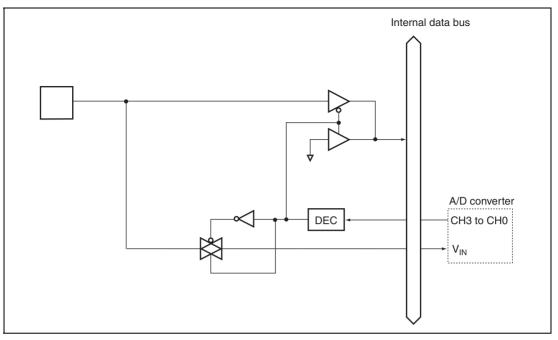

| Sect | ion 16  | A/D Converter                              | .251  |

| 16.1 |         | 28                                         |       |

| 16.2 | -       | Dutput Pins                                |       |

| 16.3 | -       | er Descriptions                            |       |

|      | 16.3.1  | A/D Data Registers A to D (ADDRA to ADDRD) | .254  |

|      |         | A/D Control/Status Register (ADCSR)        |       |

|      | 16.3.3  | A/D Control Register (ADCR)                | .256  |

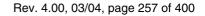

| 16.4 | Operat  | ion                                        | .257  |

|      | 16.4.1  | Single Mode                                | .257  |

|      | 16.4.2  | Scan Mode                                  | .257  |

|      | 16.4.3  | Input Sampling and A/D Conversion Time     | .258  |

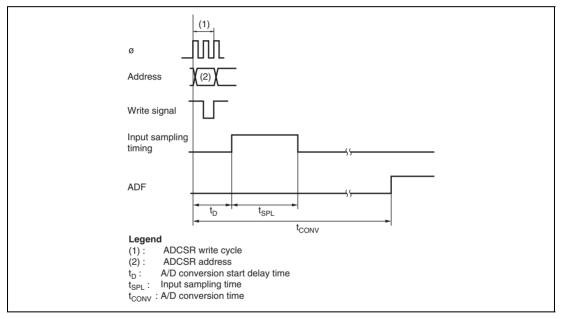

|      | 16.4.4  | External Trigger Input Timing              | . 259 |

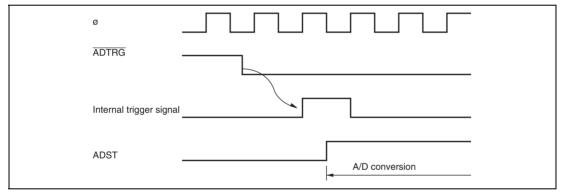

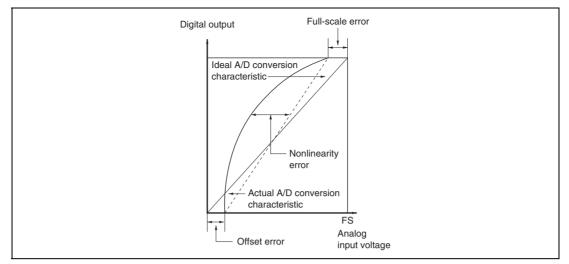

| 16.5 | A/D Co  | onversion Accuracy Definitions             | .260  |

| 16.6 | Usage   | Notes                                      | .261  |

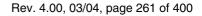

|      | 16.6.1  | Permissible Signal Source Impedance        | .261  |

|      | 16.6.2  | Influences on Absolute Accuracy            | .261  |

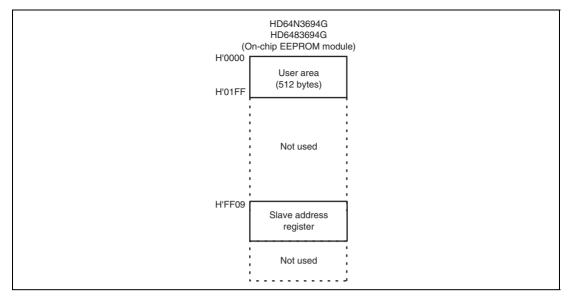

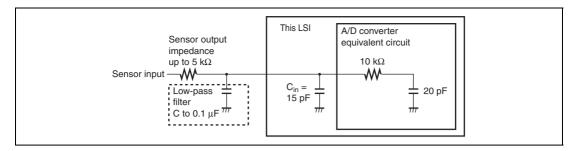

| Sect | ion 17  | EEPROM                                     | .263  |

| 17.1 | Feature | 25                                         | .263  |

| 17.2 | Input/C | Dutput Pins                                | .265  |

| 17.3 | Registe | er Description                             | . 265 |

|      | 17.3.1  | EEPROM Key Register (EKR)                  | .265  |

| 17.4 | Operat  | ion                                        | .266  |

|      | 17.4.1  | EEPROM Interface                           | . 266 |

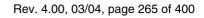

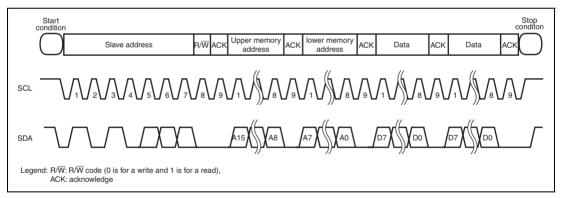

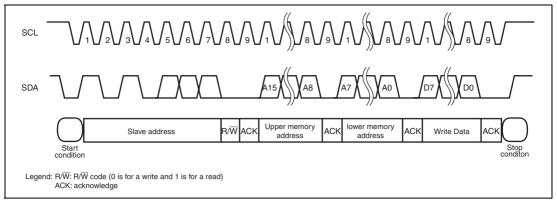

|      | 17.4.2  | Bus Format and Timing                      | . 266 |

|      | 17.4.3  | Start Condition                            | .266  |

|      | 17.4.4  | Stop Condition                             | .267  |

|      | 17.4.5  | Acknowledge                                | .267  |

|      |         | Slave Addressing                           |       |

|      | 17.4.7  | Write Operations                           | .268  |

|      | 17.4.8  | Acknowledge Polling                        |       |

|      | 17.4.9  | Read Operation                             |       |

| 17.5 |         | Notes                                      |       |

|      |         | Data Protection at V <sub>cc</sub> On/Off  |       |

|      |         | Write/Erase Endurance                      |       |

|      |         |                                            |       |

Rev. 4.00, 03/04, page xv of xxviii

|        | 17.5.3        | Noise Suppression Time                                               | . 273 |

|--------|---------------|----------------------------------------------------------------------|-------|

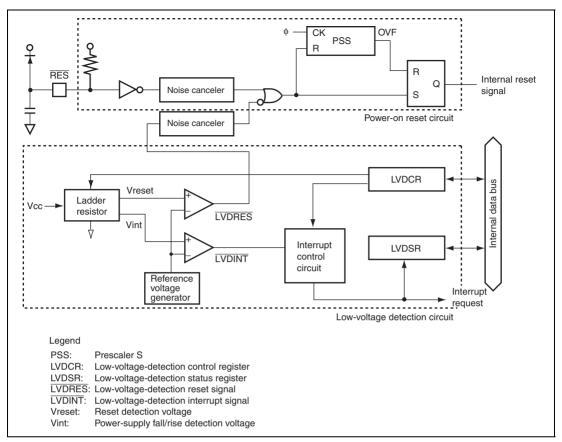

| Secti  | on 18         | Power-On Reset and Low-Voltage Detection Circuits (Optional)         | .275  |

| 18.1   |               | 8                                                                    |       |

| 18.2   |               | r Descriptions                                                       |       |

|        | -             | Low-Voltage-Detection Control Register (LVDCR)                       |       |

|        |               | Low-Voltage-Detection Status Register (LVDSR)                        |       |

| 18.3   |               | on                                                                   |       |

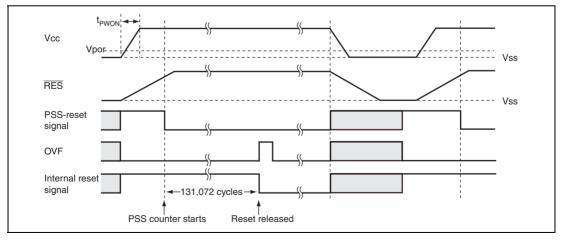

|        | 1             | Power-On Reset Circuit                                               |       |

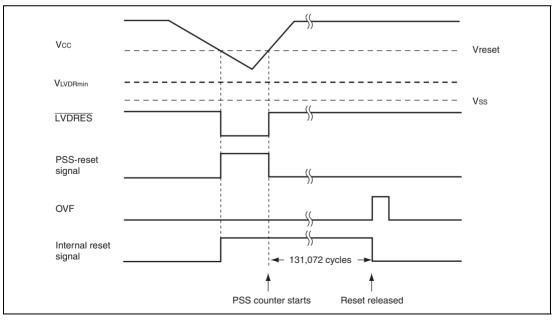

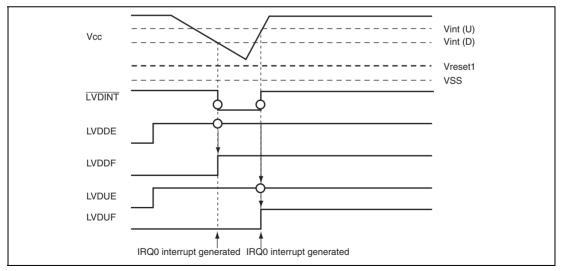

|        |               | Low-Voltage Detection Circuit                                        |       |

| Secti  | on 19         | Power Supply Circuit                                                 | .283  |

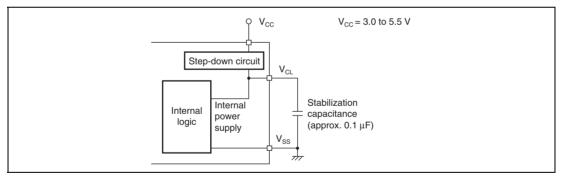

| 19.1   |               | Jsing Internal Power Supply Step-Down Circuit                        |       |

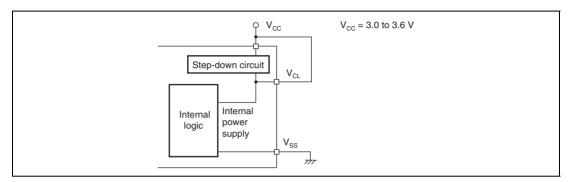

| 19.2   |               | Not Using Internal Power Supply Step Down Circuit                    |       |

| 17.2   | When I        | to come internal rower supply step Down cheattanning                 | 201   |

| Secti  | on 20         | List of Registers                                                    | 285   |

| 20.1   |               | r Addresses (Address Order)                                          |       |

| 20.1   | -             | r Bits                                                               |       |

| 20.2   | -             | rs States in Each Operating Mode                                     |       |

| Saati  | on <b>7</b> 1 | Electrical Characteristics                                           | 207   |

|        |               |                                                                      |       |

| 21.1   |               | te Maximum Ratings                                                   | . 297 |

| 21.2   |               | cal Characteristics $TTM V_{\text{resident}}$                        | 207   |

|        |               | AT <sup>™</sup> Version, EEPROM Stacked F-ZTAT <sup>™</sup> Version) |       |

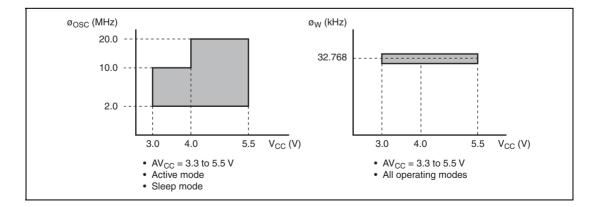

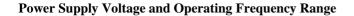

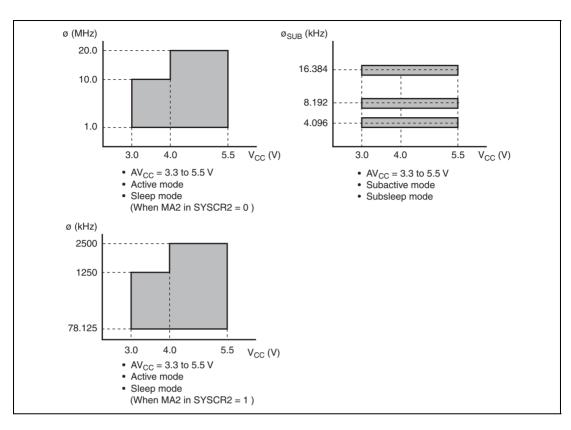

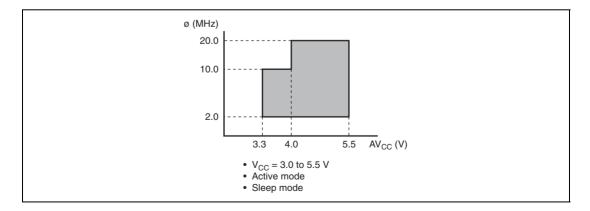

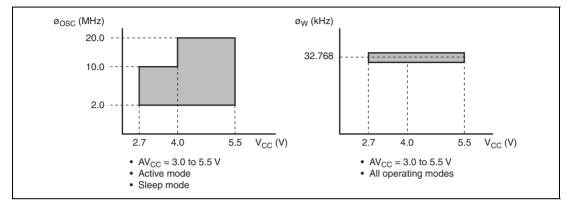

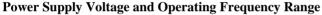

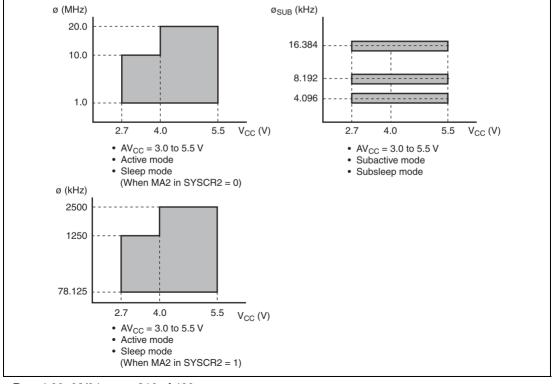

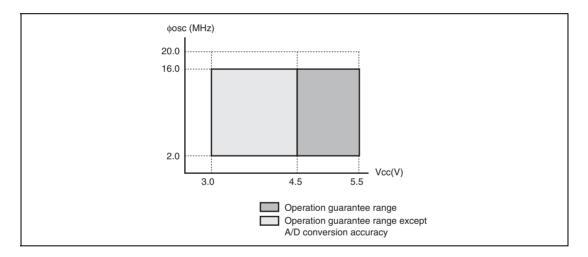

|        |               | Power Supply Voltage and Operating Ranges                            |       |

|        |               | DC Characteristics                                                   |       |

|        |               | AC Characteristics                                                   |       |

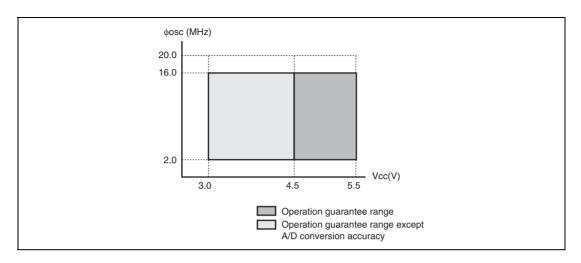

|        |               | A/D Converter Characteristics                                        |       |

|        |               | Watchdog Timer Characteristics                                       |       |

|        |               | Flash Memory Characteristics                                         |       |

|        |               | EEPROM Characteristics                                               |       |

|        |               | Power-Supply-Voltage Detection Circuit Characteristics (Optional)    |       |

|        |               | Power-On Reset Circuit Characteristics (Optional)                    | . 315 |

| 21.3   |               | cal Characteristics                                                  |       |

|        |               | ROM Version, EEPROM Stacked Mask-ROM Version)                        |       |

|        |               | Power Supply Voltage and Operating Ranges                            |       |

|        |               | DC Characteristics                                                   |       |

|        | 21.3.3        | AC Characteristics                                                   |       |

|        | 21.3.4        |                                                                      |       |

|        | 21.3.5        | e                                                                    |       |

|        |               | EEPROM Characteristics                                               |       |

|        |               | Power-Supply-Voltage Detection Circuit Characteristics (Optional)    |       |

|        | 21.3.8        | Power-On Reset Circuit Characteristics (Optional)                    | . 330 |

| Rev. 4 | 1.00, 03/     | 04, page xvi of xxviii                                               |       |

| 21.4  | Operation Timing                                      | 331 |

|-------|-------------------------------------------------------|-----|

|       | Output Load Condition                                 |     |

|       |                                                       |     |

| Appe  | endix A Instruction Set                               | 335 |

| A.1   | Instruction List                                      | 335 |

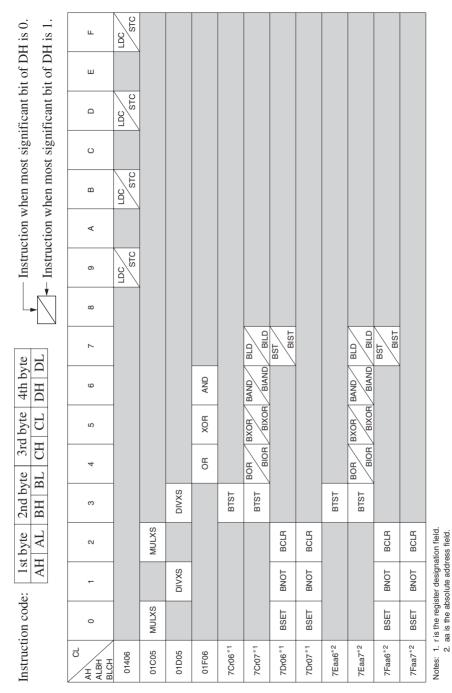

| A.2   | Operation Code Map                                    | 350 |

| A.3   | Number of Execution States                            |     |

| A.4   | Combinations of Instructions and Addressing Modes     | 364 |

|       |                                                       |     |

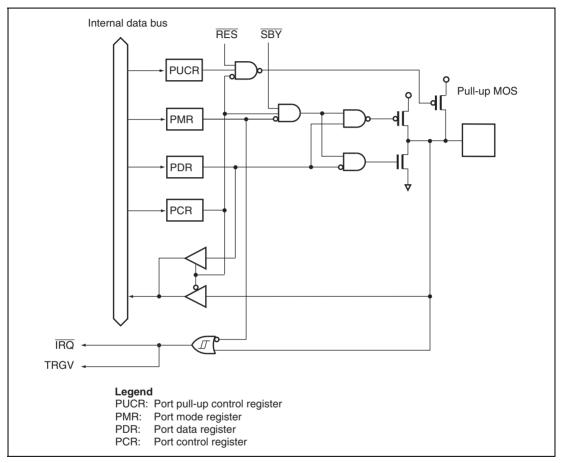

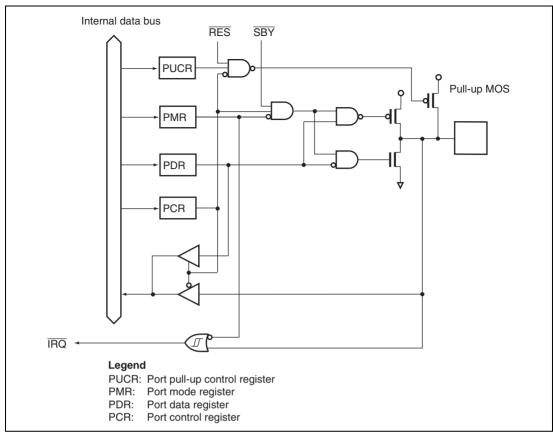

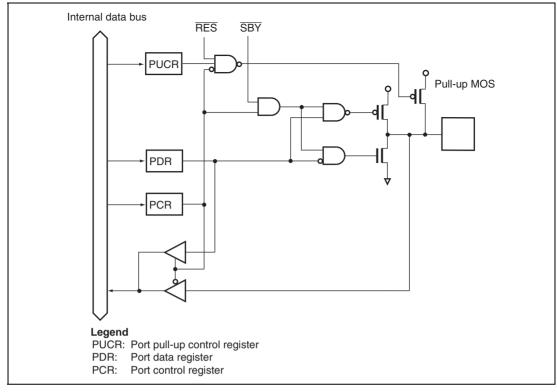

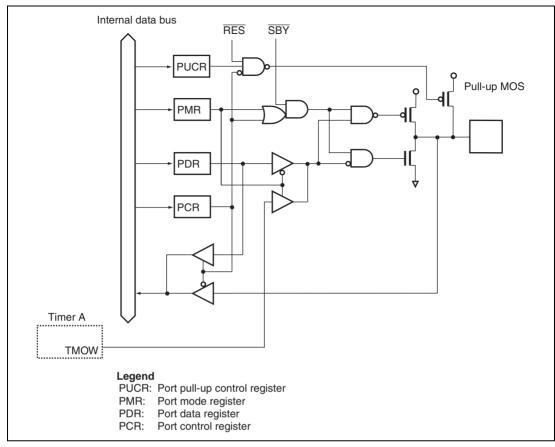

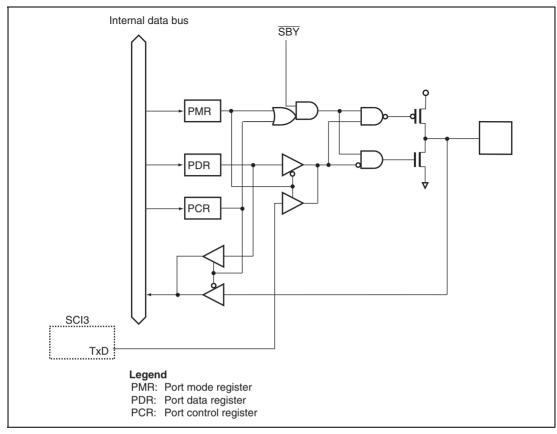

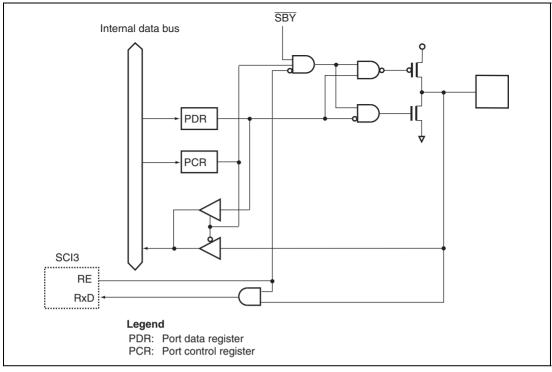

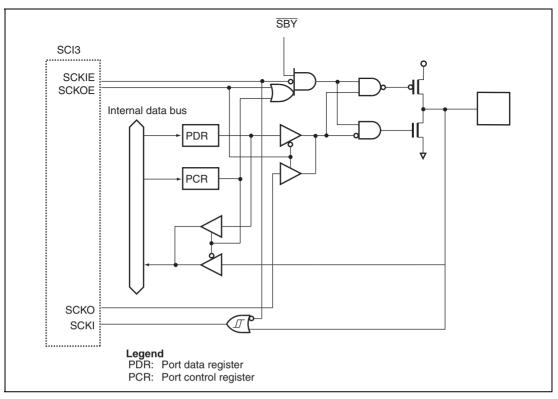

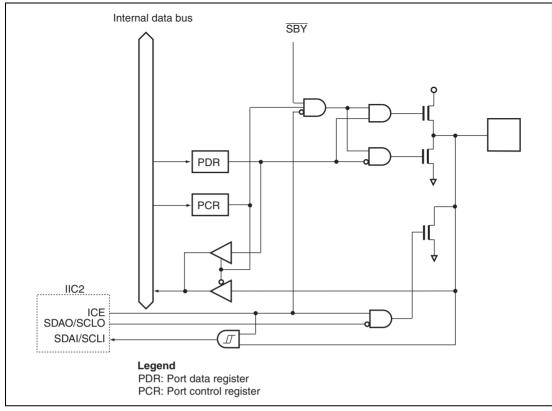

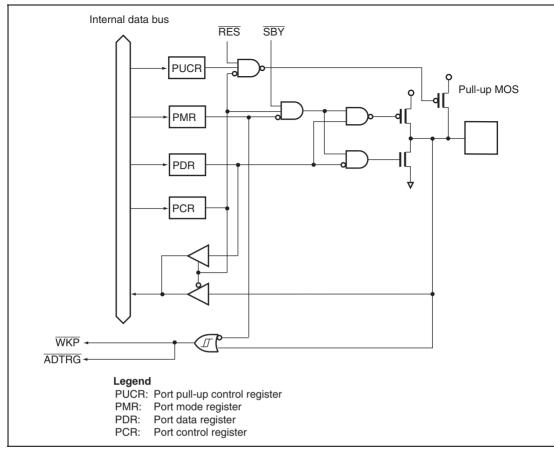

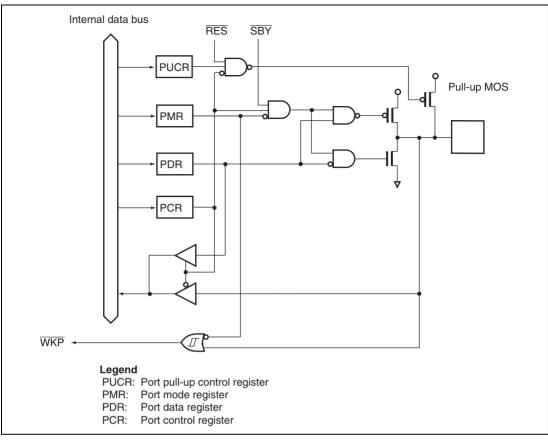

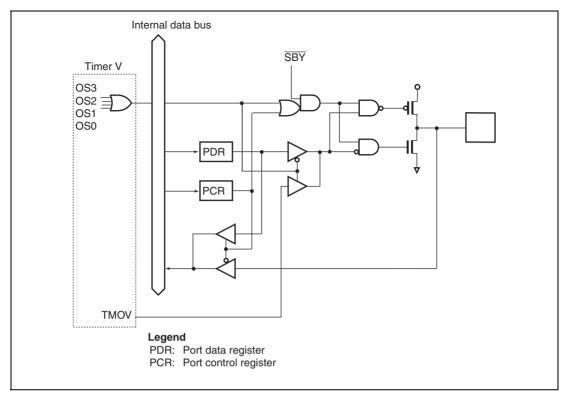

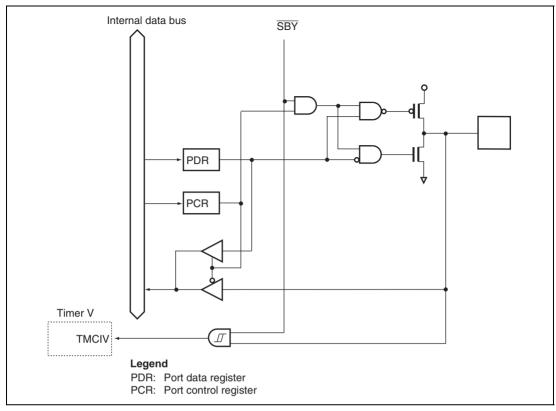

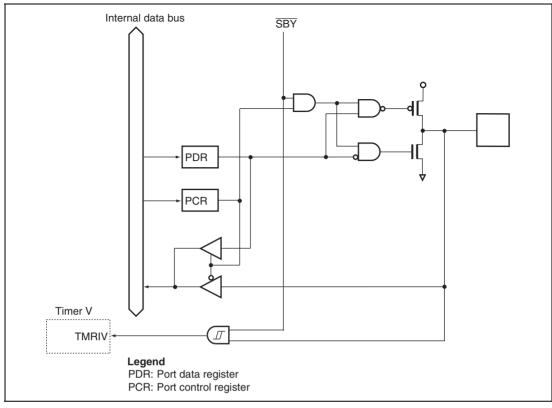

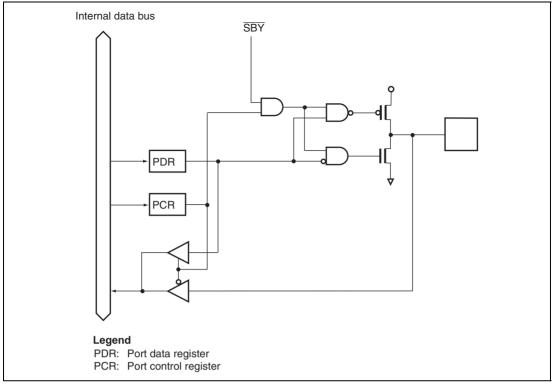

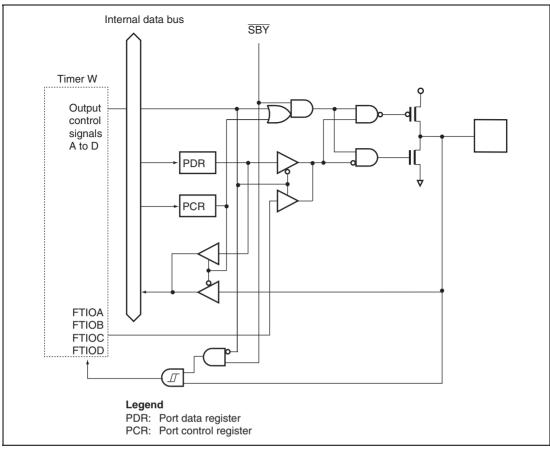

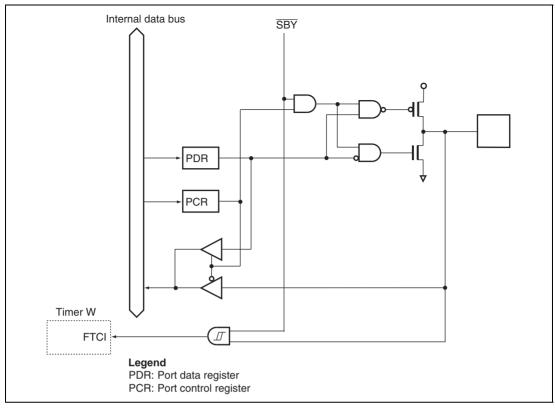

| Appe  | endix B I/O Port Block Diagrams                       | 365 |

| B.1   | I/O Port Block Diagrams                               | 365 |

| B.2   | Port States in Each Operating State                   | 381 |

|       |                                                       |     |

| Appe  | endix C Product Code Lineup                           | 382 |

|       |                                                       |     |

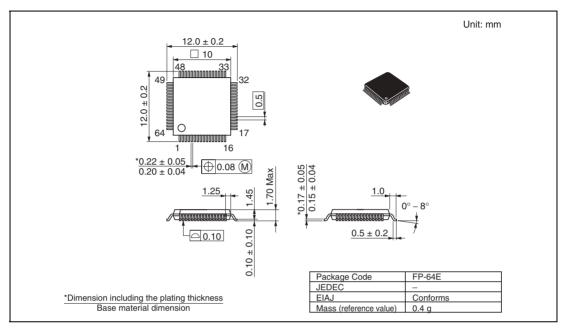

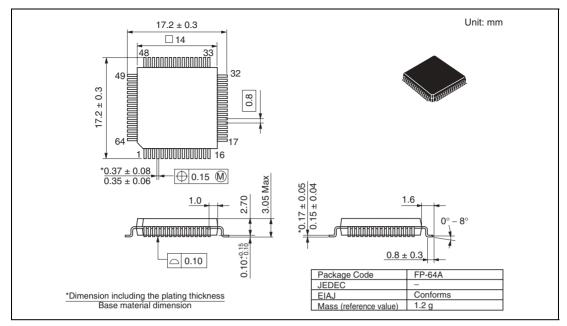

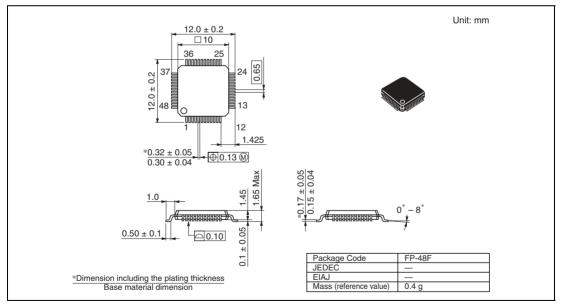

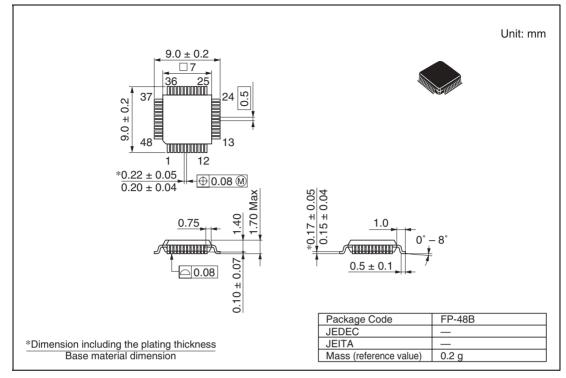

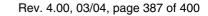

| Appe  | endix D Package Dimensions                            | 385 |

|       |                                                       |     |

| Appe  | endix E EEPROM Stacked-Structure Cross-Sectional View | 389 |

|       |                                                       |     |

| Mair  | n Revisions and Additions in this Edition             | 391 |

|       |                                                       |     |

| Index | X                                                     | 397 |

Rev. 4.00, 03/04, page xviii of xxviii

## Figures

| Section 1   |                                                                                 |    |

|-------------|---------------------------------------------------------------------------------|----|

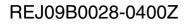

| Figure 1.1  | Internal Block Diagram of H8/3694 Group of $F$ -ZTAT <sup>TM</sup> and Mask-ROM |    |

|             | Versions                                                                        |    |

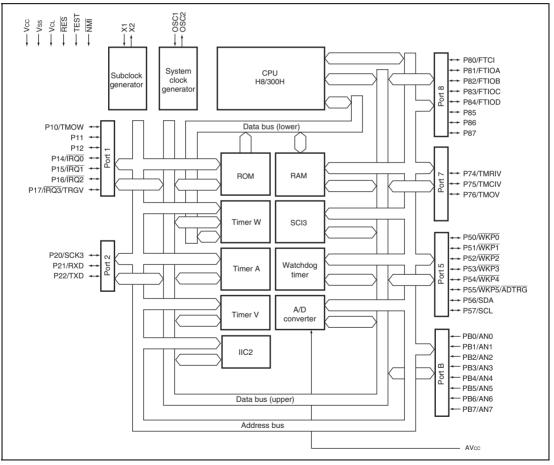

|             | Internal Block Diagram of H8/3694N (EEPROM Stacked Version)                     | 4  |

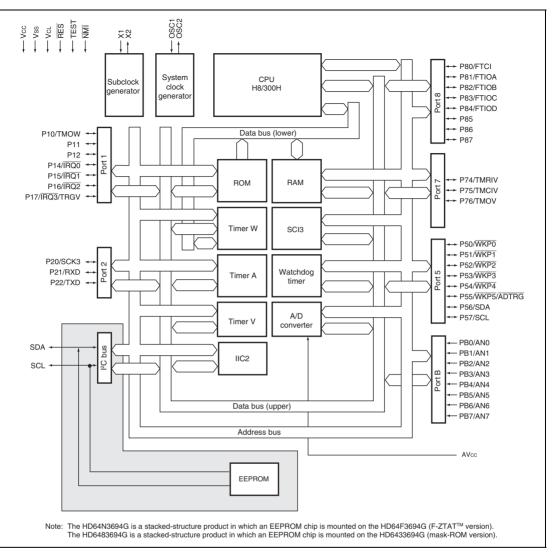

| Figure 1.3  | Pin Arrangement of H8/3694 Group of F-ZTAT <sup>TM</sup> and Mask-ROM Versions  |    |

|             | (FP-64E, FP-64A)                                                                | 5  |

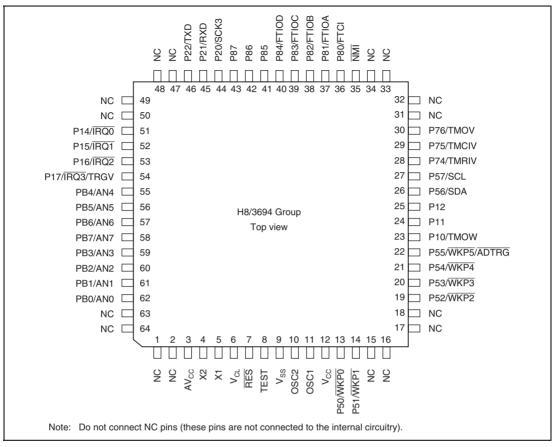

| Figure 1.4  | Pin Arrangement of H8/3694 Group of F-ZTAT <sup>TM</sup> and Mask-ROM Versions  |    |

|             | (FP-48F, FP-48B, TNP-48)                                                        |    |

| Figure 1.5  | Pin Arrangement of H8/3694N (EEPROM Stacked Version) (FP-64E)                   | 7  |

| Section 2   | СРИ                                                                             |    |

| Figure 2.1  | Memory Map (1)                                                                  | 12 |

| Figure 2.1  | Memory Map (2)                                                                  | 13 |

| Figure 2.1  | Memory Map (3)                                                                  | 14 |

| Figure 2.2  | CPU Registers                                                                   | 15 |

| Figure 2.3  | Usage of General Registers                                                      | 16 |

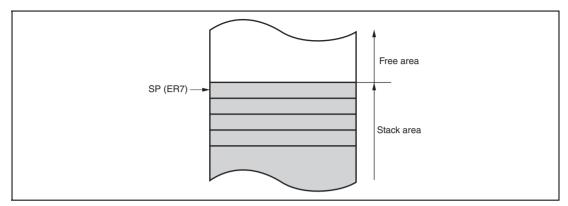

| Figure 2.4  | Relationship between Stack Pointer and Stack Area                               | 17 |

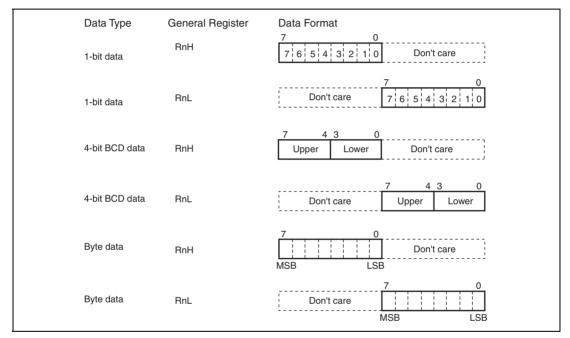

| Figure 2.5  | General Register Data Formats (1)                                               | 19 |

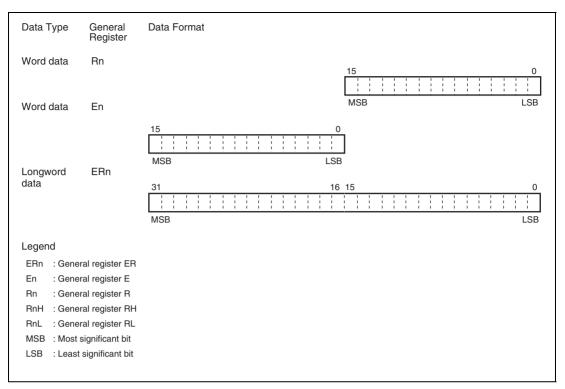

| Figure 2.5  | General Register Data Formats (2)                                               | 20 |

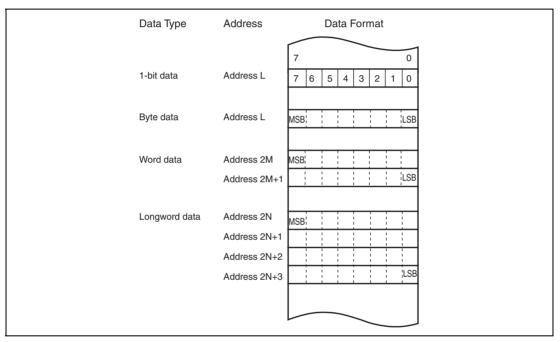

| Figure 2.6  | Memory Data Formats                                                             | 21 |

| Figure 2.7  | Instruction Formats                                                             | 32 |

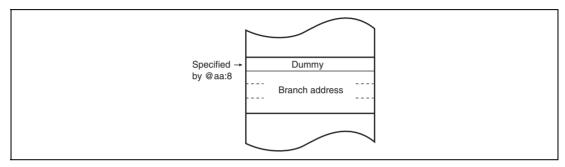

| Figure 2.8  | Branch Address Specification in Memory Indirect Mode                            | 35 |

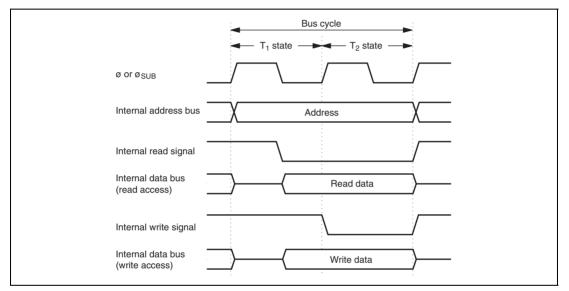

| Figure 2.9  | On-Chip Memory Access Cycle                                                     | 38 |

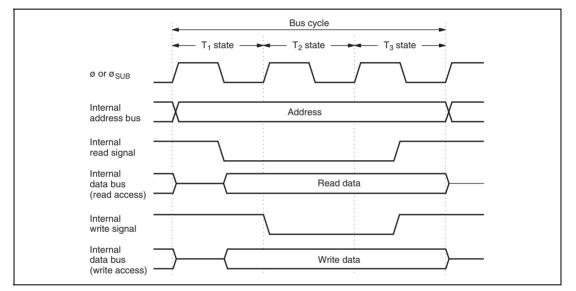

| Figure 2.10 | On-Chip Peripheral Module Access Cycle (3-State Access)                         | 39 |

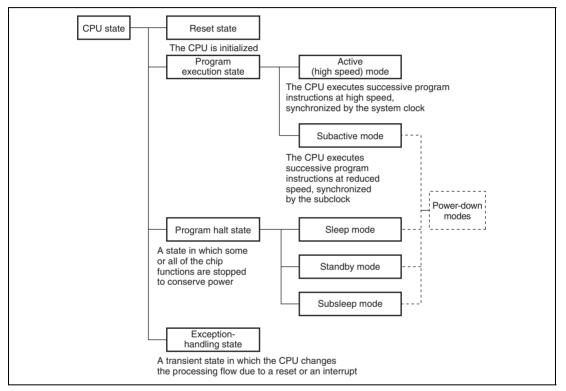

| Figure 2.11 | CPU Operation States                                                            | 40 |

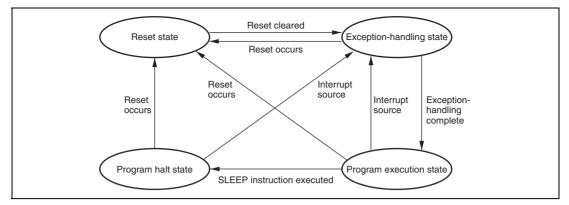

| Figure 2.12 | State Transitions                                                               | 41 |

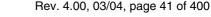

| Figure 2.13 | Example of Timer Configuration with Two Registers Allocated to                  |    |

|             | Same Address                                                                    | 42 |

| Section 3   | Exception Handling                                                              |    |

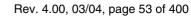

|             | Reset Sequence                                                                  | 56 |

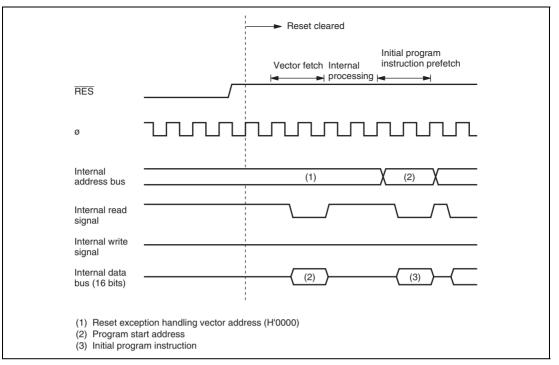

| Figure 3.2  | Stack Status after Exception Handling                                           | 57 |

| Figure 3.3  | Interrupt Sequence                                                              | 59 |

| Figure 3.4  | Port Mode Register Setting and Interrupt Request Flag Clearing Procedure        | 60 |

| Section 4   | Address Break                                                                   |    |

| Figure 4.1  | Block Diagram of Address Break                                                  | 61 |

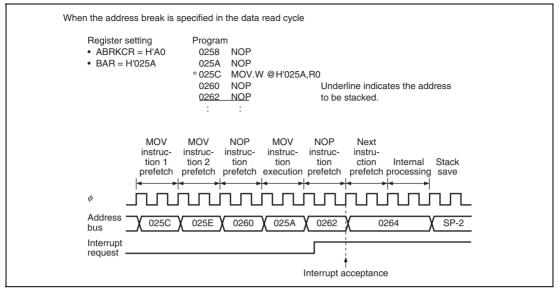

| Figure 4.2  | Address Break Interrupt Operation Example (1)                                   | 64 |

| Figure 4.2  | Address Break Interrupt Operation Example (2)                                   | 65 |

| Section 5   | Clock Pulse Generators                                                          |    |

| Figure 5.1  | Block Diagram of Clock Pulse Generators                                         | 67 |

|             |                                                                                 |    |

Rev. 4.00, 03/04, page xix of xxviii

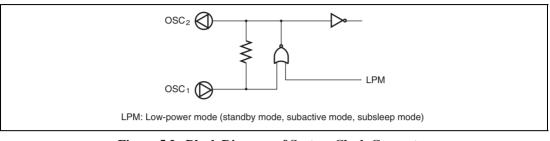

| Figure 5.2 Block Diagram of System Clock Generator                    |    |

|-----------------------------------------------------------------------|----|

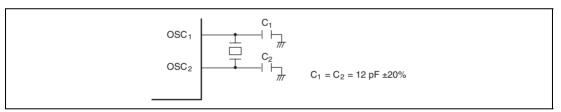

| Figure 5.3 Typical Connection to Crystal Resonator                    |    |

| Figure 5.4 Equivalent Circuit of Crystal Resonator                    |    |

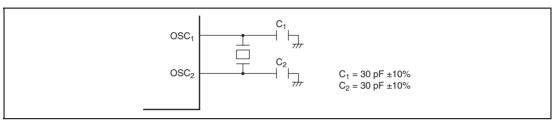

| Figure 5.5 Typical Connection to Ceramic Resonator                    |    |

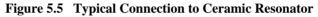

| Figure 5.6 Example of External Clock Input                            |    |

| Figure 5.7 Block Diagram of Subclock Generator                        |    |

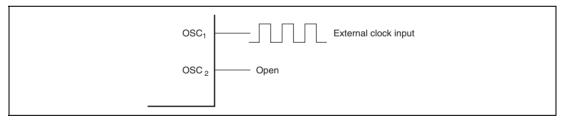

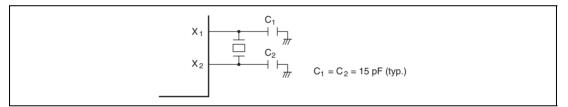

| Figure 5.8 Typical Connection to 32.768-kHz Crystal Resonator         | 70 |

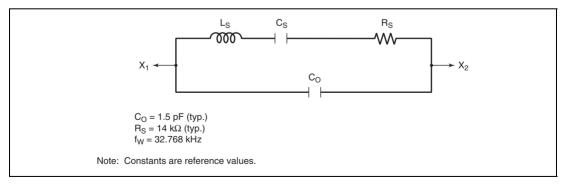

| Figure 5.9 Equivalent Circuit of 32.768-kHz Crystal Resonator         | 70 |

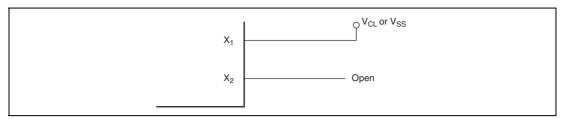

| Figure 5.10 Pin Connection when not Using Subclock                    | 71 |

| Figure 5.11 Example of Incorrect Board Design                         |    |

| Section 6 Power-Down Modes                                            |    |

| Figure 6.1 Mode Transition Diagram                                    |    |

| Section 7 ROM                                                         |    |

| Figure 7.1 Flash Memory Block Configuration                           |    |

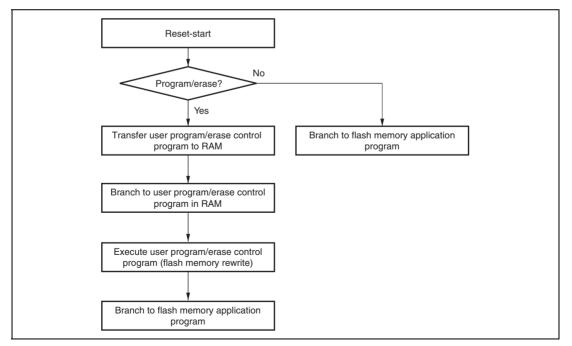

| Figure 7.2 Programming/Erasing Flowchart Example in User Program Mode |    |

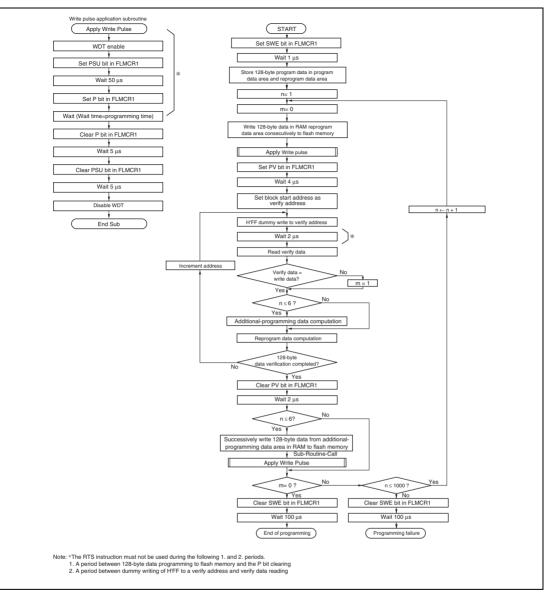

| Figure 7.3 Program/Program-Verify Flowchart                           |    |

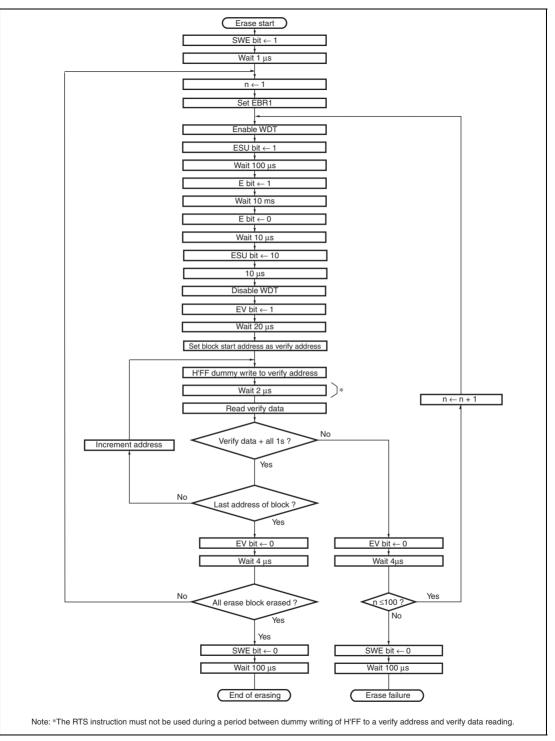

| Figure 7.4 Erase/Erase-Verify Flowchart                               |    |

| Section 9 I/O Ports                                                   |    |

| Figure 9.1 Port 1 Pin Configuration.                                  |    |

| Figure 9.2 Port 2 Pin Configuration.                                  |    |

| Figure 9.3 Port 5 Pin Configuration                                   |    |

| Figure 9.4 Port 7 Pin Configuration                                   |    |

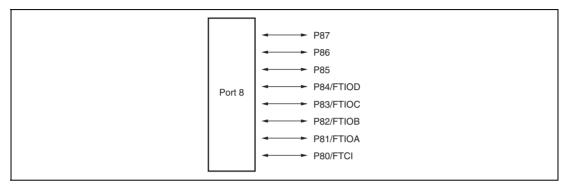

| Figure 9.5 Port 8 Pin Configuration.                                  |    |

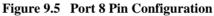

| Figure 9.6 Port B Pin Configuration                                   |    |

| Section 10 Timer A                                                    |    |

| Figure 10.1 Block Diagram of Timer A                                  |    |

| Section 11 Timer V                                                    |    |

| Figure 11.1 Block Diagram of Timer V                                  |    |

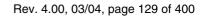

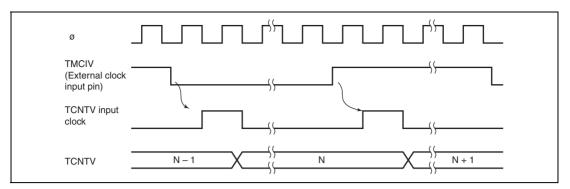

| Figure 11.2 Increment Timing with Internal Clock                      |    |

| Figure 11.3 Increment Timing with External Clock                      |    |

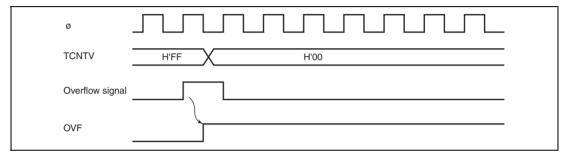

| Figure 11.4 OVF Set Timing                                            |    |

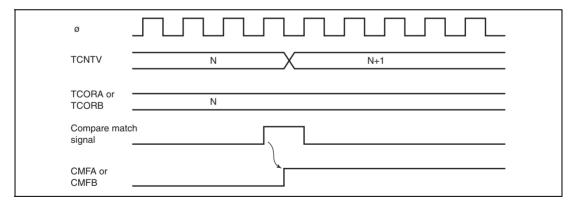

| Figure 11.5 CMFA and CMFB Set Timing                                  |    |

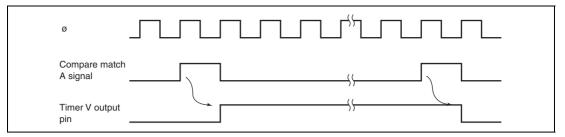

| Figure 11.6 TMOV Output Timing                                        |    |

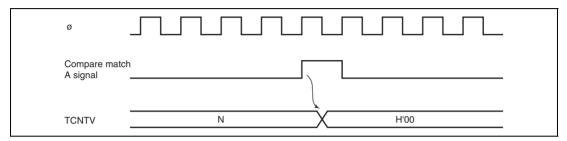

| Figure 11.7 Clear Timing by Compare Match                             |    |

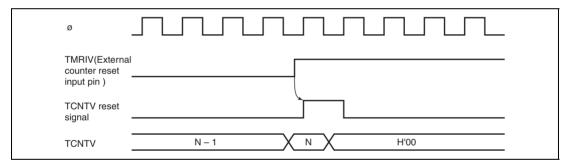

| Figure 11.8 Clear Timing by TMRIV Input                               |    |

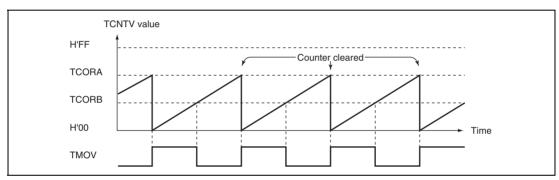

| Figure 11.9 Pulse Output Example                                      |    |

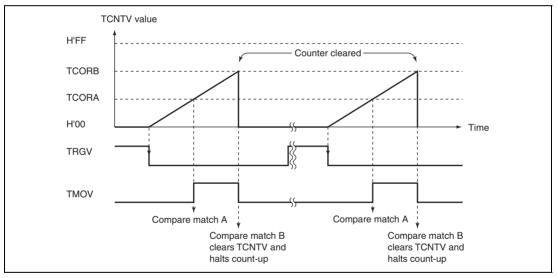

| Figure 11.10 Example of Pulse Output Synchronized to TRGV Input       |    |

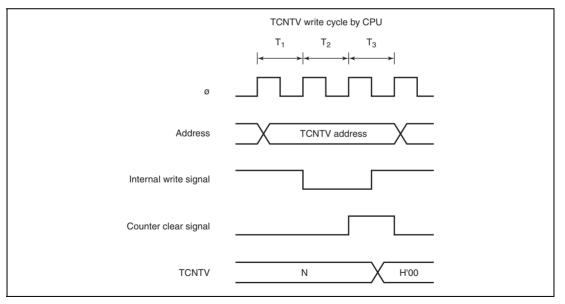

| Figure 11.11 Contention between TCNTV Write and Clear                 |    |

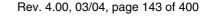

| Figure 11.12 Contention between TCORA Write and Compare Match         |    |

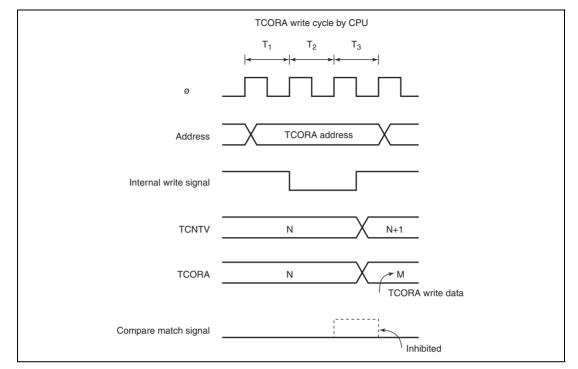

| Figure 11.13 Internal Clock Switching and TCNTV Operation             |    |

#### Section 12 Timer W

| Figure 12.1  | Timer W Block Diagram                                               | 147 |

|--------------|---------------------------------------------------------------------|-----|

| Figure 12.2  | Free-Running Counter Operation                                      |     |

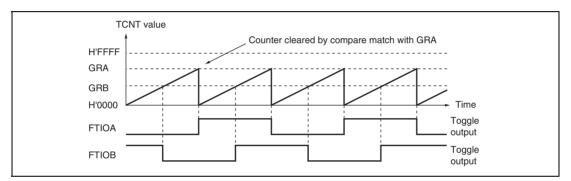

| Figure 12.3  | Periodic Counter Operation                                          |     |

| Figure 12.4  | 0 and 1 Output Example (TOA = 0, TOB = 1)                           |     |

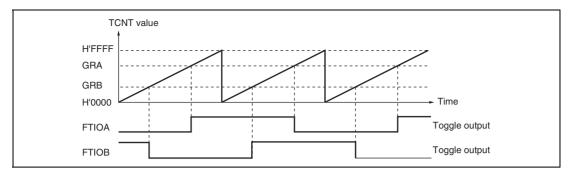

|              | Toggle Output Example (TOA = 0, TOB = 1)                            |     |

| Figure 12.6  | Toggle Output Example (TOA = 0, TOB = 1)                            |     |

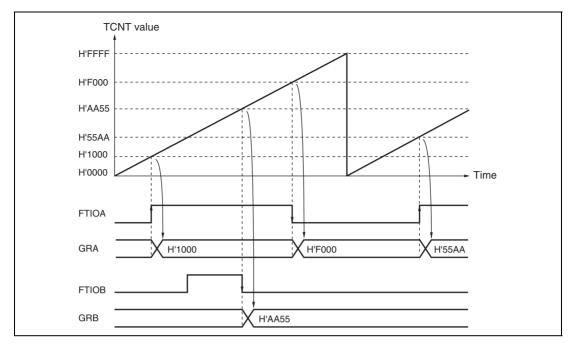

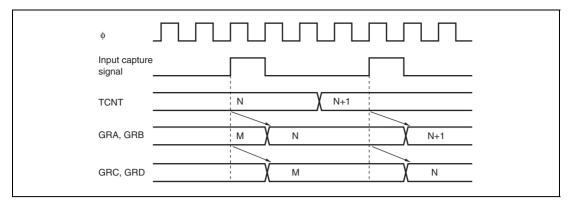

| Figure 12.7  | Input Capture Operating Example                                     |     |

| Figure 12.8  | Buffer Operation Example (Input Capture)                            |     |

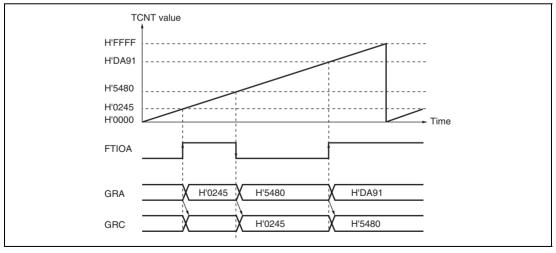

| Figure 12.9  | PWM Mode Example (1)                                                |     |

|              | PWM Mode Example (2)                                                |     |

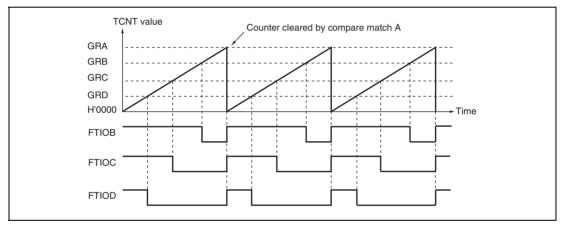

| Figure 12.11 | Buffer Operation Example (Output Compare)                           |     |

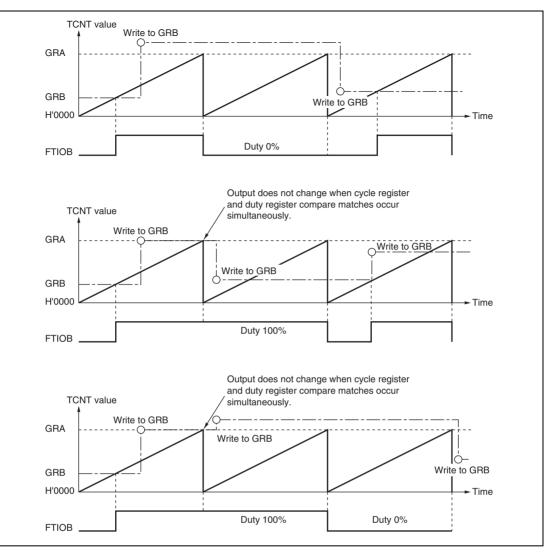

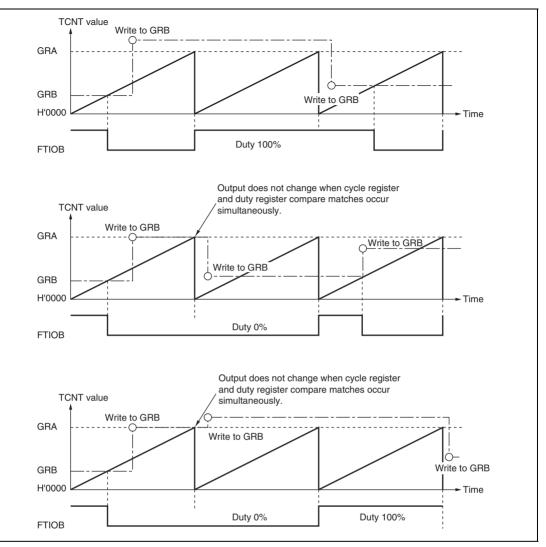

| Figure 12.12 | PWM Mode Example                                                    |     |

|              | (TOB, TOC, and TOD = 0: initial output values are set to 0)         |     |

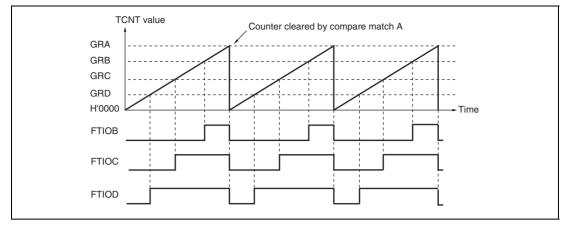

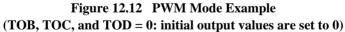

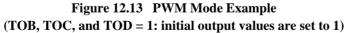

| Figure 12.13 | PWM Mode Example                                                    |     |

|              | (TOB, TOC, and TOD = 1: initial output values are set to 1)         |     |

|              | Count Timing for Internal Clock Source                              |     |

| -            | Count Timing for External Clock Source                              |     |

| Figure 12.16 | Output Compare Output Timing                                        |     |

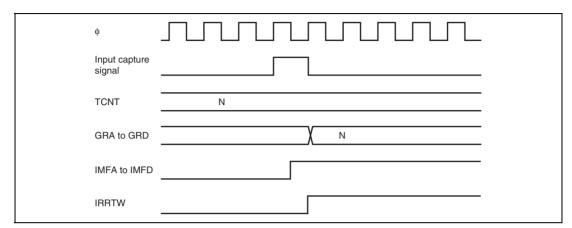

| -            | Input Capture Input Signal Timing                                   |     |

| Figure 12.18 | Timing of Counter Clearing by Compare Match                         |     |

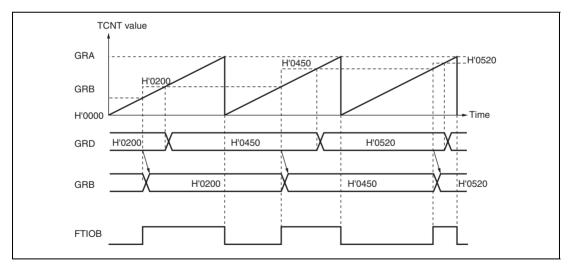

| Figure 12.19 | Buffer Operation Timing (Compare Match)                             |     |

| Figure 12.20 | Buffer Operation Timing (Input Capture)                             |     |

| Figure 12.21 | Timing of IMFA to IMFD Flag Setting at Compare Match                |     |

| Figure 12.22 | Timing of IMFA to IMFD Flag Setting at Input Capture                |     |

| Figure 12.23 | Timing of Status Flag Clearing by CPU                               |     |

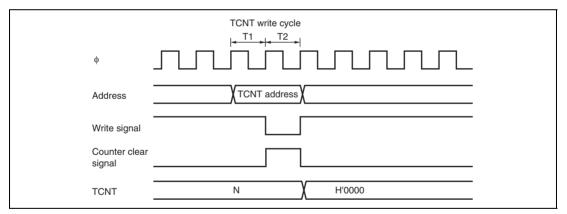

| Figure 12.24 | Contention between TCNT Write and Clear                             |     |

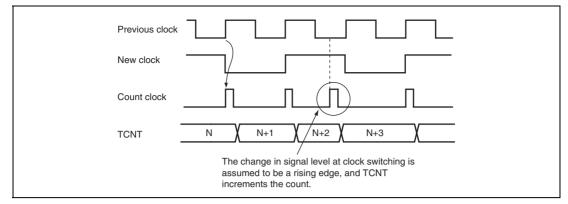

| Figure 12.25 | Internal Clock Switching and TCNT Operation                         |     |

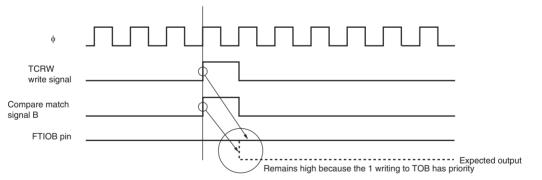

| Figure 12.26 | When Compare Match and Bit Manipulation Instruction to TCRW         |     |

|              | Occur at the Same Timing                                            |     |

| Section 13   | Watchdog Timer                                                      |     |

|              | Block Diagram of Watchdog Timer                                     | 173 |

|              | Watchdog Timer Operation Example                                    |     |

| •            | • • •                                                               | 1// |

|              | Serial Communication Interface3 (SCI3)                              |     |

| 0            | Block Diagram of SCI3                                               |     |

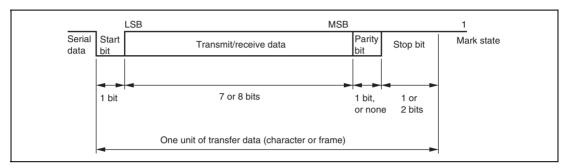

|              | Data Format in Asynchronous Communication                           |     |

| Figure 14.3  | Relationship between Output Clock and Transfer Data Phase           |     |

|              | (Asynchronous Mode)(Example with 8-Bit Data, Parity, Two Stop Bits) |     |

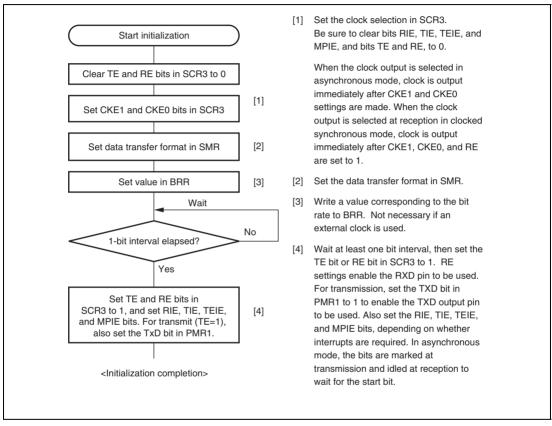

| Figure 14.4  | Sample SCI3 Initialization Flowchart                                |     |

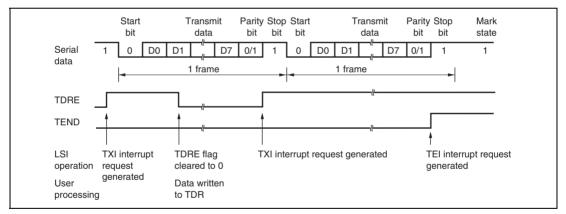

| Figure 14.5  | Example SCI3 Operation in Transmission in Asynchronous Mode         |     |

|              | (8-Bit Data, Parity, One Stop Bit)                                  |     |

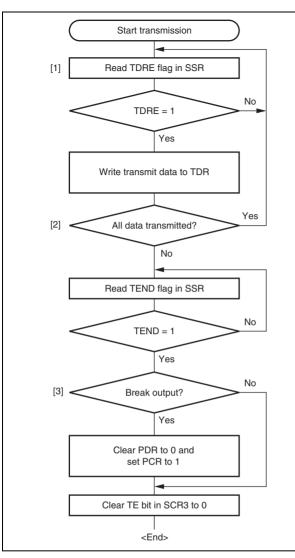

| Figure 14.6  | Sample Serial Transmission Flowchart (Asynchronous Mode)            |     |

|              | <b>_</b>                                                            |     |

## RENESAS

Rev. 4.00, 03/04, page xxi of xxviii

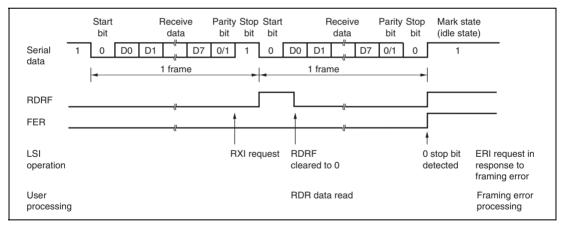

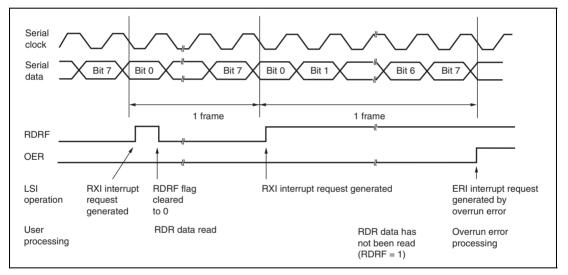

| Figure 14.7 Example SCI3 Operation in Reception in Asynchronous Mode                 |     |

|--------------------------------------------------------------------------------------|-----|

| (8-Bit Data, Parity, One Stop Bit)                                                   | 199 |

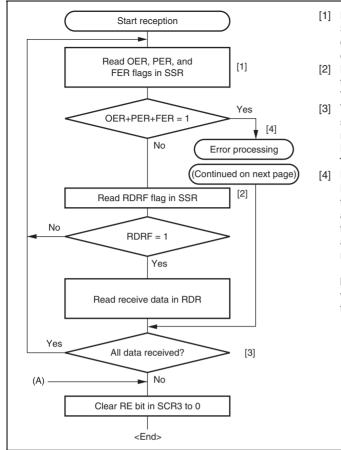

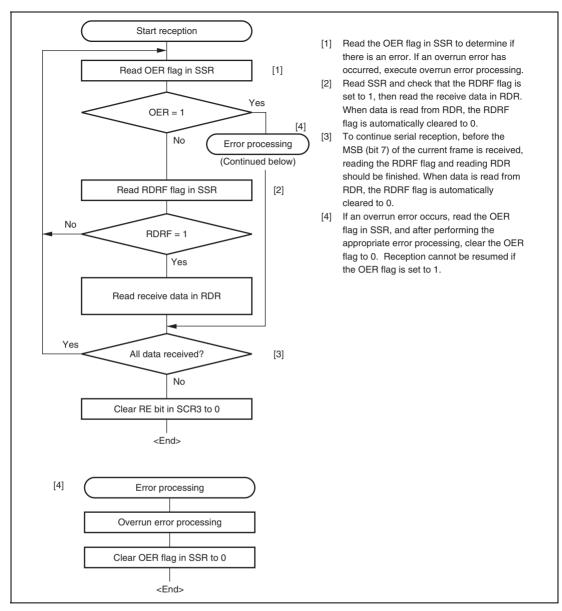

| Figure 14.8 Sample Serial Data Reception Flowchart (Asynchronous mode) (1)           | 201 |

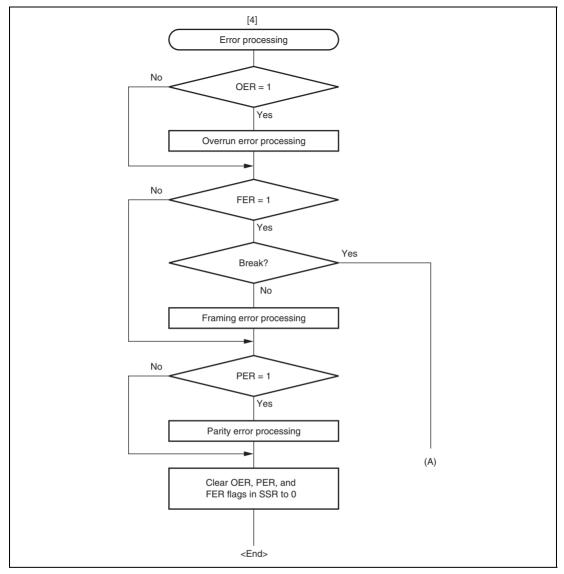

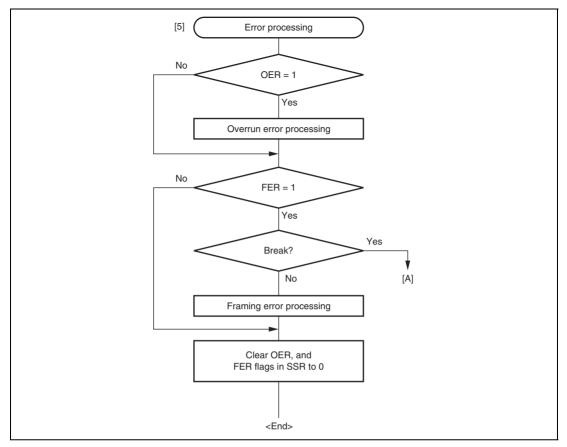

| Figure 14.8 Sample Serial Reception Data Flowchart (2)                               | 202 |

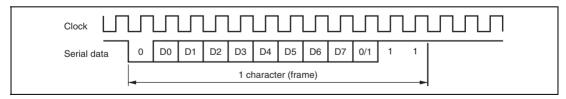

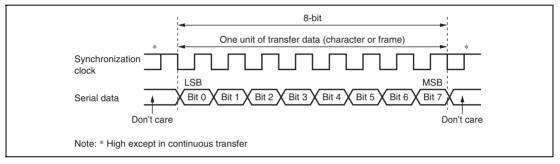

| Figure 14.9 Data Format in Clocked Synchronous Communication                         | 203 |

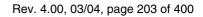

| Figure 14.10 Example of SCI3 Operation in Transmission in Clocked Synchronous Mode   | 204 |

| Figure 14.11 Sample Serial Transmission Flowchart (Clocked Synchronous Mode)         | 205 |

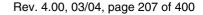

| Figure 14.12 Example of SCI3 Reception Operation in Clocked Synchronous Mode         | 206 |

| Figure 14.13 Sample Serial Reception Flowchart (Clocked Synchronous Mode)            | 207 |

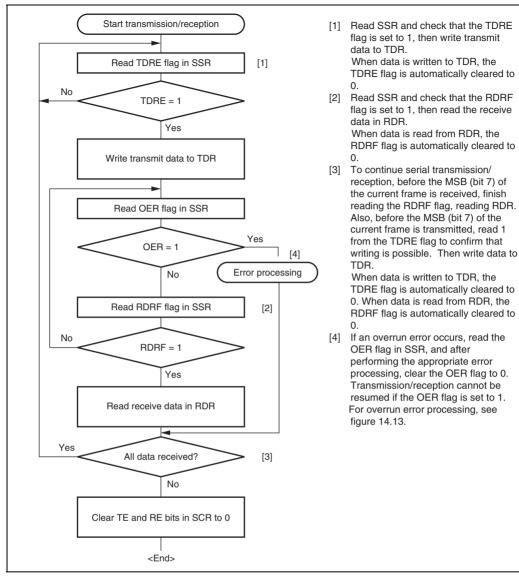

| Figure 14.14 Sample Flowchart of Simultaneous Serial Transmit and Receive Operations |     |

| (Clocked Synchronous Mode)                                                           | 209 |

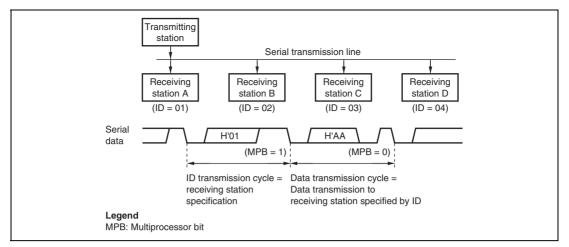

| Figure 14.15 Example of Communication Using Multiprocessor Format                    |     |

| (Transmission of Data H'AA to Receiving Station A)                                   | 211 |

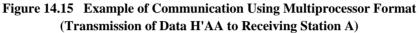

| Figure 14.16 Sample Multiprocessor Serial Transmission Flowchart                     | 212 |

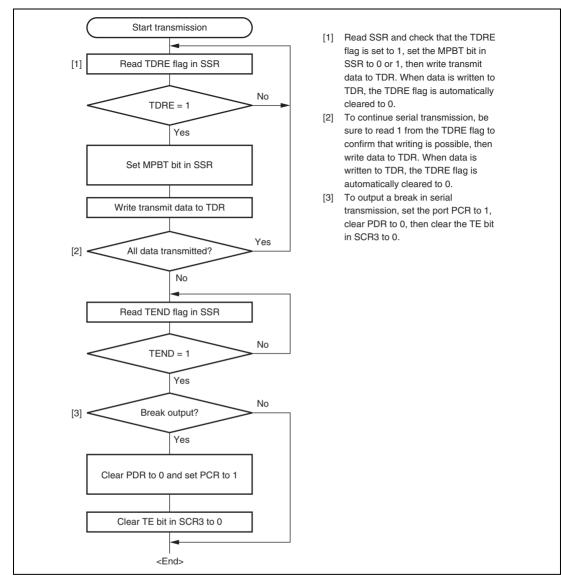

| Figure 14.17 Sample Multiprocessor Serial Reception Flowchart (1)                    | 213 |

| Figure 14.17 Sample Multiprocessor Serial Reception Flowchart (2)                    | 214 |

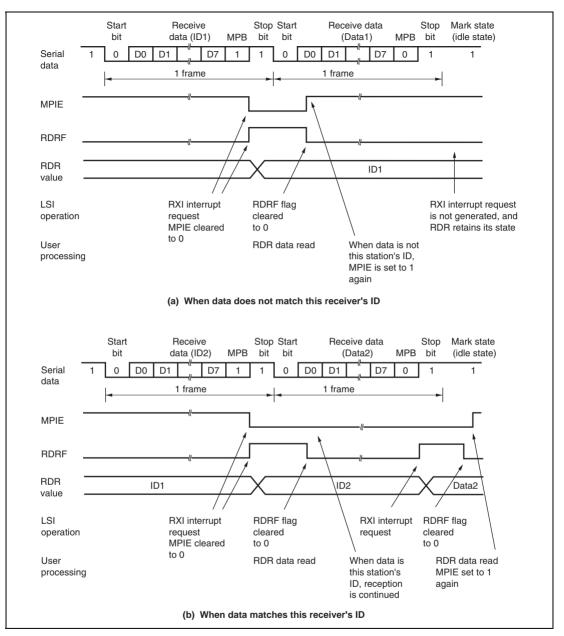

| Figure 14.18 Example of SCI3 Operation in Reception Using Multiprocessor Format      |     |

| (Example with 8-Bit Data, Multiprocessor Bit, One Stop Bit)                          | 215 |

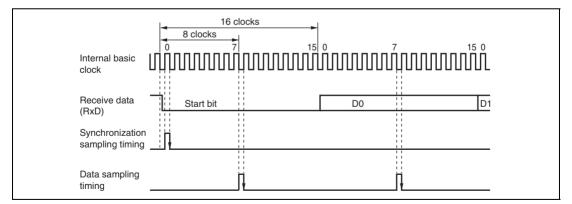

| Figure 14.19 Receive Data Sampling Timing in Asynchronous Mode                       | 218 |

| Section 15 I <sup>2</sup> C Bus Interface 2 (IIC2)                                   |     |

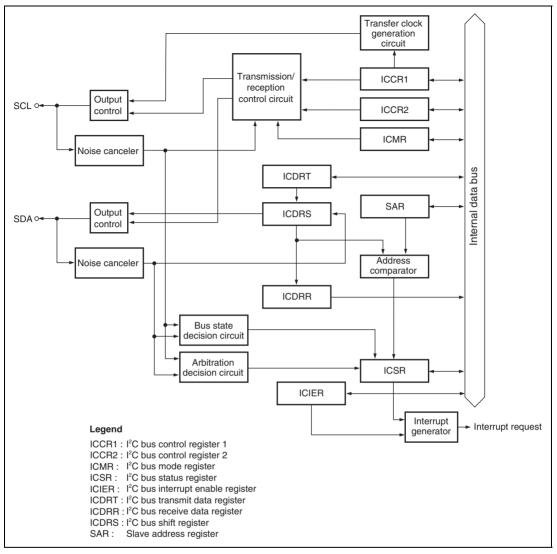

| Figure 15.1 Block Diagram of I <sup>2</sup> C Bus Interface 2                        | 220 |

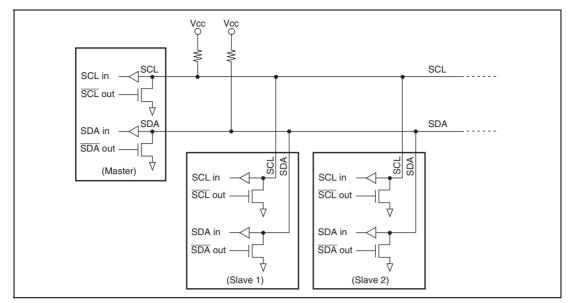

| Figure 15.2 External Circuit Connections of I/O Pins                                 |     |

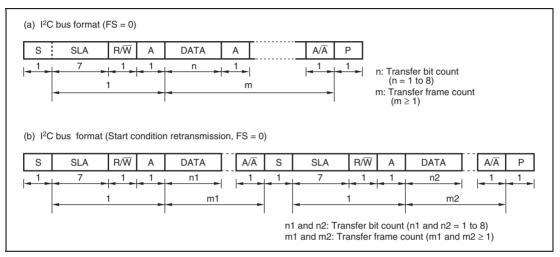

| Figure 15.3 I <sup>2</sup> C Bus Formats                                             |     |

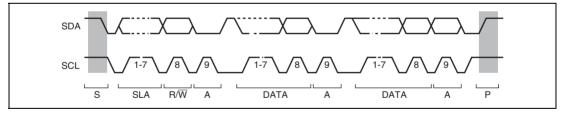

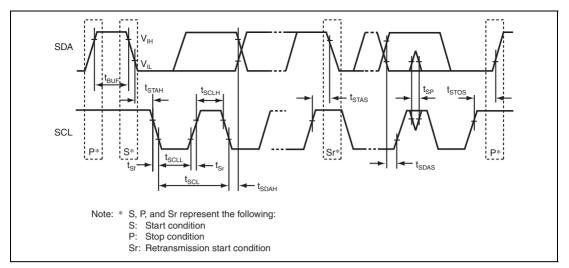

| Figure 15.4 I <sup>2</sup> C Bus Timing                                              |     |

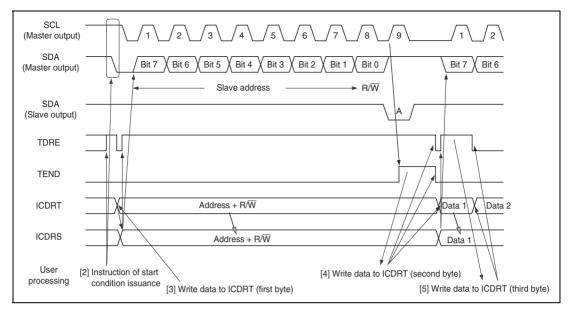

| Figure 15.5 Master Transmit Mode Operation Timing (1)                                | 235 |

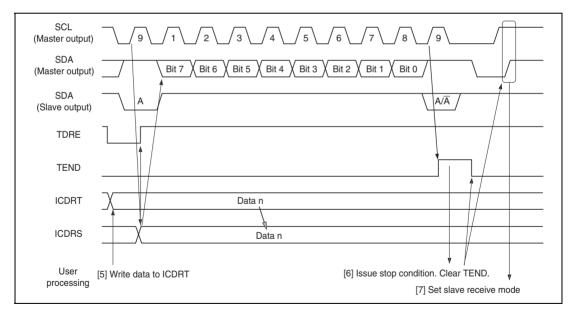

| Figure 15.6 Master Transmit Mode Operation Timing (2)                                |     |

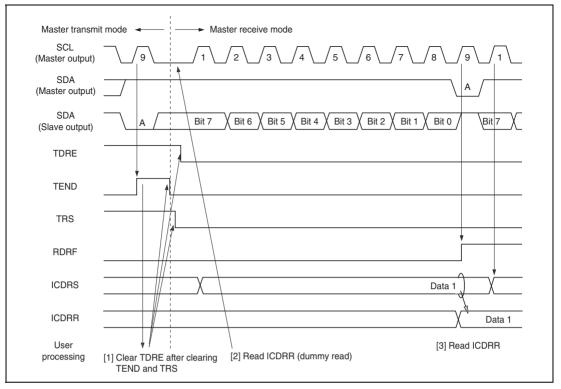

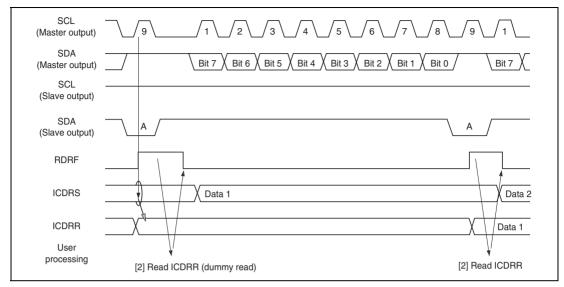

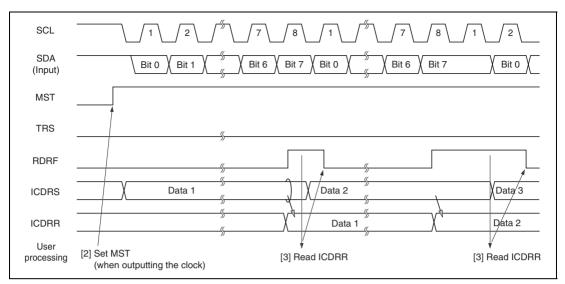

| Figure 15.7 Master Receive Mode Operation Timing (1)                                 | 237 |

| Figure 15.8 Master Receive Mode Operation Timing (2)                                 |     |

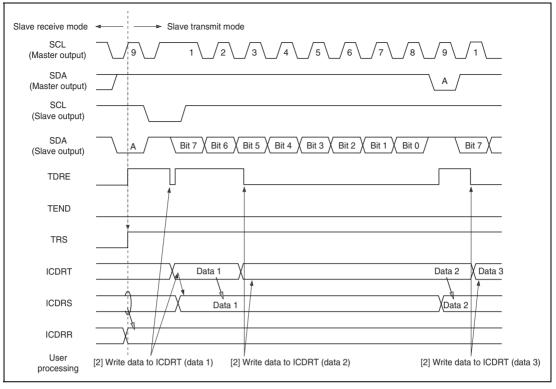

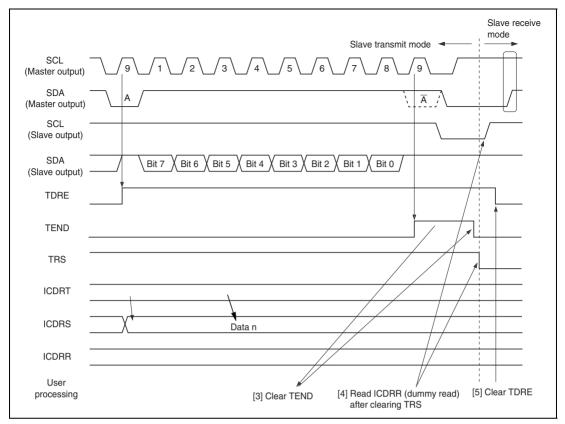

| Figure 15.9 Slave Transmit Mode Operation Timing (1)                                 | 239 |

| Figure 15.10 Slave Transmit Mode Operation Timing (2)                                | 240 |

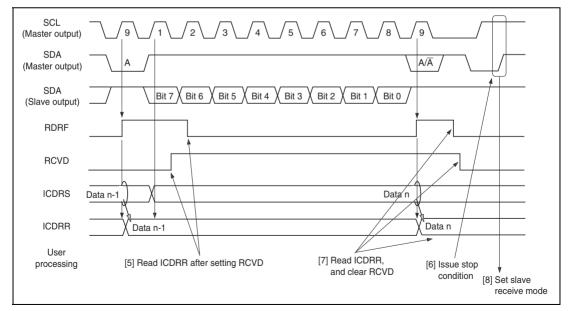

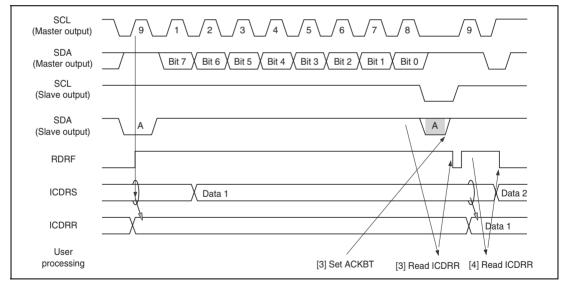

| Figure 15.11 Slave Receive Mode Operation Timing (1)                                 | 241 |

| Figure 15.12 Slave Receive Mode Operation Timing (2)                                 | 241 |

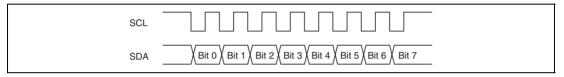

| Figure 15.13 Clocked Synchronous Serial Transfer Format                              | 242 |

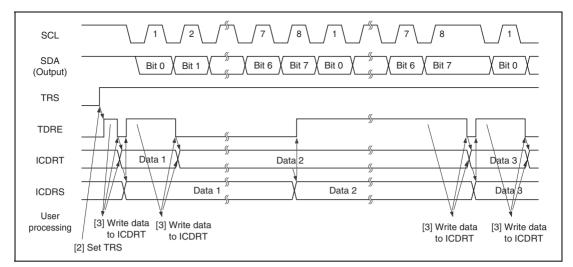

| Figure 15.14 Transmit Mode Operation Timing                                          | 243 |

| Figure 15.15 Receive Mode Operation Timing                                           | 244 |

| Figure 15.16 Block Diagram of Noise Conceler                                         | 244 |

| Figure 15.17 Sample Flowchart for Master Transmit Mode                               | 245 |

| Figure 15.18 Sample Flowchart for Master Receive Mode                                | 246 |

| Figure 15.19 Sample Flowchart for Slave Transmit Mode                                |     |

| Figure 15.20 Sample Flowchart for Slave Receive Mode                                 |     |

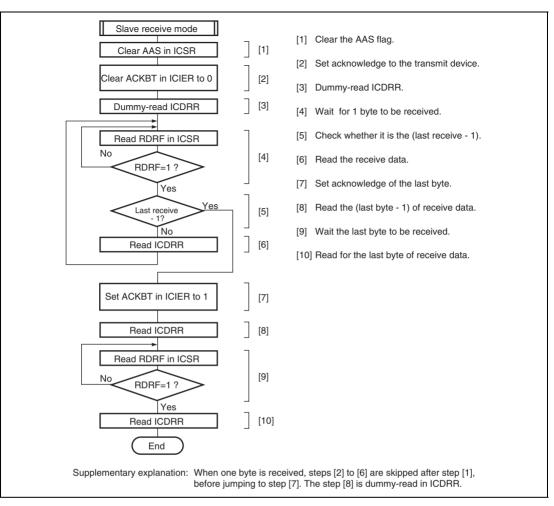

| Figure 15.21 The Timing of the Bit Synchronous Circuit                               | 250 |

| Section 16  | A/D Converter                                                             |     |

|-------------|---------------------------------------------------------------------------|-----|

| Figure 16.1 | Block Diagram of A/D Converter                                            | 252 |

| Figure 16.2 | A/D Conversion Timing                                                     | 258 |

| Figure 16.3 | External Trigger Input Timing                                             | 259 |

| Figure 16.4 | A/D Conversion Accuracy Definitions (1)                                   | 260 |

| Figure 16.5 | A/D Conversion Accuracy Definitions (2)                                   | 261 |

| Figure 16.6 | Analog Input Circuit Example                                              | 262 |

| Section 17  | EEPROM                                                                    |     |

| Figure 17.1 | Block Diagram of EEPROM                                                   | 264 |

| Figure 17.2 | EEPROM Bus Format and Bus Timing                                          | 266 |

| Figure 17.3 | Byte Write Operation                                                      | 269 |

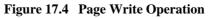

| Figure 17.4 | Page Write Operation                                                      | 269 |

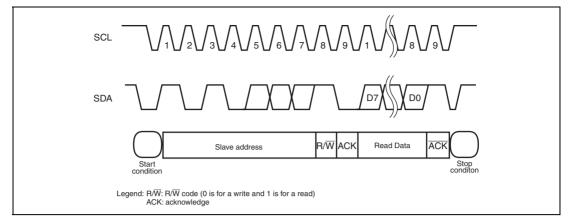

| Figure 17.5 | Current Address Read Operation                                            | 271 |

| Figure 17.6 | Random Address Read Operation                                             | 271 |

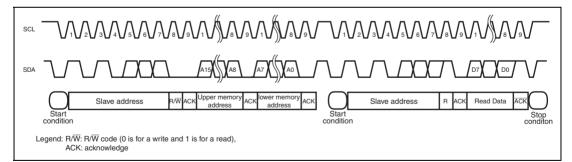

| Figure 17.7 | Sequential Read Operation (when current address read is used)             | 272 |

| Section 18  | Power-On Reset and Low-Voltage Detection Circuits (Optional)              |     |

| Figure 18.1 | Block Diagram of Power-On Reset Circuit and Low-Voltage Detection Circuit | 276 |

| Figure 18.2 | Operational Timing of Power-On Reset Circuit                              | 279 |

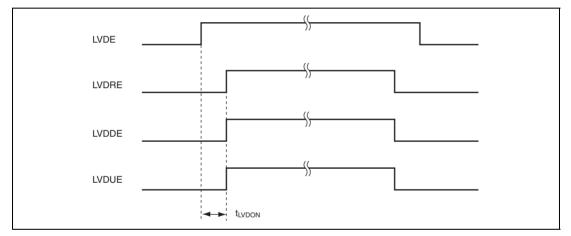

| Figure 18.3 | Operational Timing of LVDR Circuit                                        | 280 |

| Figure 18.4 | Operational Timing of LVDI Circuit                                        | 281 |

| Figure 18.5 | Timing for Operation/Release of Low-Voltage Detection Circuit             | 282 |

| Section 19  | Power Supply Circuit                                                      |     |

| Figure 19.1 | Power Supply Connection when Internal Step-Down Circuit is Used           | 283 |

| Figure 19.2 | Power Supply Connection when Internal Step-Down Circuit is Not Used       | 284 |

| Section 21  | Electrical Characteristics                                                |     |

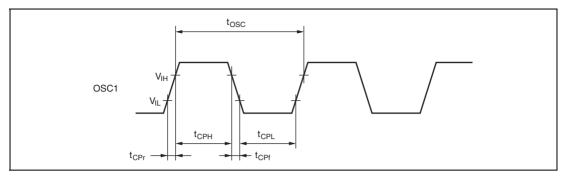

| Figure 21.1 | System Clock Input Timing                                                 | 331 |

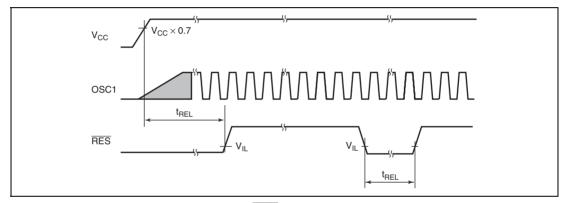

| Figure 21.2 | RES Low Width Timing                                                      | 331 |

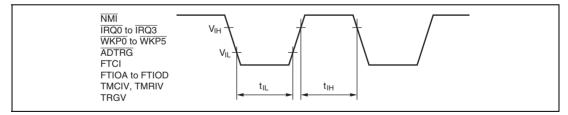

| Figure 21.3 | Input Timing                                                              | 331 |

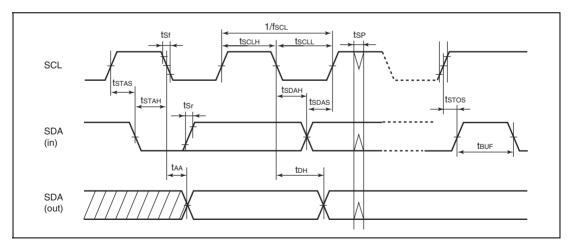

| Figure 21.4 | I <sup>2</sup> C Bus Interface Input/Output Timing                        | 332 |

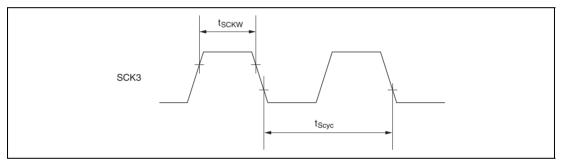

| Figure 21.5 | SCK3 Input Clock Timing                                                   | 332 |

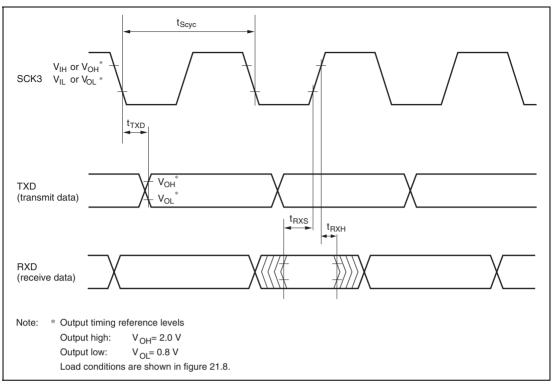

| Figure 21.6 | SCI Input/Output Timing in Clocked Synchronous Mode                       | 333 |

| Figure 21.7 | EEPROM Bus Timing                                                         | 333 |

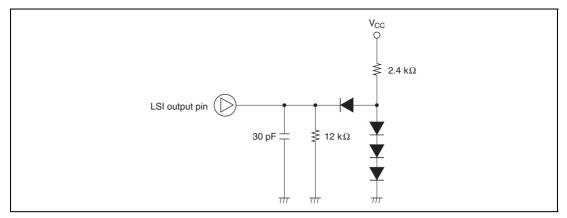

| Figure 21.8 | Output Load Circuit                                                       | 334 |

| Appendix I  | 3 I/O Port Block Diagrams                                                 |     |

| Figure B.1  | Port 1 Block Diagram (P17)                                                | 365 |

|             | Port 1 Block Diagram (P16 to P14)                                         |     |

| Figure B.3  | Port 1 Block Diagram (P12, P11)                                           | 367 |

| Figure B.4  | Port 1 Block Diagram (P10)                                                | 368 |

| Figure B.5  | Port 2 Block Diagram (P22)                                                | 369 |

| Figure B.6  | Port 2 Block Diagram (P21)                                                | 370 |

Rev. 4.00, 03/04, page xxiii of xxviii

| 375 |

|-----|

| 376 |

| 377 |

|     |

| 379 |

| 380 |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

| 389 |

|     |

## Tables

| Section 1  | Overview                                                                 |    |

|------------|--------------------------------------------------------------------------|----|

| Table 1.1  | Pin Functions                                                            | 8  |

| Section 2  | CPU                                                                      |    |

| Table 2.1  | Operation Notation                                                       | 22 |

| Table 2.2  | Data Transfer Instructions                                               | 23 |

| Table 2.3  | Arithmetic Operations Instructions (1)                                   |    |

| Table 2.3  | Arithmetic Operations Instructions (2)                                   | 25 |

| Table 2.4  | Logic Operations Instructions                                            | 26 |

| Table 2.5  | Shift Instructions                                                       | 26 |

| Table 2.6  | Bit Manipulation Instructions (1)                                        | 27 |

| Table 2.6  | Bit Manipulation Instructions (2)                                        | 28 |

| Table 2.7  | Branch Instructions                                                      | 29 |

| Table 2.8  | System Control Instructions                                              |    |

| Table 2.9  | Block Data Transfer Instructions                                         | 31 |

| Table 2.10 |                                                                          |    |

| Table 2.11 | e                                                                        |    |

| Table 2.12 | (-)                                                                      |    |

| Table 2.12 | Effective Address Calculation (2)                                        | 37 |

| Section 3  | Exception Handling                                                       |    |

| Table 3.1  | Exception Sources and Vector Address                                     | 47 |

| Table 3.2  | Interrupt Wait States                                                    | 58 |

| Section 4  | Address Break                                                            |    |

| Table 4.1  | Access and Data Bus Used                                                 | 63 |

| Section 5  | Clock Pulse Generators                                                   |    |

| Table 5.1  | Crystal Resonator Parameters                                             | 69 |

| Section 6  | Power-Down Modes                                                         |    |

| Table 6.1  | Operating Frequency and Waiting Time                                     | 75 |

| Table 6.2  | Transition Mode after SLEEP Instruction Execution and Interrupt Handling |    |

| Table 6.3  | Internal State in Each Operating Mode                                    |    |

| Section 7  | ROM                                                                      |    |

| Table 7.1  | Setting Programming Modes                                                | 90 |

| Table 7.2  | Boot Mode Operation                                                      |    |

| Table 7.3  | System Clock Frequencies for which Automatic Adjustment of               |    |

|            | LSI Bit Rate is Possible                                                 | 93 |

| Table 7.4  | Reprogram Data Computation Table                                         |    |

| Table 7.5  | Additional-Program Data Computation Table                                |    |

| Table 7.6  | Programming Time                                                         | 96 |

Rev. 4.00, 03/04, page xxv of xxviii

| Table 7.7                                                                                                                  | Flash Memory Operating States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100                                           |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Section 10<br>Table 10.1                                                                                                   | Timer A<br>Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 126                                           |

| Section 11<br>Table 11.1<br>Table 11.2                                                                                     | Timer V<br>Pin Configuration<br>Clock Signals to Input to TCNTV and Counting Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

| Section 12<br>Table 12.1<br>Table 12.2                                                                                     | Timer W<br>Timer W Functions<br>Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| Section 14<br>Table 14.1<br>Table 14.2<br>Table 14.2<br>Table 14.2<br>Table 14.3<br>Table 14.4<br>Table 14.4<br>Table 14.4 | Serial Communication Interface3 (SCI3)<br>Pin Configuration<br>Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (1)<br>Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (2)<br>Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (3)<br>Maximum Bit Rate for Each Frequency (Asynchronous Mode)<br>Examples of BBR Setting for Various Bit Rates<br>(Clocked Synchronous Mode) (1)<br>Examples of BRR Settings for Various Bit Rates<br>(Clocked Synchronous Mode) (2)<br>SSR Status Flags and Receive Data Handling<br>SCI3 Interrupt Requests | 189<br>190<br>191<br>192<br>193<br>194<br>200 |

| <b>Section 15</b><br>Table 15.1<br>Table 15.2<br>Table 15.3<br>Table 15.4                                                  | I <sup>2</sup> C Bus Interface 2 (IIC2)<br>I <sup>2</sup> C Bus Interface Pins<br>Transfer Rate<br>Interrupt Requests<br>Time for Monitoring SCL                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 223<br>249                                    |

| Section 16<br>Table 16.1<br>Table 16.2<br>Table 16.3                                                                       | A/D Converter<br>Pin Configuration<br>Analog Input Channels and Corresponding ADDR Registers<br>A/D Conversion Time (Single Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 254                                           |