# Low-Power, 32-bit Cortex-M0+ MCUs with 12-bit ADC, 10-bit DAC, 256-Channel PTC, RTC, and SERCOM

**SAM D20 Family**

#### **Features**

#### **Operating Conditions**

- 1.62V 3.63V, -40°C to +85°C, DC up to 48 MHz

- 1.62V 3.63V, -40°C to +105°C, DC up to 32 MHz

- 2.7V 3.63V, -40°C to +125°C Extended Temperature with compliance to AEC-Q100, DC up to 32MHz

#### Core

- Arm Cortex -M0+ CPU running at up to 48 MHz

- Single-cycle hardware multiplier

#### **Memories**

- 16/32/64/128/256 KB in-system self-programmable Flash

- 2/4/8/16/32 KB SRAM

#### **System**

- Power-on Reset (POR) and Brown-out Detection (BOD)

- Internal and external clock options with 48 MHz Digital Frequency Locked Loop (DFLL48M)

- External Interrupt Controller (EIC)

- Up to 16 external interrupts

- One non-maskable interrupt

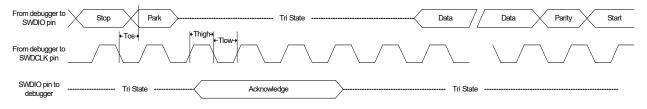

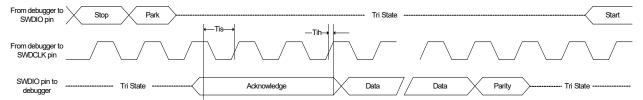

- Two-pin Serial Wire Debug (SWD) programming, test and debugging interface

#### **Low-Power**

- Idle and Stand-by Sleep modes

- SleepWalking peripherals

### **Peripherals**

- 8-channel Event System

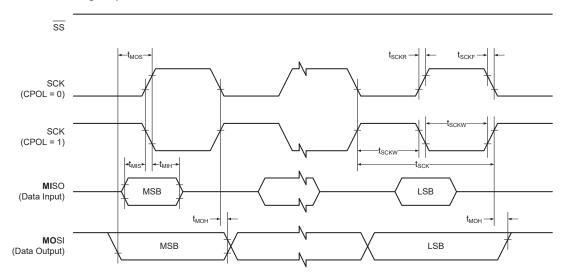

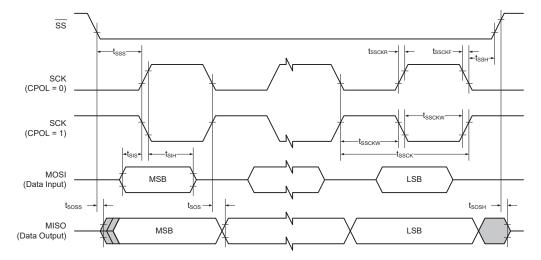

- Up to eight 16-bit Timer/Counters (TC), configurable as:

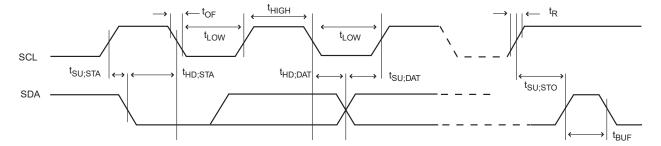

- One 16-bit TC with two compare/capture channels

- One 8-bit TC with two compare/capture channels

- One 32-bit TC with two compare/capture channels, by using two TCs

- 32-bit Real Time Counter (RTC) with clock/calendar function

- Watchdog Timer (WDT)

- · CRC-32 generator

- Up to six Serial Communication Interfaces (SERCOM), each configurable to operate as either:

- USART with full-duplex and single-wire half-duplex configuration

- Inter-Integrated Circuit (I<sup>2</sup>C) up to 400 kHz

- Serial Peripheral Interface (SPI)

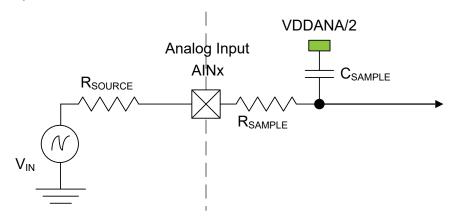

- One 12-bit, 350 ksps Analog-to-Digital Converter (ADC) with up to 20 channels

- Differential and single-ended input

- 1/2x to 16x programmable gain stage

- Automatic offset and gain error compensation

- Oversampling and decimation in hardware to support 13-bit, 14-bit, 15-bit, or 16-bit resolution

- 10-bit, 350 ksps Digital-to-Analog Converter (DAC)

- Two Analog Comparators (AC) with Window Compare function

- Peripheral Touch Controller (PTC)

- Up to 256-channel capacitive touch and proximity sensing

#### 1/0

• Up to 52 programmable I/O pins

#### **Packages**

- 64-pin TQFP, VQFN

- 64-ball UFBGA (not available in grades Extended Temperature and AEC-QA100)

- 48-pin TQFP, VQFN

- 45-ball WLCSP (not available in grades Extended Temperature and AEC-QA100)

- 32-pin TQFP, VQFN

- 27-ball WLCSP (not available in grades Extended Temperature and AEC-QA100)

#### **Power Consumption**

- Power Consumption

- Down to 50 μA/MHz in Active mode

- Down to 8 μA running the PTC

# **Table of Contents**

| Fea | itures |                                       |    |

|-----|--------|---------------------------------------|----|

| 1.  | Confi  | guration Summary                      | 11 |

| 2.  | Orde   | ring Information <sup>(1)</sup>       | 13 |

| 3.  | Block  | Diagram                               | 14 |

| 4.  | Pinou  | ıt                                    | 15 |

|     | 4.1.   | SAM D20J                              | 15 |

|     | 4.2.   | SAM D20G                              | 17 |

|     | 4.3.   | SAM D20E                              | 19 |

| 5.  | Signa  | ll Descriptions List                  | 21 |

| 6.  | I/O M  | lultiplexing and Considerations       | 22 |

|     | 6.1.   | Multiplexed Signals                   | 22 |

|     | 6.2.   | Other Functions                       | 24 |

| 7.  | Powe   | er Supply and Start-Up Considerations | 26 |

|     | 7.1.   | Power Domain Overview                 | 26 |

|     | 7.2.   | Power Supply Considerations           | 26 |

|     | 7.3.   | Power-Up                              | 28 |

|     | 7.4.   | Power-On Reset and Brown-Out Detector | 28 |

| 8.  | Produ  | uct Mapping                           | 30 |

| 9.  | Mem    | ories                                 | 31 |

|     | 9.1.   | Embedded Memories                     | 31 |

|     | 9.2.   | Physical Memory Map                   | 31 |

|     | 9.3.   | NVM Calibration and Auxiliary Space   | 31 |

|     | 9.4.   | NVM User Row Mapping                  |    |

|     | 9.5.   | NVM Software Calibration Area Mapping | 33 |

|     | 9.6.   | Serial Number                         |    |

| 10. | Proce  | essor And Architecture                | 35 |

|     | 10.1.  | Cortex M0+ Processor                  | 35 |

|     | 10.2.  | Nested Vector Interrupt Controller    | 36 |

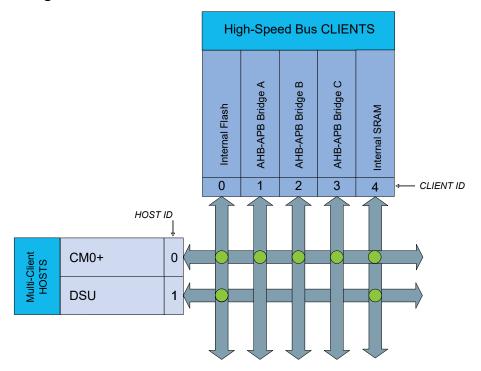

|     | 10.3.  | High-Speed Bus System                 | 37 |

|     |        | AHB-APB Bridge                        |    |

|     |        | PAC - Peripheral Access Controller    |    |

|     | 10.6.  | Register Description                  | 40 |

| 11. | Perip  | herals Configuration Summary          | 51 |

| 12. | DSU -  | - Device Service Unit                 | 53 |

|     | 12.1.  | Overview                              | 53 |

|     |        | Features                              |    |

|     |        | Block Diagram                         |    |

|     | 12.4.  | Signal Description                    | 54 |

|     | 12.5.  | Product Dependencies                | 54  |

|-----|--------|-------------------------------------|-----|

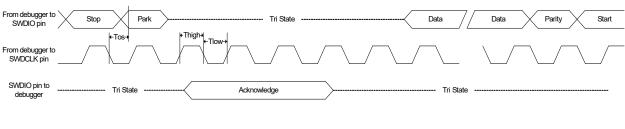

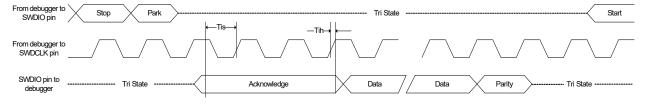

|     | 12.6.  | Debug Operation                     | 55  |

|     | 12.7.  | Chip Erase                          | 56  |

|     | 12.8.  | Programming                         | 57  |

|     | 12.9.  | Intellectual Property Protection    | 57  |

|     |        | Device Identification               |     |

|     | 12.11. | Functional Description              | 60  |

|     | 12.12. | Register Summary                    | 65  |

|     | 12.13. | Register Description                | 66  |

| 13. | Clock  | System                              | 89  |

|     | 13.1.  | Clock Distribution                  | 89  |

|     | 13.2.  | Synchronous and Asynchronous Clocks | 90  |

|     |        | Register Synchronization            |     |

|     |        | Enabling a Peripheral               |     |

|     |        | Disabling a Peripheral              |     |

|     |        | On-demand, Clock Requests           |     |

|     |        | Power Consumption vs. Speed         |     |

|     |        | Clocks after Reset                  |     |

| 14. | GCLK   | - Generic Clock Controller          | 97  |

|     | 14.1.  | Overview                            | 97  |

|     |        | Features                            |     |

|     |        | Block Diagram                       |     |

|     |        | Signal Description                  |     |

|     |        | Product Dependencies                |     |

|     |        | Functional Description              |     |

|     |        | Register Summary                    |     |

|     |        | Register Description                |     |

| 15  |        | · Manager (PM)                      |     |

| ١٥. |        | Overview                            |     |

|     |        |                                     |     |

|     |        | Features                            |     |

|     |        | Block Diagram                       |     |

|     |        | Signal Description                  |     |

|     |        | Product Dependencies                |     |

|     |        | Functional Description              |     |

|     |        | Register Summary                    |     |

|     | 15.8.  | Register Description                | 126 |

| 16. |        | RL – System Controller              |     |

|     |        | Overview                            |     |

|     |        | Features                            |     |

|     |        | Block Diagram                       |     |

|     |        | Signal Description                  |     |

|     |        | Product Dependencies                |     |

|     | 16.6.  | Functional Description              | 148 |

|     | 16.7.  | Register Summary                    | 159 |

|     | 16.8   | Register Description                | 160 |

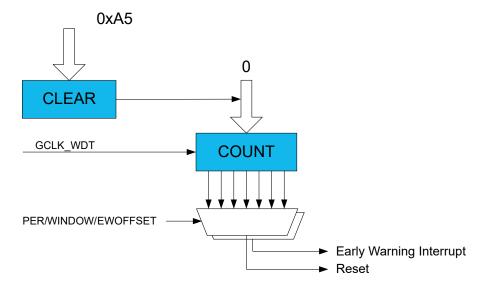

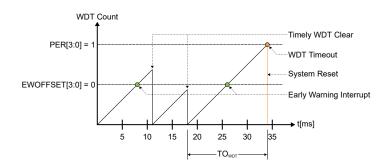

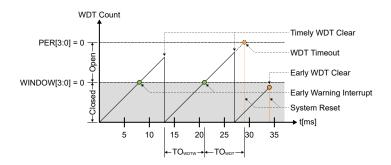

| 17. | WDT   | - Watchdog Timer                        | 190  |

|-----|-------|-----------------------------------------|------|

|     | 17.1. | Overview                                | 190  |

|     | 17.2. | Features                                | 190  |

|     | 17.3. | Block Diagram                           | 190  |

|     | 17.4. | Signal Description                      | 191  |

|     | 17.5. | Product Dependencies                    | 191  |

|     | 17.6. | Functional Description                  | 192  |

|     | 17.7. | Register Summary                        | 196  |

|     |       | Register Description                    |      |

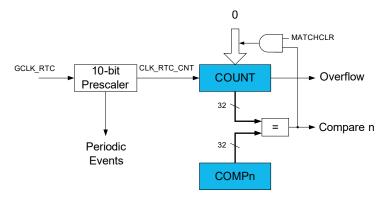

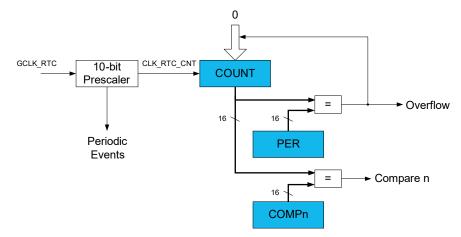

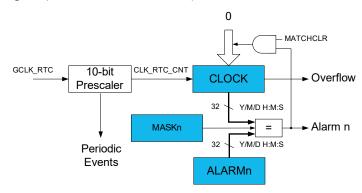

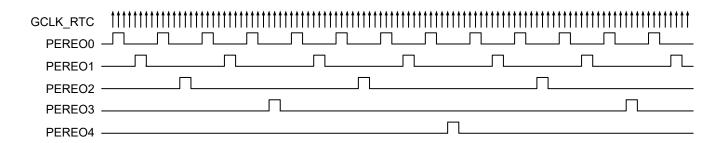

| 18. | RTC - | Real-Time Counter                       | 206  |

|     | 18.1. | Overview                                | 206  |

|     | 18.2. | Features                                | 206  |

|     | 18.3. | Block Diagram                           | 206  |

|     | 18.4. | Signal Description                      | 207  |

|     |       | Product Dependencies                    |      |

|     |       | Functional Description                  |      |

|     |       | Register Summary                        |      |

|     |       | Register Description                    |      |

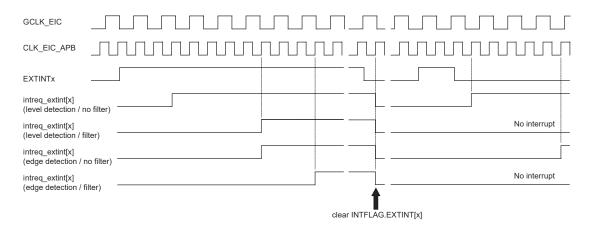

| 10  | FIC - | External Interrupt Controller           | 2/18 |

| ١). |       | Overview                                |      |

|     |       | Features                                |      |

|     |       | Block Diagram                           |      |

|     |       | Signal Description                      |      |

|     |       | Product Dependencies                    |      |

|     |       | Functional Description                  |      |

|     |       | Register Summary                        |      |

|     |       | Register Description                    |      |

|     |       |                                         |      |

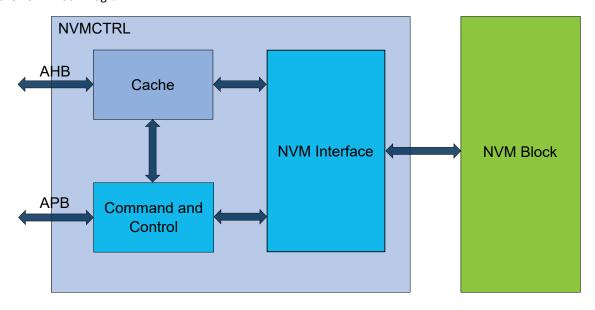

| 20. |       | CTRL – Nonvolatile Memory Controller    |      |

|     |       | Overview                                |      |

|     | 20.2. | Features                                | 265  |

|     |       | Block Diagram                           |      |

|     | 20.4. | Signal Description                      | 265  |

|     | 20.5. | Product Dependencies                    | 265  |

|     | 20.6. | Functional Description                  | 267  |

|     | 20.7. | Register Summary                        | 274  |

|     | 20.8. | Register Description                    | 274  |

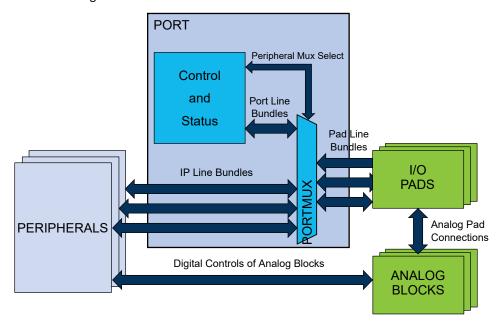

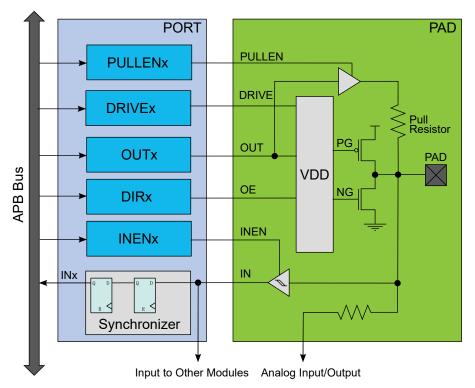

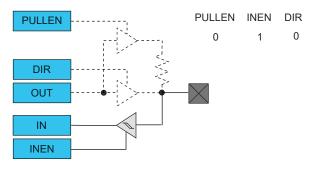

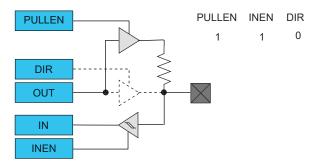

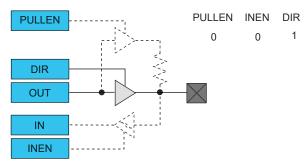

| 21. | PORT  | - I/O Pin Controller                    | 286  |

|     | 21.1. | Overview                                | 286  |

|     | 21.2. | Features                                | 286  |

|     |       | Block Diagram                           |      |

|     |       | Signal Description                      |      |

|     |       | Product Dependencies                    |      |

|     |       | Functional Description                  |      |

|     |       | Register Summary                        |      |

|     |       | PORT Pin Groups and Register Repetition |      |

|     |       | Register Description                    |      |

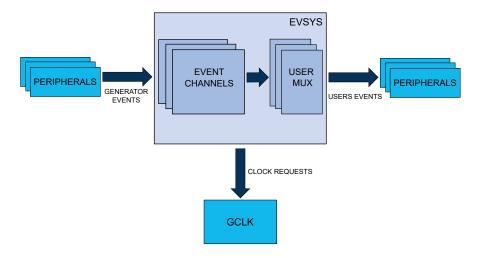

| 22. | Event    | System (EVSYS)                                 | 312 |

|-----|----------|------------------------------------------------|-----|

|     | 22.1.    | Overview                                       | 312 |

|     | 22.2.    | Features                                       | 312 |

|     | 22.3.    | Block Diagram                                  | 312 |

|     |          | Signal Description                             |     |

|     |          | Product Dependencies                           |     |

|     |          | Functional Description.                        |     |

|     |          | Register Summary                               |     |

|     |          | Register Description.                          |     |

|     |          |                                                |     |

| 23. |          | DM – Serial Communication Interface            |     |

|     |          | Overview                                       |     |

|     |          | Features                                       |     |

|     |          | Block Diagram                                  |     |

|     |          | Signal Description                             |     |

|     |          | Product Dependencies                           |     |

|     | 23.6.    | Functional Description                         | 332 |

| 24. | SERCO    | DM USART                                       | 338 |

|     | 24.1.    | Overview                                       | 338 |

|     | 24.2.    | USART Features                                 | 338 |

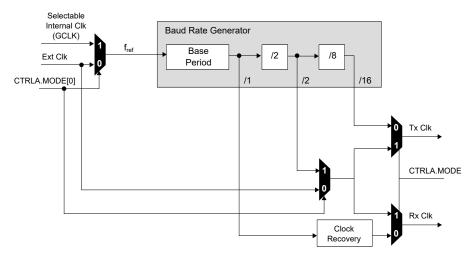

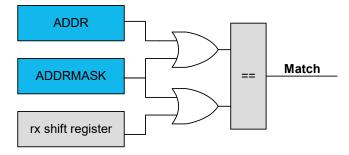

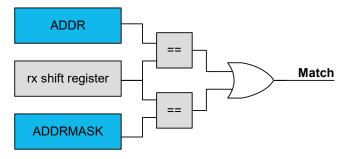

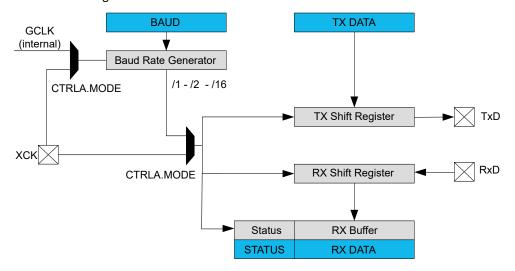

|     | 24.3.    | Block Diagram                                  | 339 |

|     |          | Signal Description                             |     |

|     |          | Product Dependencies                           |     |

|     |          | Functional Description                         |     |

|     |          | Register Summary                               |     |

|     |          | Register Description                           |     |

|     |          |                                                |     |

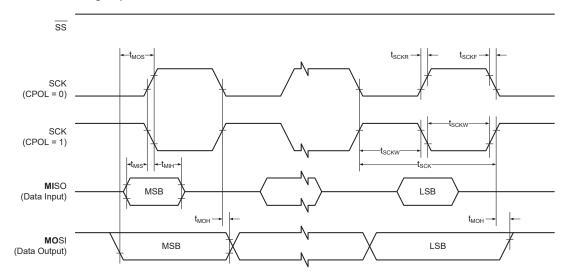

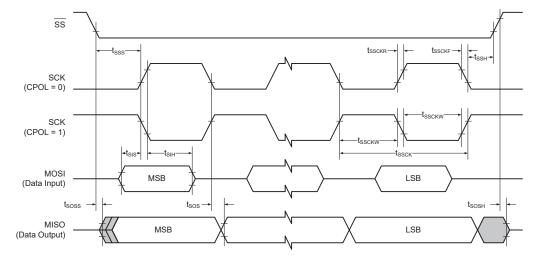

| 25. |          | DM SPI – SERCOM Serial Peripheral Interface    |     |

|     |          | Overview                                       |     |

|     | 25.2.    | Features                                       | 362 |

|     |          | Block Diagram                                  |     |

|     | 25.4.    | Signal Description                             | 363 |

|     | 25.5.    | Product Dependencies                           | 363 |

|     | 25.6.    | Functional Description                         | 364 |

|     | 25.7.    | Register Summary                               | 372 |

|     | 25.8.    | Register Description                           | 372 |

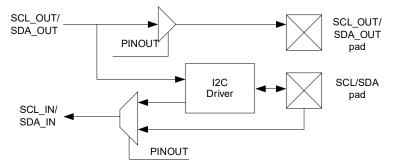

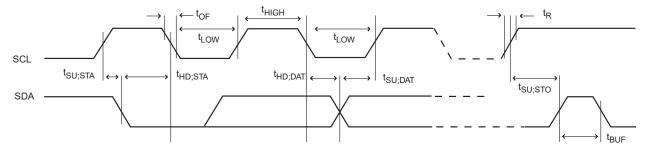

| 26. | SERCO    | DM I <sup>2</sup> C – Inter-Integrated Circuit | 386 |

|     | 26.1.    | Overview                                       | 386 |

|     |          | Features                                       |     |

|     |          | Block Diagram                                  |     |

|     |          | Signal Description                             |     |

|     |          | Product Dependencies                           |     |

|     |          | Functional Description                         |     |

|     |          | Register Summary - I2C Client                  |     |

|     |          | Register Description - I <sup>2</sup> C Client |     |

|     |          | Register Summary - I2C Host                    |     |

|     |          | Register Description - I <sup>2</sup> C Host   |     |

|     | ∠∪. I U. | NCEISICI DESCIBUIUII - I C 1103L               | 413 |

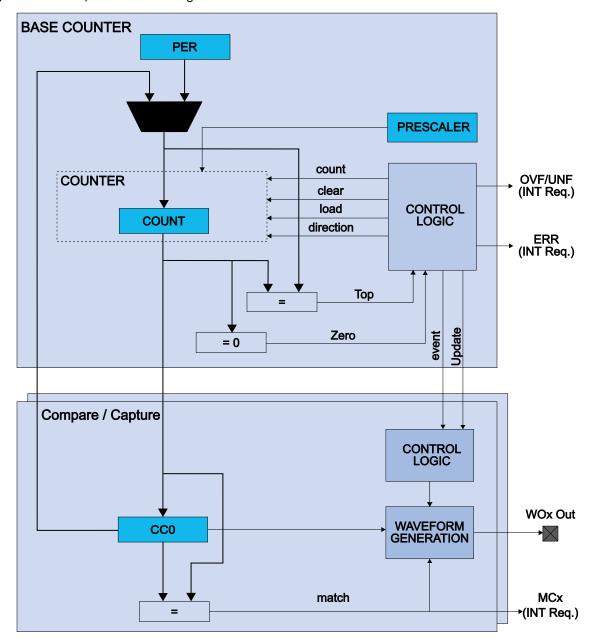

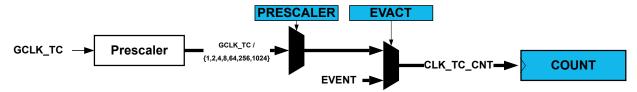

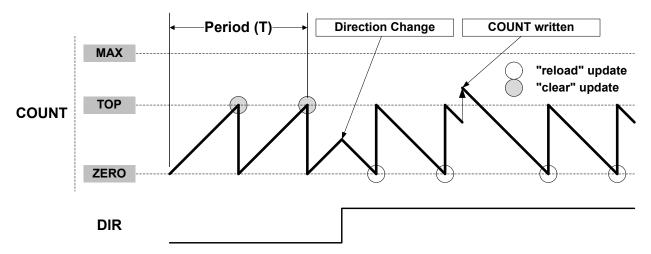

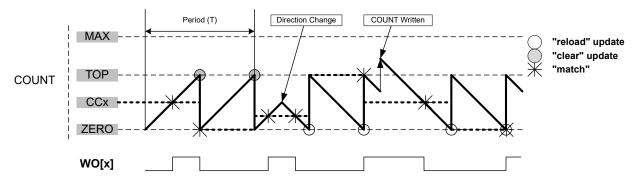

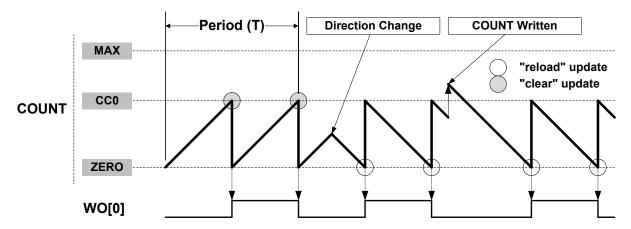

| 27. | TC – Timer/Counter                               | 427 |

|-----|--------------------------------------------------|-----|

|     | 27.1. Overview                                   | 427 |

|     | 27.2. Features                                   | 427 |

|     | 27.3. Block Diagram                              | 428 |

|     | 27.4. Signal Description                         |     |

|     | 27.5. Product Dependencies                       |     |

|     | 27.6. Functional Description                     |     |

|     | 27.7. Register Summary for 8-bit Registers       |     |

|     | 27.8. Register Description for 8-bit Registers   |     |

|     | 27.9. Register Summary for 16-bit Registers      |     |

|     | 27.10. Register Description for 16-bit Registers |     |

|     | 27.11. Register Summary for 32-bit Registers     |     |

|     | 27.12. Register Description for 32-bit Registers |     |

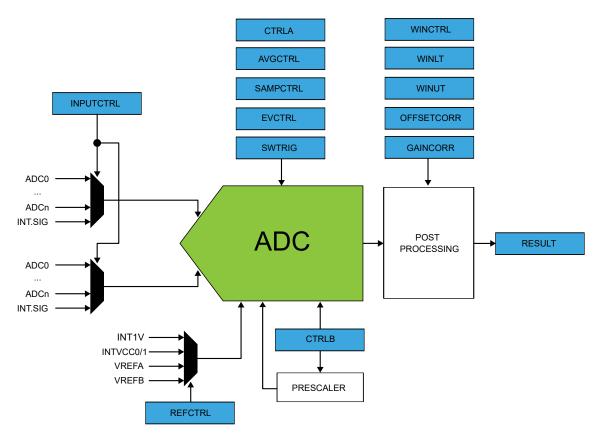

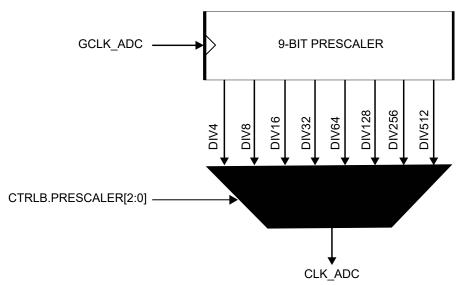

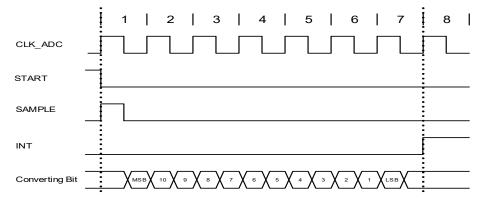

| 28  | Analog-to-Digital Converter (ADC)                | 186 |

| 20. | 28.1. Overview                                   |     |

|     |                                                  |     |

|     | 28.2. Features                                   |     |

|     | 28.3. Block Diagram                              |     |

|     | 28.4. Signal Description                         |     |

|     | 28.5. Product Dependencies                       |     |

|     | 28.6. Functional Description                     |     |

|     | 28.7. Register Summary                           |     |

|     | 28.8. Register Description                       | 498 |

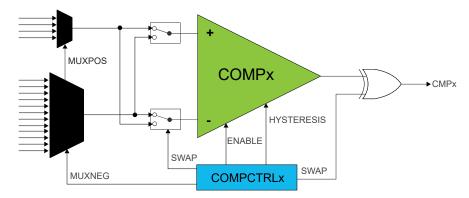

| 29. | AC – Analog Comparators                          | 522 |

|     | 29.1. Overview                                   | 522 |

|     | 29.2. Features                                   | 522 |

|     | 29.3. Block Diagram                              | 523 |

|     | 29.4. Signal Description                         | 523 |

|     | 29.5. Product Dependencies                       | 523 |

|     | 29.6. Functional Description                     |     |

|     | 29.7. Register Summary                           | 535 |

|     | 29.8. Register Description                       | 535 |

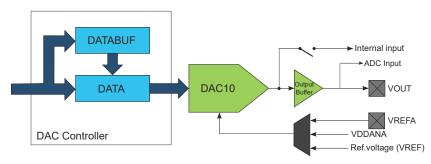

| 30. | DAC – Digital-to-Analog Converter                | 550 |

|     | 30.1. Overview                                   | 550 |

|     | 30.2. Features                                   | 550 |

|     | 30.3. Block Diagram                              |     |

|     | 30.4. Signal Description                         |     |

|     | 30.5. Product Dependencies                       |     |

|     | 30.6. Functional Description                     |     |

|     | 30.7. Register Summary                           |     |

|     | 30.8. Register Description                       |     |

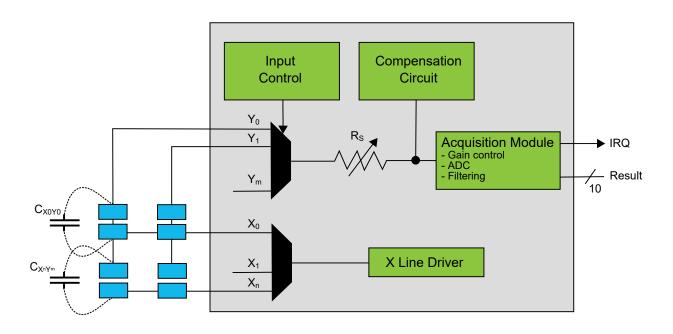

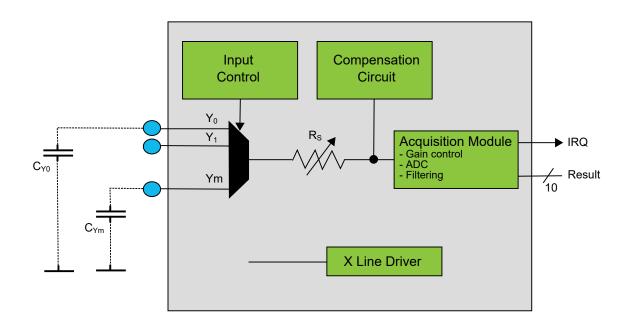

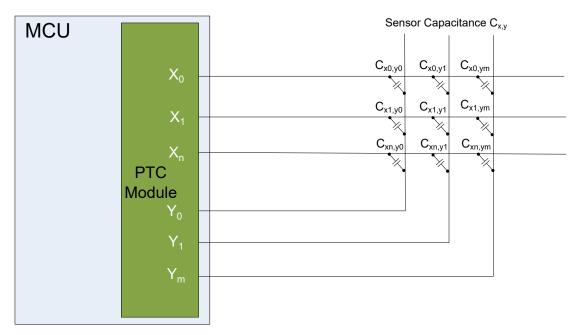

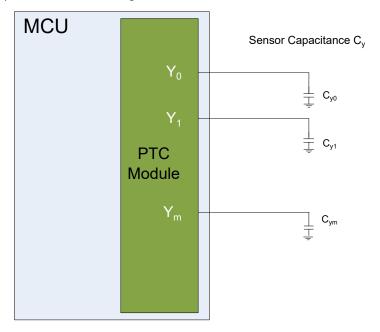

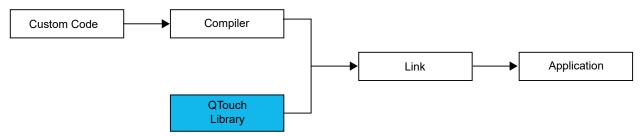

| 31  | PTC - Peripheral Touch Controller                | 565 |

| ٠., | 31.1. Overview                                   |     |

|     | 31.2. Features                                   |     |

|     | 31.3. Block Diagram                              |     |

|     | 31.4. Signal Description                         |     |

|     | 31.5. System Dependencies                        |     |

|     | 31.6.   | Functional Description                           | 568   |

|-----|---------|--------------------------------------------------|-------|

| 32. | Electri | cal Characteristics at 85°C                      | .569  |

|     | 32.1.   | Disclaimer                                       | . 569 |

|     | 32.2.   | Absolute Maximum Ratings                         | 569   |

|     | 32.3.   | General Operating Ratings                        | 570   |

|     | 32.4.   | Supply Characteristics                           | .570  |

|     | 32.5.   | Maximum Clock Frequencies                        | 571   |

|     | 32.6.   | Power Consumption                                | .572  |

|     | 32.7.   | Peripheral Power Consumption                     | .576  |

|     | 32.8.   | I/O Pin Characteristics                          | .577  |

|     | 32.9.   | Injection Current                                | . 579 |

|     | 32.10.  | Analog Characteristics                           | 579   |

|     | 32.11.  | NVM Characteristics                              | .591  |

|     | 32.12.  | Oscillators Characteristics                      | .592  |

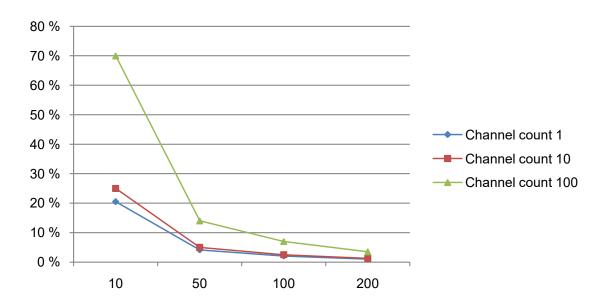

|     | 32.13.  | PTC Typical Characteristics                      | .596  |

|     | 32.14.  | Timing Characteristics                           | .599  |

| 33. | Electri | cal Characteristics at 105°C                     | .604  |

|     | 33.1.   | Disclaimer                                       | .604  |

|     | 33.2.   | Absolute Maximum Ratings                         | 604   |

|     | 33.3.   | General Operating Ratings                        | 604   |

|     | 33.4.   | Maximum Clock Frequencies                        | 605   |

|     | 33.5.   | Power Consumption                                | .606  |

|     | 33.6.   | Injection Current                                | .609  |

|     | 33.7.   | Analog Characteristics                           | .610  |

|     | 33.8.   | NVM Characteristics                              | 618   |

|     | 33.9.   | Oscillators Characteristics                      | 618   |

| 34. | AEC-Q   | 100 Electrical Characteristics at 125 $^{\circ}$ | .623  |

|     | 34.1.   | Disclaimer                                       | 623   |

|     | 34.2.   | Absolute Maximum Ratings                         | 623   |

|     | 34.3.   | General Operating Ratings                        | 625   |

|     | 34.4.   | Supply Characteristics                           | .625  |

|     | 34.5.   | Maximum Clock Frequencies                        | 625   |

|     | 34.6.   | Power Consumption                                | .626  |

|     |         | Peripheral Power Consumption                     |       |

|     | 34.8.   | I/O Pin Characteristics                          | .630  |

|     | 34.9.   | Injection Current                                | .631  |

|     | 34.10.  | Analog Characteristics                           | 632   |

|     | 34.11.  | NVM Characteristics                              | .639  |

|     |         | Oscillators Characteristics                      |       |

|     |         | PTC Characteristics                              |       |

|     | 34.14.  | Timing Characteristics                           | .645  |

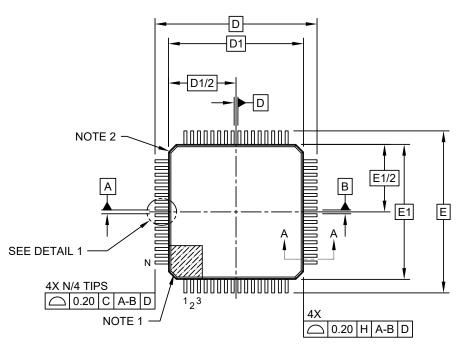

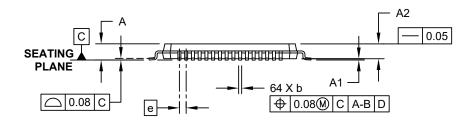

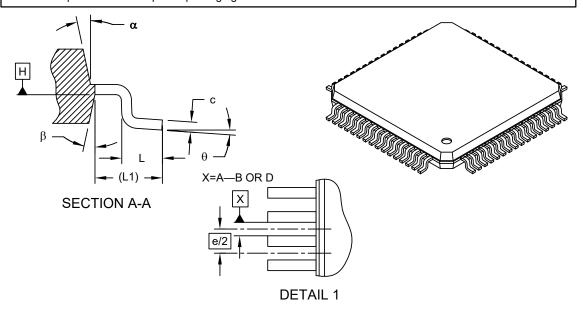

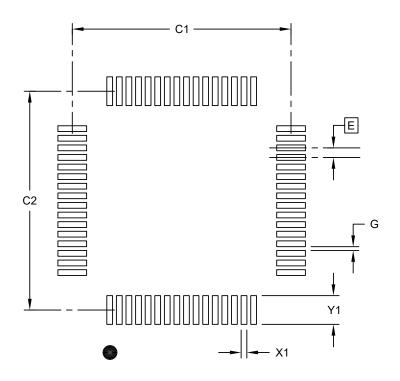

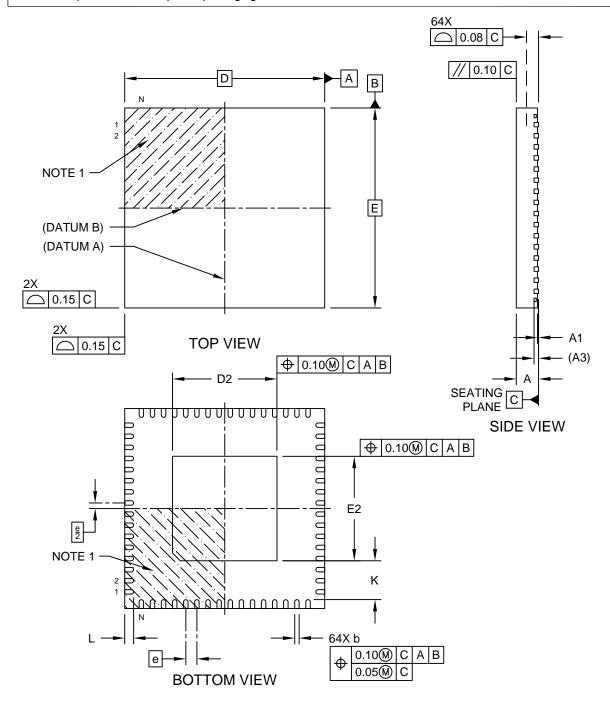

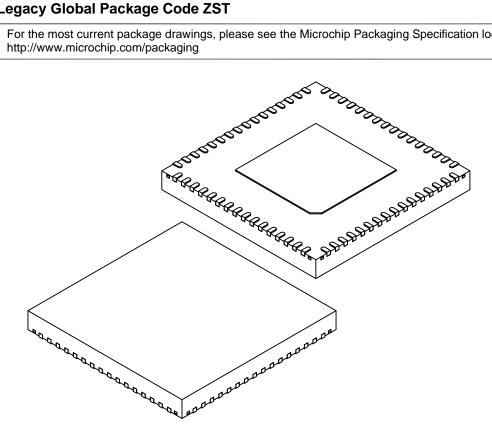

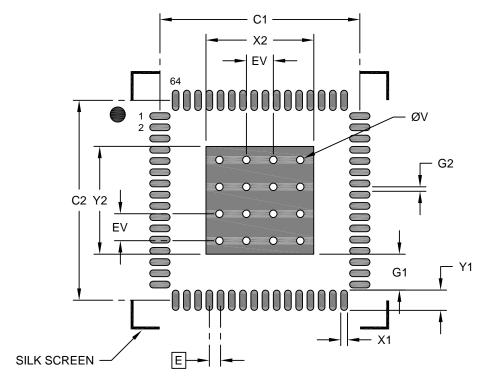

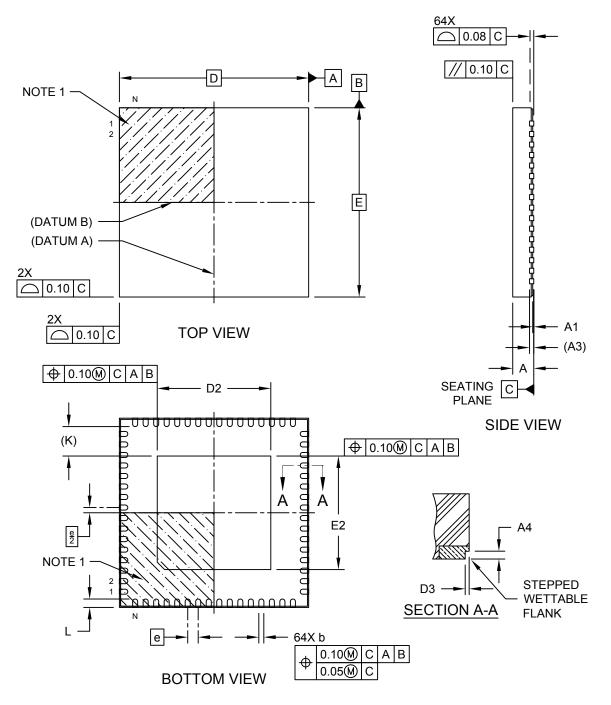

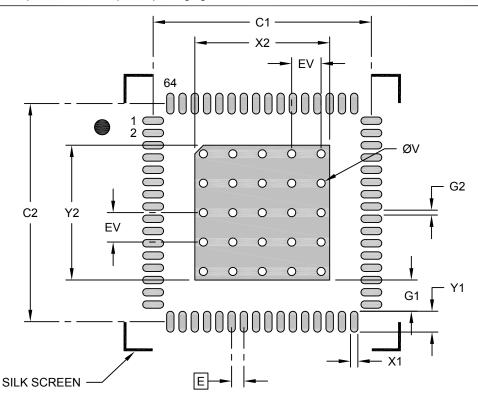

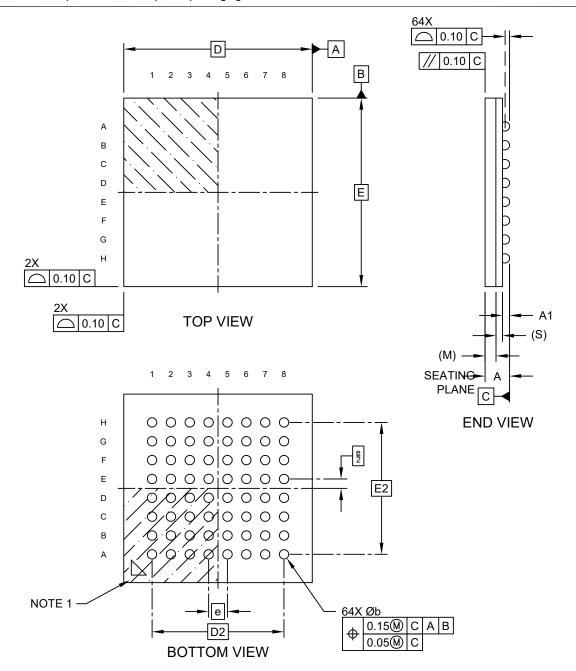

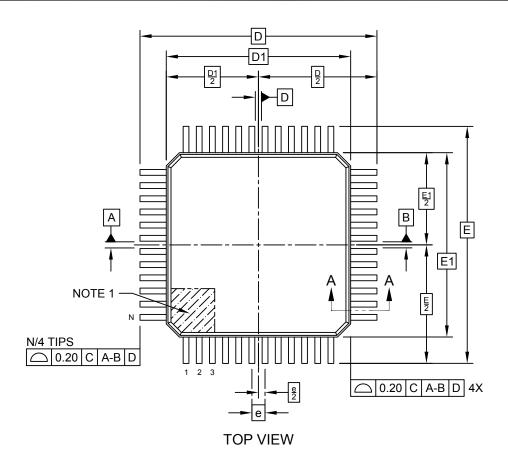

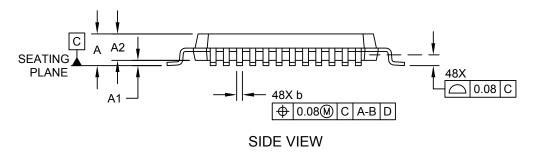

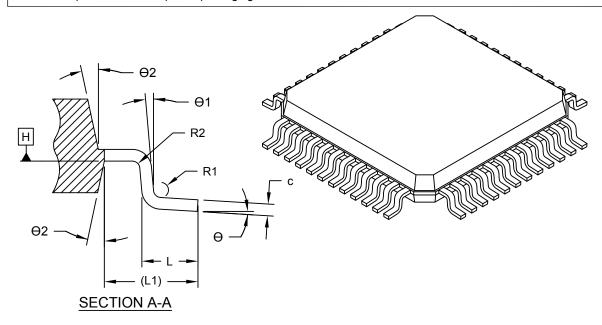

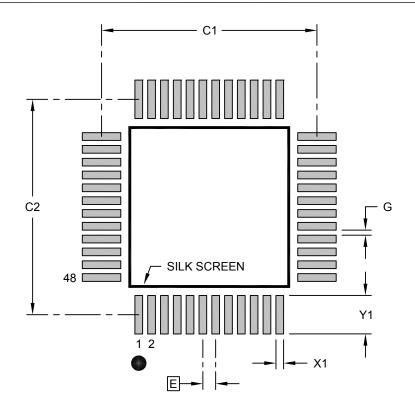

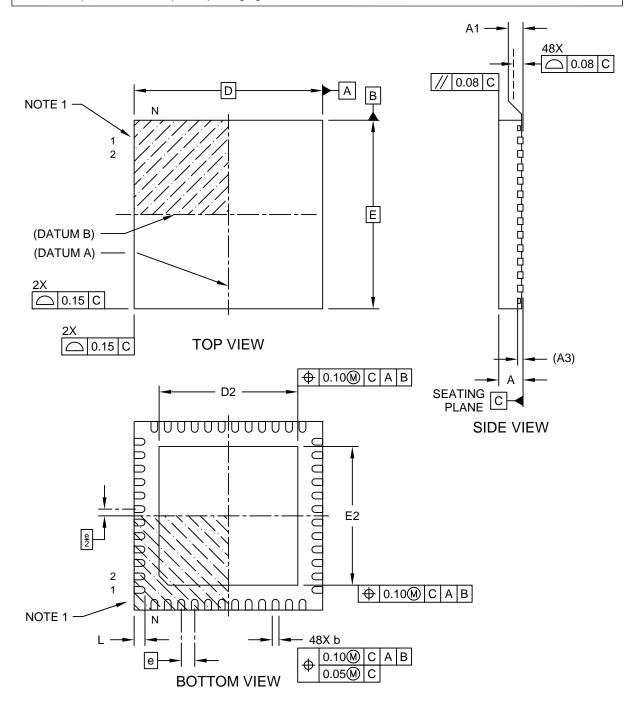

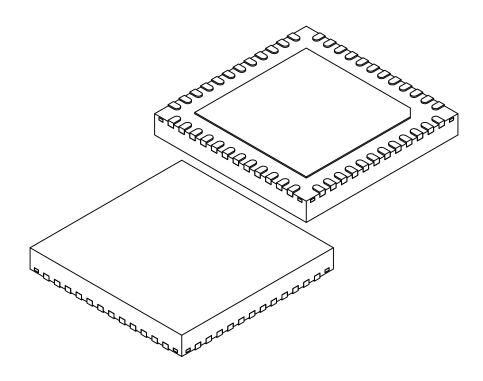

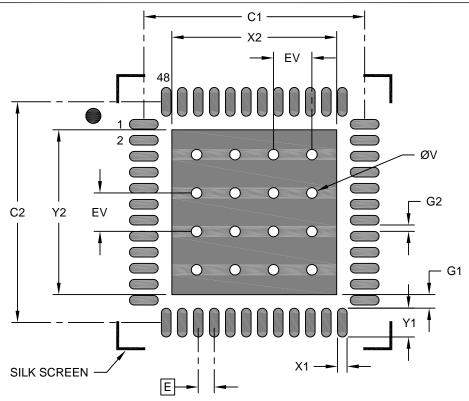

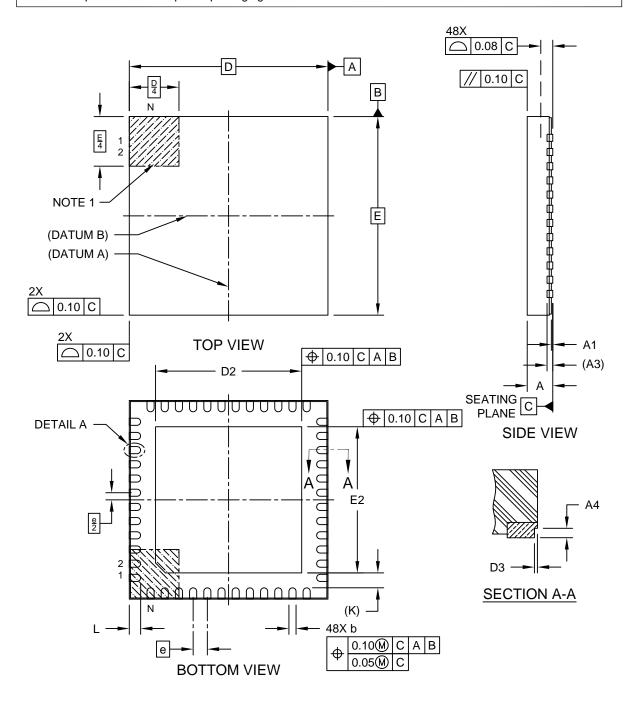

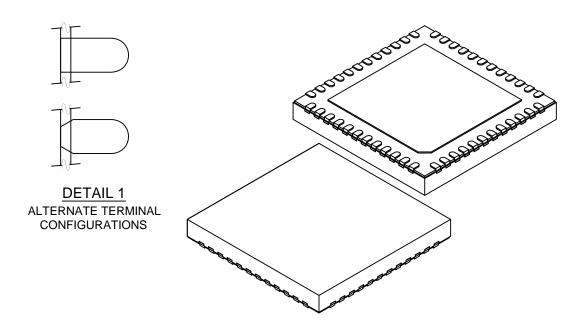

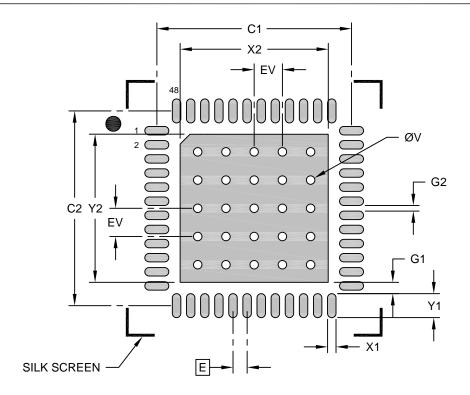

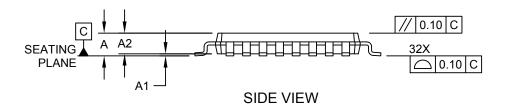

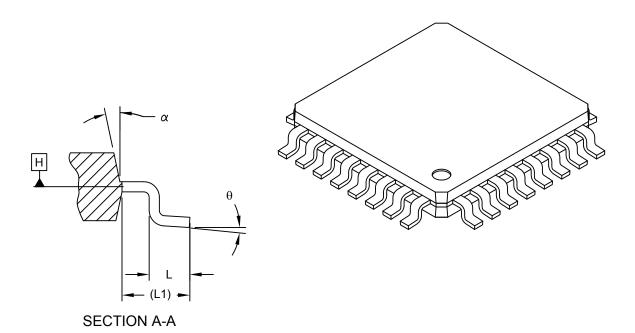

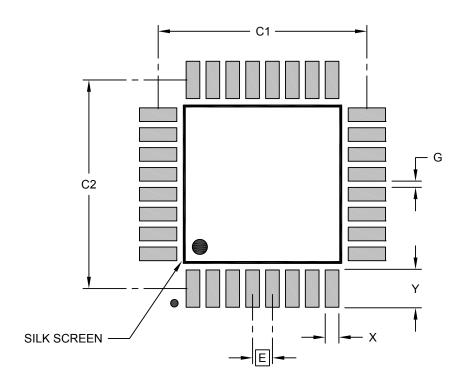

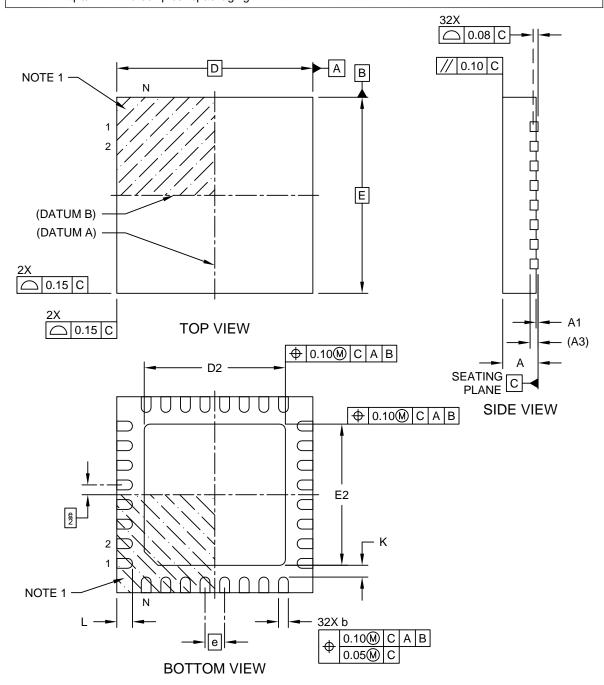

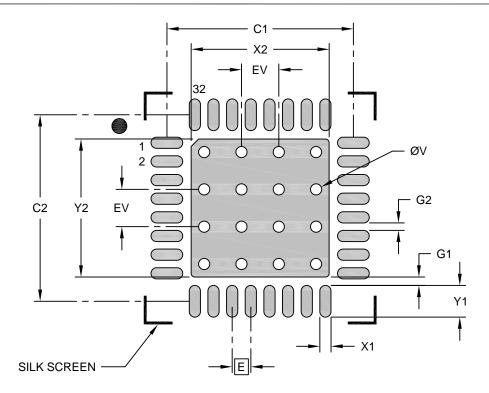

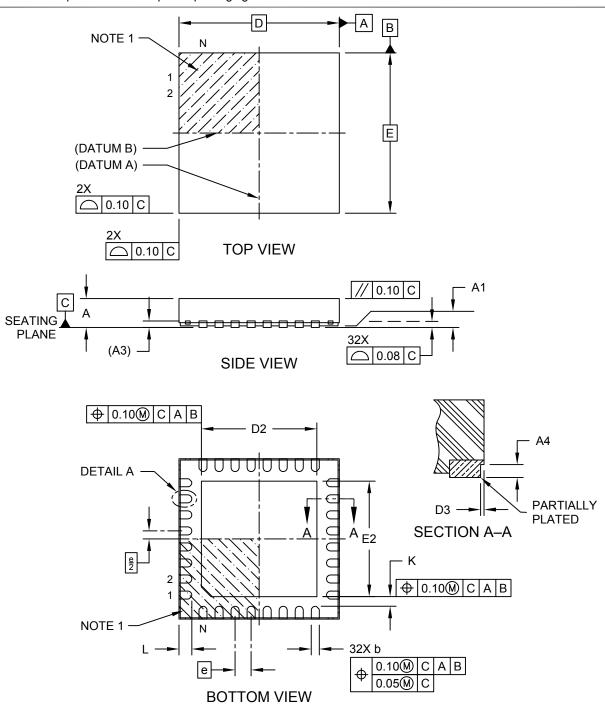

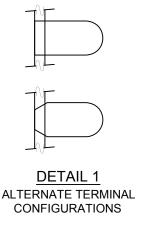

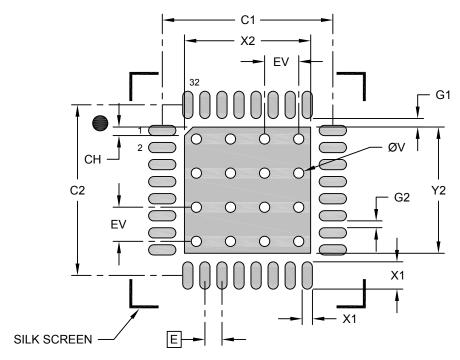

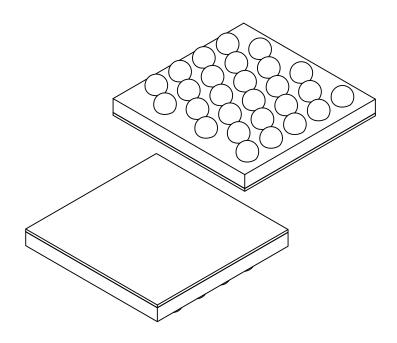

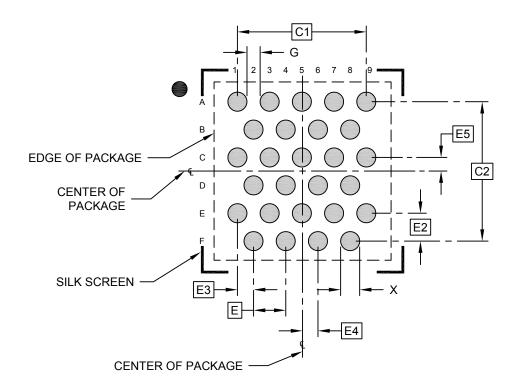

| 35. | Packa   | ging Information                                 | 650   |

|     | 35.1.   | Thermal Considerations                           | .650  |

|     | 35.2.   | Package Drawings                                 | .651  |

|     | 25.2    | Soldering Profile                                | 606   |

| 36. Schema   | itic Checklist                       | 697 |

|--------------|--------------------------------------|-----|

| 36.1. li     | ntroduction                          | 697 |

| 36.2. P      | ower Supply                          | 697 |

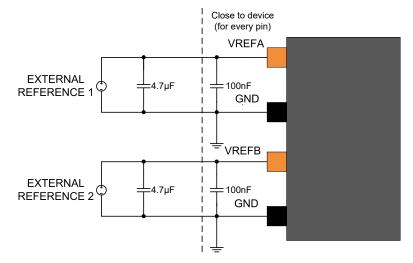

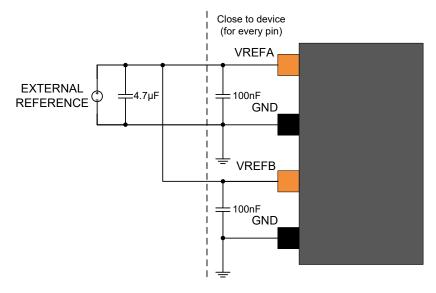

| 36.3. E      | xternal Analog Reference Connections | 699 |

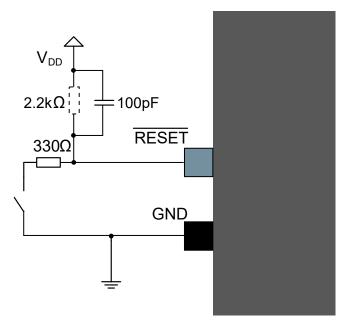

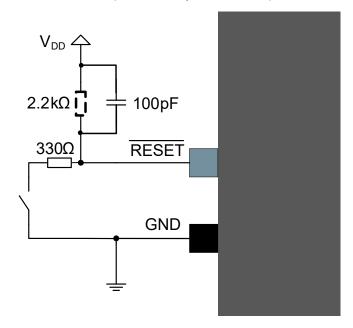

| 36.4. E      | xternal Reset Circuit                | 700 |

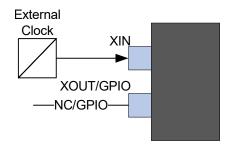

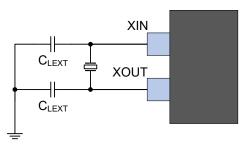

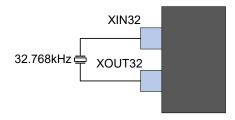

| 36.5. C      | clocks and Crystal Oscillators       | 701 |

| 36.6. L      | Inused or Unconnected Pins           | 703 |

| 36.7. P      | rogramming and Debug Ports           | 703 |

| 37. Datash   | eet Revision History                 | 707 |

| 37.1. F      | levision G - 08/2023                 | 707 |

| 37.2. F      | levision F - 03/2022                 | 707 |

| 37.3. F      | levision E - 11/2020                 | 707 |

| 37.4. F      | levision D - 03/2020                 | 708 |

| 37.5. R      | levision C - 11/2019                 | 709 |

| 37.6. F      | lev. B - 11/2017                     | 710 |

| 37.7. F      | lev. A - 08/2017                     | 710 |

| 37.8. F      | lev. P - 09/2016                     | 710 |

| 37.9. F      | lev. O - 08/2016                     | 711 |

| 37.10.       | Rev. N - 01/2015                     | 711 |

| 37.11.       | Rev. M - 12/2014                     | 712 |

| 37.12.       | Rev. L - 09/2014                     | 713 |

| 37.13.       | Rev. K – 05/2014                     | 714 |

| 37.14.       | Rev. J – 12/2013                     | 716 |

| 37.15.       | Rev. I 12/2013                       | 716 |

| 37.16.       | Rev. H 10/2013                       | 723 |

| 37.17.       | Rev. G - 10/2013                     | 724 |

| 37.18.       | Rev. F - 10/2013                     | 725 |

| 37.19.       | Rev. E - 09/2013                     | 725 |

| 37.20.       | Rev. D - 08/2013                     | 725 |

| 37.21.       | Rev. C – 07/2013                     | 726 |

| 37.22.       | Rev. B – 07/2013                     | 727 |

| 37.23.       | Rev. A - 06/2013                     | 728 |

| 38. Conven   | tions                                | 729 |

| 38.1. N      | Jumerical Notation                   | 729 |

| 38.2. N      | Memory Size and Type                 | 729 |

|              | requency and Time                    |     |

|              | legisters and Bits                   |     |

| 39. Acronyr  | ns and Abbreviations                 | 731 |

| The Microch  | nip Website                          | 733 |

| Product Cha  | ange Notification Service            | 733 |

|              | upport                               |     |

|              |                                      |     |

| ·            | evices Code Protection Feature       |     |

| Legal Notice | 3                                    | 733 |

| Trademarks                  | 734  |

|-----------------------------|------|

| Quality Management System   | .735 |

| Worldwide Sales and Service | 736  |

# 1. Configuration Summary

Table 1-1. SAM D20 Device-Specific Features

| Device      | Flash (KB) | SRAM (KB) |

|-------------|------------|-----------|

| ATSAMD20E14 | 16         | 2         |

| ATSAMD20E15 | 32         | 4         |

| ATSAMD20E16 | 64         | 8         |

| ATSAMD20E17 | 128        | 16        |

| ATSAMD20E18 | 256        | 32        |

| ATSAMD20G14 | 16         | 2         |

| ATSAMD20G15 | 32         | 4         |

| ATSAMD20G16 | 64         | 8         |

| ATSAMD20G17 | 128        | 16        |

| ATSAMD20G18 | 256        | 32        |

| ATSAMD20J14 | 16         | 2         |

| ATSAMD20J15 | 32         | 4         |

| ATSAMD20J16 | 64         | 8         |

| ATSAMD20J17 | 128        | 16        |

| ATSAMD20J18 | 256        | 32        |

**Table 1-2.** SAM D20 Family Features

| Feature                                           | SAM D20J                  | SAM 20             | OG               | SAM D20E            |          |  |

|---------------------------------------------------|---------------------------|--------------------|------------------|---------------------|----------|--|

| Packages                                          | VQFN64/TQFP64/<br>UFBGA64 | VQFN48/TQFP48      | WLCSP45          | VQFN32/TQFP32       | WLCSP27  |  |

| Pins                                              | 64                        | 48                 | 45               | 32                  | 27       |  |

| General Purpose I/O pins (GPIOs)                  | 52                        | 38                 | 35               | 26                  | 22       |  |

| Flash                                             | 256/128/64/32             | /16 KB             | 256/128 KB       | 256/128/64/32/16 KB | 64/32 KB |  |

| SRAM                                              | 32/16/8/4/2               | КВ                 | 32/16 KB         | 32/16/8/4/2 KB      | 8/4 KB   |  |

| Timer Counter (TC) instances                      | 8                         |                    |                  | 6                   |          |  |

| Waveform output channels per TC instance          | 2 <sup>(1)</sup>          |                    |                  |                     |          |  |

| Serial Communication Interface (SERCOM) instances | 6 4(2)                    |                    | 4 <sup>(2)</sup> |                     |          |  |

| Analog-to-Digital Converter (ADC) channels        | 20                        | 20 14              |                  | 10                  | 10       |  |

| Analog Comparators (AC)                           |                           |                    | 2                |                     |          |  |

| Digital-to-Analog Converter (DAC) channels        |                           |                    | 1                |                     |          |  |

| Real-Time Counter (RTC)                           |                           | Υ                  | es               |                     |          |  |

| RTC alarms                                        |                           |                    | 1                |                     |          |  |

| RTC compare values                                |                           | One 32-bit value o | r two 16-bit     | values              |          |  |

| External Interrupt lines                          | 16                        |                    | 14               |                     |          |  |

| Peripheral Touch Controller (PTC) X and Y lines   | 16x16 12x10 10x6          |                    | 10x6             | 9x6                 |          |  |

| Maximum CPU frequency 48MHz                       |                           |                    |                  |                     |          |  |

| continued             |                                                                                 |                                                |         |               |         |

|-----------------------|---------------------------------------------------------------------------------|------------------------------------------------|---------|---------------|---------|

| Feature               | SAM D20J                                                                        | SAM 20                                         | G       | SAM D20E      |         |

| Packages              | VQFN64/TQFP64/<br>UFBGA64                                                       | VQFN48/TQFP48                                  | WLCSP45 | VQFN32/TQFP32 | WLCSP27 |

|                       | 32.768 kHz crystal oscillator (XOSC32K)<br>0.4-32 MHz crystal oscillator (XOSC) |                                                |         |               |         |

|                       | 32.768 kHz internal oscillator (OSC32K)                                         |                                                |         |               |         |

| Oscillators           | 32 kHz ultra low-power internal oscillator (OSCULP32K)                          |                                                |         |               |         |

|                       | 8 MHz high-accuracy internal oscillator (OSC8M)                                 |                                                |         |               |         |

|                       | 48 MH                                                                           | 48 MHz Digital Frequency Locked Loop (DFLL48M) |         |               |         |

| Event System channels | 8                                                                               |                                                |         |               |         |

| SW Debug Interface    | Yes                                                                             |                                                |         |               |         |

| Watchdog Timer (WDT)  | Yes                                                                             |                                                |         |               |         |

#### Notes:

- 1. The WLCSP27 package does not contain TC4/WO[1] and TC5/WO[0],TC5/WO[1] outputs.

- 2. SERCOM4/SERCOM5 are not available on the VQFN32/TQFP32 and WLCSP27 packages.

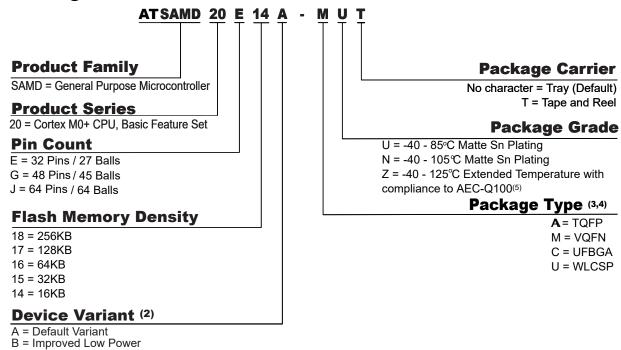

# 2. Ordering Information (1)

### Note:

- 1. Not all combinations are valid. The available device part numbers are listed in configuration Summary.

- 2. Variant B is available only for Flash memory density of 64 KB, 32 KB, and 16 KB.

- 3. Devices in the WLCSP45 package include a factory programmed Boot Loader. Contact your local Microchip sales office for additional information.

- 4. Devices in the WLCSP27 package include a factory programmed Boot Loader. For additional information, refer to the MPLAB Harmony v3 Boot Loader documentation.

- 5. AEC-Q100 grading is only available for Variant B.

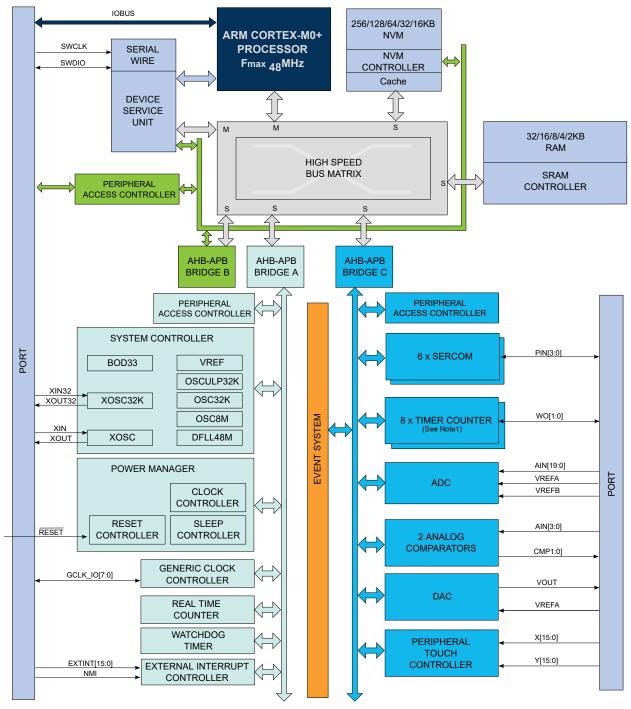

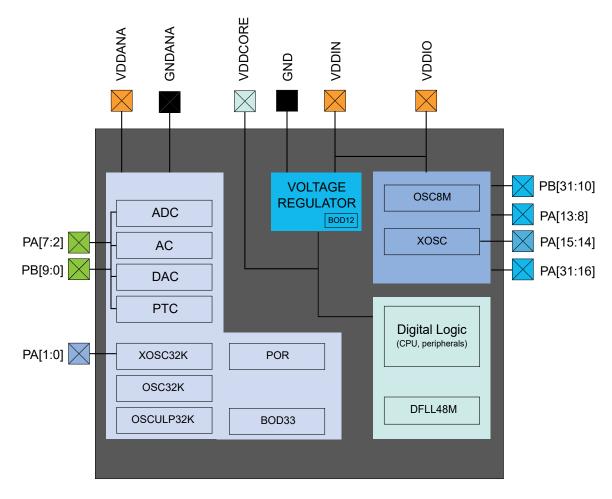

# 3. Block Diagram

**Note:** 1. Some products have different number of SERCOM instances, Timer/Counter instances, PTC signals and ADC signals. Refer to *Peripherals Configuration Summary* for details.

#### **Related Links**

11. Peripherals Configuration Summary

## 4. Pinout

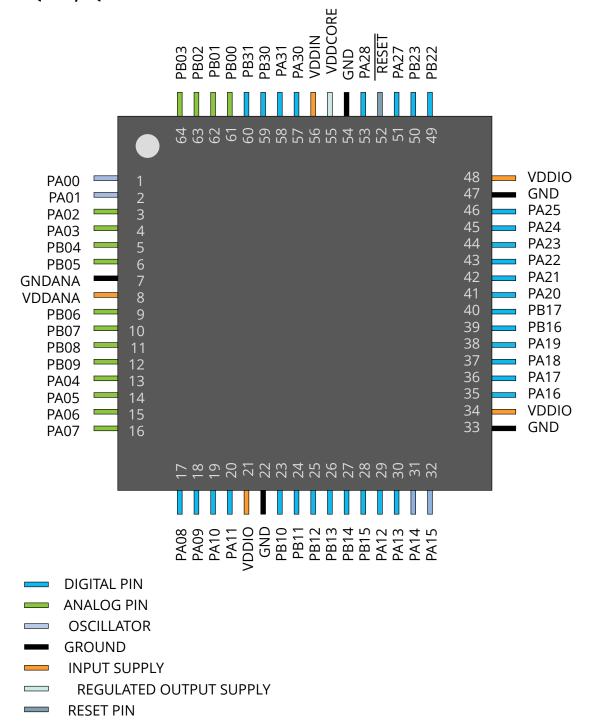

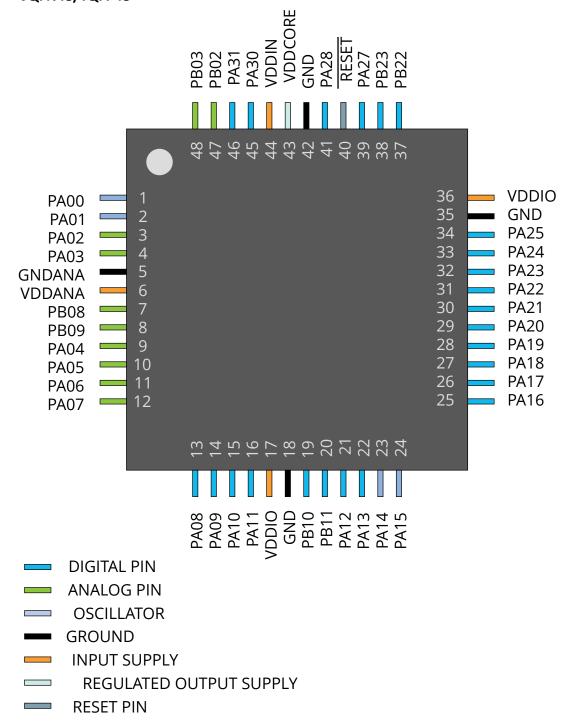

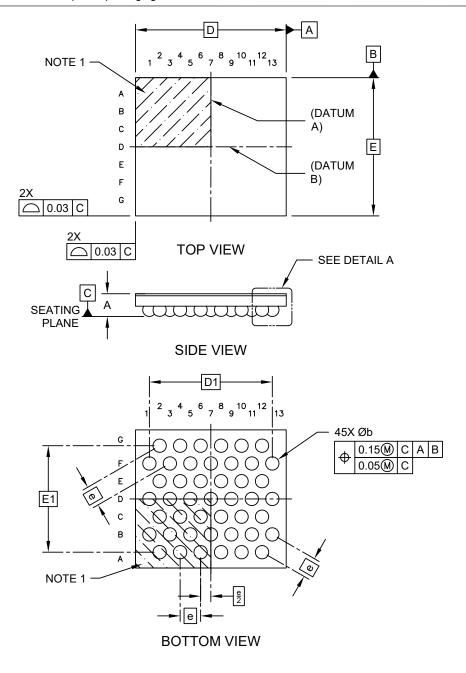

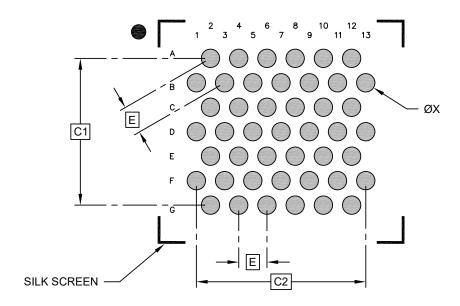

# 4.1 SAM D20J

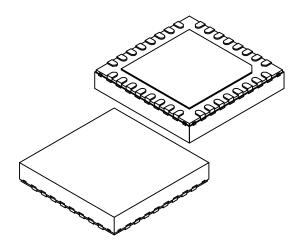

#### 4.1.1 VQFN64/TQFP64

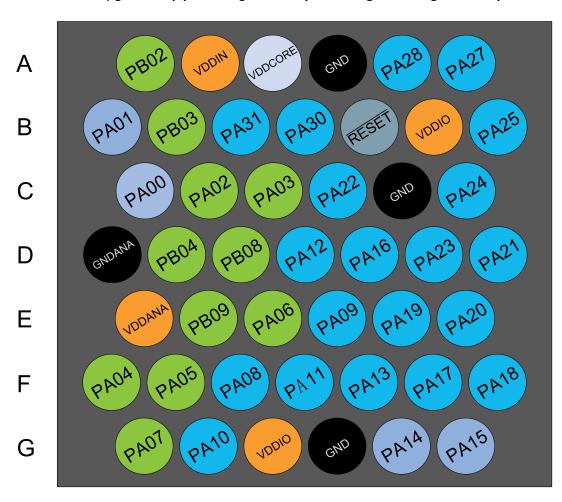

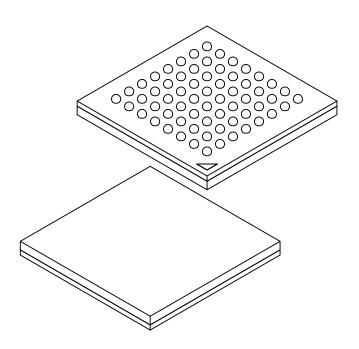

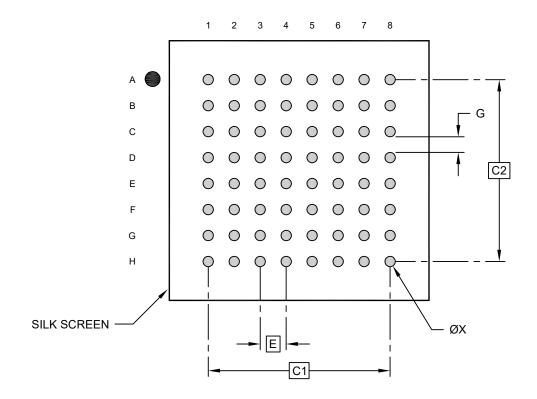

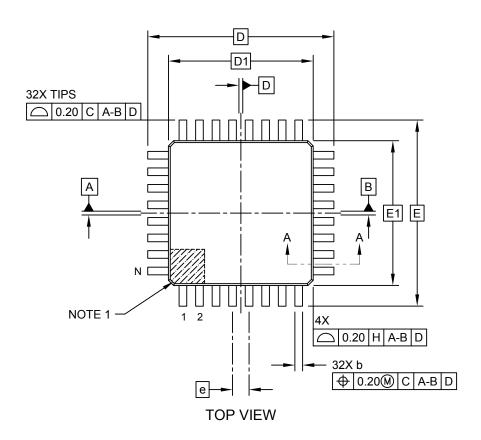

#### 4.1.2 UFBGA64

- DIGITAL PIN

- ANALOG PIN

- OSCILLATOR

- GROUND

- INPUT SUPPLY

- REGULATED OUTPUT SUPPLY

- RESET PIN

## 4.2 SAM D20G

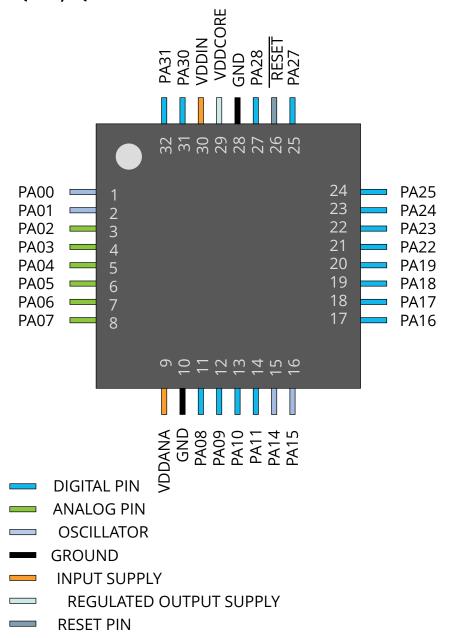

## 4.2.1 VQFN48/TQFP48

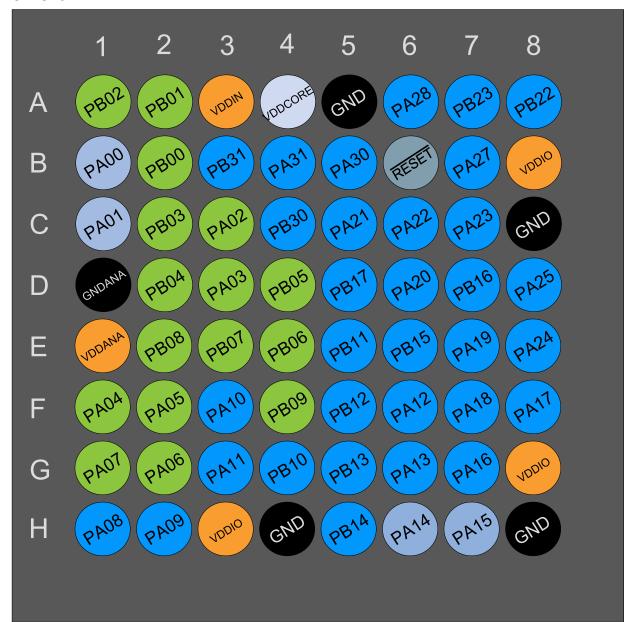

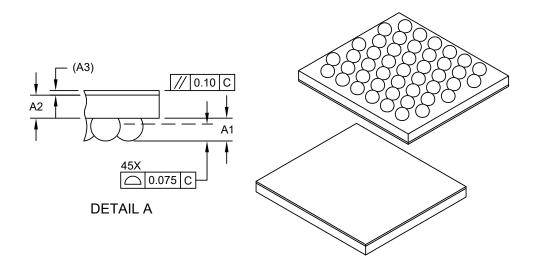

#### 4.2.2 WLCSP45

12 10 8 6 4 2 13 11 9 7 5 3 1

- DIGITAL PIN

- ANALOG PIN

- OSCILLATOR

- GROUND

- INPUT SUPPLY

- REGULATED OUTPUT SUPPLY

- RESET PIN

## 4.3 SAM D20E

# 4.3.1 VQFN32/TQFP32

**Note:** In the VQFN32/TQFP32 package, both VDDIO and VDDANA are internally connected.

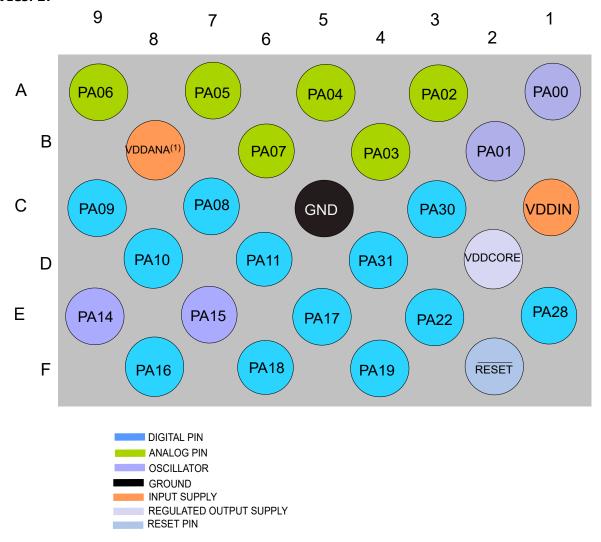

#### 4.3.2 WLCSP27

#### Note:

1. In the WLCSP27 package, both VDDIO and VDDANA are internally connected.

# 5. Signal Descriptions List

The following table provides details on signal names classified by peripherals.

| Signal Name                              | Function                                                       | Туре           | Active Level |  |  |

|------------------------------------------|----------------------------------------------------------------|----------------|--------------|--|--|

| Analog Comparators - AC                  |                                                                |                |              |  |  |

| AIN[3:0]                                 | AC Analog Inputs                                               | Analog         |              |  |  |

| CMP[1:0]                                 | AC Comparator Outputs                                          | Digital        |              |  |  |

| Analog-to-Digita                         | ll Converter (ADC)                                             |                |              |  |  |

| AIN[19:0]                                | ADC Analog Inputs                                              | Analog         |              |  |  |

| VREFA                                    | ADC Voltage External Reference A                               | Analog         |              |  |  |

| VREFB                                    | ADC Voltage External Reference B                               | Analog         |              |  |  |

| Digital-to-Analog                        | g Converter (DAC)                                              |                |              |  |  |

| VOUT                                     | DAC Voltage output                                             | Analog         |              |  |  |

| VREFA                                    | DAC Voltage External Reference                                 | Analog         |              |  |  |

| External Interru                         | pt Controller                                                  |                |              |  |  |

| EXTINT[15:0]                             | External Interrupts                                            | Input          |              |  |  |

| NMI                                      | External Non-Maskable Interrupt                                | Input          |              |  |  |

| Generic Clock G                          | enerator - GCLK                                                |                |              |  |  |

| GCLK_IO[7:0]                             | Generic Clock (source clock or generic clock generator output) | I/O            |              |  |  |

| Power Manager                            | - PM                                                           |                |              |  |  |

| RESET                                    | Reset                                                          | Input          | Low          |  |  |

| Serial Communication Interface - SERCOMx |                                                                |                |              |  |  |

| PAD[3:0]                                 | SERCOM I/O Pads                                                | I/O            |              |  |  |

| System Control                           | - SYSCTRL                                                      |                |              |  |  |

| XIN                                      | Crystal Input                                                  | Analog/Digital |              |  |  |

| XIN32                                    | 32 kHz Crystal Input                                           | Analog/Digital |              |  |  |

| XOUT                                     | Crystal Output                                                 | Analog         |              |  |  |

| XOUT32                                   | 32 kHz Crystal Output                                          | Analog         |              |  |  |

| Timer Counter -                          | TCx                                                            |                |              |  |  |

| WO[1:0]                                  | Waveform Outputs                                               | Output         |              |  |  |

| Peripheral Touc                          | h Controller - PTC                                             |                |              |  |  |

| X[15:0]                                  | PTC Output                                                     | Analog         |              |  |  |

| Y[15:0]                                  | PTC Input/Output                                               | Analog         |              |  |  |

| General Purpos                           | e I/O - PORT                                                   |                |              |  |  |

| PA25 - PA00                              | Parallel I/O Controller I/O Port A                             | I/O            |              |  |  |

| PA28 - PA27                              | Parallel I/O Controller I/O Port A                             | I/O            |              |  |  |

| PA31 - PA30                              | Parallel I/O Controller I/O Port A                             | I/O            |              |  |  |

| PB17 - PB00                              | Parallel I/O Controller I/O Port B                             | I/O            |              |  |  |

| PB23 - PB22                              | Parallel I/O Controller I/O Port B                             | I/O            |              |  |  |

| PB31 - PB30                              | Parallel I/O Controller I/O Port B                             | I/O            |              |  |  |

# 6. I/O Multiplexing and Considerations

**Related Links**

32.8.2. I2C Pins

# 6.1 Multiplexed Signals

Each pin is by default controlled by the PORT as a general purpose I/O and alternatively it can be assigned to one of the peripheral functions A, B, C, D, E, F, G, or H. To enable a peripheral function on a pin, the Peripheral Multiplexer Enable bit in the Pin Configuration register corresponding to that pin (PINCFGn.PMUXEN, n = 0-31) in the PORT must be written to one. The selection of peripheral function A to H is done by writing to the Peripheral Multiplexing Odd and Even bits in the Peripheral Multiplexing register (PMUXn.PMUXE/O) in the PORT.

This table describes the peripheral signals multiplexed to the PORT I/O pins.

Table 6-1. PORT Function Multiplexing

|                                         | Pin/Ball                                |                                         | I/O  | Supply | Туре             | Α          |                                |         | B <sub>(2)</sub> |       |      | C_(1)              | D(1)               | Е             | F             | G   | н          |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|------|--------|------------------|------------|--------------------------------|---------|------------------|-------|------|--------------------|--------------------|---------------|---------------|-----|------------|

| SAM D20E<br>(VQFN32,TQFP32/<br>WLCSP27) | SAM D20G<br>(VQFN48,TQFP48/<br>WLCSP45) | SAM D20J<br>(VQFN64,TQFP64/<br>UFBGA64) | Pin  |        |                  | EIC        | REF                            | ADC     | AC               | PTC   | DAC  | SERCOM(3)          | SERCOM-<br>ALT     | T             | C(4)          | СОМ | AC/GCLK    |

| 1/A1                                    | 1/C12                                   | 1/B1                                    | PA00 | VDDANA |                  | EXTINT[0]  |                                |         |                  |       |      |                    | SERCOM1/<br>PAD[0] |               | TC2/<br>WO[0] |     |            |

| 2/B2                                    | 2/B13                                   | 2/C1                                    | PA01 | VDDANA |                  | EXTINT[1]  |                                |         |                  |       |      |                    | SERCOM1/<br>PAD[1] |               | TC2/<br>WO[1] |     |            |

| 3/A3                                    | 3/C10                                   | 3/C3                                    | PA02 | VDDANA |                  | EXTINT[2]  |                                | AIN[0]  |                  | Y[0]  | VOUT |                    |                    |               |               |     |            |

| 4/B4                                    | 4/C8                                    | 4/D3                                    | PA03 | VDDANA |                  | EXTINT[3]  | ADC/<br>VREFA<br>DAC/<br>VREFA | AIN[1]  |                  | Y[1]  |      |                    |                    |               |               |     |            |

|                                         | /D11                                    | 5/D2                                    | PB04 | VDDANA |                  | EXTINT[4]  |                                | AIN[12] |                  | Y[10] |      |                    |                    |               |               |     |            |

|                                         |                                         | 6/D4                                    | PB05 | VDDANA |                  | EXTINT[5]  |                                | AIN[13] |                  | Y[11] |      |                    |                    |               |               |     |            |

|                                         |                                         | 9/E4                                    | PB06 | VDDANA |                  | EXTINT[6]  |                                | AIN[14] |                  | Y[12] |      |                    |                    |               |               |     |            |

|                                         |                                         | 10/E3                                   | PB07 | VDDANA |                  | EXTINT[7]  |                                | AIN[15] |                  | Y[13] |      |                    |                    |               |               |     |            |

|                                         | 7/D9                                    | 11/E2                                   | PB08 | VDDANA |                  | EXTINT[8]  |                                | AIN[2]  |                  | Y[14] |      |                    | SERCOM4/<br>PAD[0] |               | TC4/<br>WO[0] |     |            |

|                                         | 8/E10                                   | 12/F4                                   | PB09 | VDDANA |                  | EXTINT[9]  |                                | AIN[3]  |                  | Y[15] |      |                    | SERCOM4/<br>PAD[1] |               | TC4/<br>WO[1] |     |            |

| 5/A5                                    | 9/F13                                   | 13/F1                                   | PA04 | VDDANA |                  | EXTINT[4]  | ADC/<br>VREFB                  | AIN[4]  | AIN[0]           | Y[2]  |      |                    | SERCOMO/<br>PAD[0] |               | TC0/<br>WO[0] |     |            |

| 6/A7                                    | 10/F11                                  | 14/F2                                   | PA05 | VDDANA |                  | EXTINT[5]  |                                | AIN[5]  | AIN[1]           | Y[3]  |      |                    | SERCOMO/<br>PAD[1] |               | TC0/<br>WO[1] |     |            |

| 7/A9                                    | 11/E8                                   | 15/G2                                   | PA06 | VDDANA |                  | EXTINT[6]  |                                | AIN[6]  | AIN[2]           | Y[4]  |      |                    | SERCOM0/<br>PAD[2] |               | TC1/<br>WO[0] |     |            |

| 8/B6                                    | 12/G12                                  | 16/G1                                   | PA07 | VDDANA |                  | EXTINT[7]  |                                | AIN[7]  | AIN[3]           | Y[5]  |      |                    | SERCOMO/<br>PAD[3] |               | TC1/<br>WO[1] |     |            |

| 11/C7                                   | 13/F9                                   | 17/H1                                   | PA08 | VDDIO  | I²C              | NMI        |                                | AIN[16] |                  | X[0]  |      | SERCOMO/<br>PAD[0] | SERCOM2/<br>PAD[0] | TC0/<br>WO[0] |               |     |            |

| 12/C9                                   | 14/E6                                   | 18/H2                                   | PA09 | VDDIO  | I <sup>2</sup> C | EXTINT[9]  |                                | AIN[17] |                  | X[1]  |      | SERCOMO/<br>PAD[1] | SERCOM2/<br>PAD[1] | TC0/<br>WO[1] |               |     |            |

| 13/D8                                   | 15/G10                                  | 19/F3                                   | PA10 | VDDIO  |                  | EXTINT[10] |                                | AIN[18] |                  | X[2]  |      | SERCOMO/<br>PAD[2] | SERCOM2/<br>PAD[2] | TC1/<br>WO[0] |               |     | GCLK_IO[4] |

| 14/D6                                   | 16/F7                                   | 20/G3                                   | PA11 | VDDIO  |                  | EXTINT[11] |                                | AIN[19] |                  | X[3]  |      | SERCOMO/<br>PAD[3] | SERCOM2/<br>PAD[3] | TC1/<br>WO[1] |               |     | GCLK_IO[5] |

| continued                               | Pin/Ball |                                         | I/O  | Supply | Туре             | А          |     |     | B(2) |       |     | C <sub>(1)</sub>   | D <u>(1)</u>       | E             | F             | G   | Н          |

|-----------------------------------------|----------|-----------------------------------------|------|--------|------------------|------------|-----|-----|------|-------|-----|--------------------|--------------------|---------------|---------------|-----|------------|

| SAM D20E<br>(VQFN32,TQFP32/<br>WLCSP27) | SAM D20G | SAM D20J<br>(VQFN64,TQFP64/<br>UFBGA64) | Pin  | 11.5   | "                | EIC        | REF | ADC | AC   | PTC   | DAC |                    | SERCOM-<br>ALT     |               | C(4)          | СОМ | AC/GCLK    |

|                                         | 19       | 23/G4                                   | PB10 | VDDIO  |                  | EXTINT[10] |     |     |      |       |     |                    | SERCOM4/<br>PAD[2] |               | TC5/<br>WO[0] |     | GCLK_IO[4] |

|                                         | 20       | 24/E5                                   | PB11 | VDDIO  |                  | EXTINT[11] |     |     |      |       |     |                    | SERCOM4/<br>PAD[3] |               | TC5/<br>WO[1] |     | GCLK_IO[5] |

|                                         |          | 25/F5                                   | PB12 | VDDIO  | I <sup>2</sup> C | EXTINT[12] |     |     |      | X[12] |     | SERCOM4/<br>PAD[0] |                    | TC4/<br>WO[0] |               |     | GCLK_IO[6] |

|                                         |          | 26/G5                                   | PB13 | VDDIO  | I <sup>2</sup> C | EXTINT[13] |     |     |      | X[13] |     | SERCOM4/<br>PAD[1] |                    | TC4/<br>WO[1] |               |     | GCLK_IO[7] |

|                                         |          | 27/H5                                   | PB14 | VDDIO  |                  | EXTINT[14] |     |     |      | X[14] |     | SERCOM4/<br>PAD[2] |                    | TC5/<br>WO[0] |               |     | GCLK_IO[0] |

|                                         |          | 28/E6                                   | PB15 | VDDIO  |                  | EXTINT[15] |     |     |      | X[15] |     | SERCOM4/<br>PAD[3] |                    | TC5/<br>WO[1] |               |     | GCLK_IO[1] |

|                                         | 21/D7    | 29/F6                                   | PA12 | VDDIO  | I <sup>2</sup> C | EXTINT[12] |     |     |      |       |     | SERCOM2/<br>PAD[0] | SERCOM4/<br>PAD[0] | TC2/<br>WO[0] |               |     | AC/CMP[0]  |

|                                         | 22/F5    | 30/G6                                   | PA13 | VDDIO  | I <sup>2</sup> C | EXTINT[13] |     |     |      |       |     | SERCOM2/<br>PAD[1] | SERCOM4/<br>PAD[1] | TC2/<br>WO[1] |               |     | AC/CMP[1]  |

| 15/E9                                   | 23/G4    | 31/H6                                   | PA14 | VDDIO  |                  | EXTINT[14] |     |     |      |       |     | SERCOM2/<br>PAD[2] | SERCOM4/<br>PAD[2] | TC3/<br>WO[0] |               |     | GCLK_IO[0] |

| 16/E7                                   | 24/G2    | 32/H7                                   | PA15 | VDDIO  |                  | EXTINT[15] |     |     |      |       |     | SERCOM2/<br>PAD[3] | SERCOM4/<br>PAD[3] | TC3/<br>WO[1] |               |     | GCLK_IO[1] |

| 17/F8                                   | 25/D5    | 35/G7                                   | PA16 | VDDIO  | I²C              | EXTINT[0]  |     |     |      | X[4]  |     | SERCOM1/<br>PAD[0] | SERCOM3/<br>PAD[0] |               | TC2/<br>WO[0] |     | GCLK_IO[2] |

| 18/E5                                   | 26/F3    | 36/F8                                   | PA17 | VDDIO  | I <sup>2</sup> C | EXTINT[1]  |     |     |      | X[5]  |     | SERCOM1/<br>PAD[1] | SERCOM3/<br>PAD[1] |               | TC2/<br>WO[1] |     | GCLK_IO[3] |

| 19/F6                                   | 27/F1    | 37/F7                                   | PA18 | VDDIO  |                  | EXTINT[2]  |     |     |      | X[6]  |     | SERCOM1/<br>PAD[2] | SERCOM3/<br>PAD[2] |               | TC3/<br>WO[0] |     | AC/CMP[0]  |

| 20/F4                                   | 28/E4    | 38/E7                                   | PA19 | VDDIO  |                  | EXTINT[3]  |     |     |      | X[7]  |     | SERCOM1/<br>PAD[3] | SERCOM3/<br>PAD[3] |               | TC3/<br>WO[1] |     | AC/CMP[1]  |

|                                         |          | 39/D7                                   | PB16 | VDDIO  | I <sup>2</sup> C | EXTINT[0]  |     |     |      |       |     | SERCOM5/<br>PAD[0] |                    | TC6/<br>WO[0] |               |     | GCLK_IO[2] |

|                                         |          | 40/D5                                   | PB17 | VDDIO  | I <sup>2</sup> C | EXTINT[1]  |     |     |      |       |     | SERCOM5/<br>PAD[1] |                    | TC6/<br>WO[1] |               |     | GCLK_IO[3] |

|                                         | 29/E2    | 41/D6                                   | PA20 | VDDIO  |                  | EXTINT[4]  |     |     |      | X[8]  |     | SERCOM5/<br>PAD[2] | SERCOM3/<br>PAD[2] | TC7/<br>WO[0] |               |     | GCLK_IO[4] |

|                                         | 30/D1    | 42/C5                                   | PA21 | VDDIO  |                  | EXTINT[5]  |     |     |      | X[9]  |     | SERCOM5/<br>PAD[3] | SERCOM3/<br>PAD[3] | TC7/<br>WO[1] |               |     | GCLK_IO[5] |

| 21/E3                                   | 31/C6    | 43/C6                                   | PA22 | VDDIO  | I <sup>2</sup> C | EXTINT[6]  |     |     |      | X[10] |     | SERCOM3/<br>PAD[0] | SERCOM5/<br>PAD[0] |               | TC4/<br>WO[0] |     | GCLK_IO[6] |

| 22                                      | 32/D3    | 44/C7                                   | PA23 | VDDIO  | I <sup>2</sup> C | EXTINT[7]  |     |     |      | X[11] |     | SERCOM3/<br>PAD[1] | SERCOM5/<br>PAD[1] |               | TC4/<br>WO[1] |     | GCLK_IO[7] |

| 23                                      | 33/C2    | 45/E8                                   | PA24 | VDDIO  |                  | EXTINT[12] |     |     |      |       |     | SERCOM3/<br>PAD[2] | SERCOM5/<br>PAD[2] |               | TC5/<br>WO[0] |     |            |

| 24                                      | 34/B1    | 46/D8                                   | PA25 | VDDIO  |                  | EXTINT[13] |     |     |      |       |     | SERCOM3/<br>PAD[3] | SERCOM5/<br>PAD[3] |               | TC5/<br>WO[1] |     |            |

|                                         | 37       | 49/A8                                   | PB22 | VDDIO  |                  | EXTINT[6]  |     |     |      |       |     |                    | SERCOM5/<br>PAD[2] |               | TC7/<br>WO[0] |     | GCLK_IO[0] |

|                                         | 38       | 50/A7                                   | PB23 | VDDIO  |                  | EXTINT[7]  |     |     |      |       |     |                    | SERCOM5/<br>PAD[3] |               | TC7/<br>WO[1] |     | GCLK_IO[1] |

| 25                                      | 39/A2    | 51/B7                                   | PA27 | VDDIO  |                  | EXTINT[15] |     |     |      |       |     |                    |                    |               |               |     | GCLK_IO[0] |

| 27/E1                                   | 41/A4    | 53/A6                                   | PA28 | VDDIO  |                  | EXTINT[8]  |     |     |      |       |     |                    |                    |               |               |     | GCLK_IO[0] |

| continued                               |                                         |                                         |      |            |                  |            |     |         |              |      |     |           |                    |   |                    |           |            |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|------|------------|------------------|------------|-----|---------|--------------|------|-----|-----------|--------------------|---|--------------------|-----------|------------|

|                                         | Pin/Ball                                |                                         | I/O  | I/O Supply |                  | A          |     |         | B <u>(2)</u> |      |     | C(1)      | D(1)               | Е | F                  | G         | н          |

| SAM D20E<br>(VQFN32,TQFP32/<br>WLCSP27) | SAM D20G<br>(VQFN48,TQFP48/<br>WLCSP45) | SAM D20J<br>(VQFN64,TQFP64/<br>UFBGA64) | Pin  |            |                  | EIC        | REF | ADC     | AC           | PTC  | DAC | SERCOM(3) | SERCOM-<br>ALT     | Т | C <sub>-</sub> (4) | СОМ       | AC/GCLK    |

| 31/C3                                   | 45/B7                                   | 57/B5                                   | PA30 | VDDIO      |                  | EXTINT[10] |     |         |              |      |     |           | SERCOM1/<br>PAD[2] |   | TC1/<br>WO[0]      | SWCLK     | GCLK_IO[0] |

| 32/D4                                   | 46/B9                                   | 58/B4                                   | PA31 | VDDIO      |                  | EXTINT[11] |     |         |              |      |     |           | SERCOM1/<br>PAD[3] |   | TC1/<br>WO[1]      | SWDIO (5) |            |

|                                         |                                         | 59/C4                                   | PB30 | VDDIO      | I <sup>2</sup> C | EXTINT[14] |     |         |              |      |     |           | SERCOM5/<br>PAD[0] |   | TC0/<br>WO[0]      |           |            |

|                                         |                                         | 60/B3                                   | PB31 | VDDIO      | I <sup>2</sup> C | EXTINT[15] |     |         |              |      |     |           | SERCOM5/<br>PAD[1] |   | TC0/<br>WO[1]      |           |            |

|                                         |                                         | 61/B2                                   | PB00 | VDDANA     |                  | EXTINT[0]  |     | AIN[8]  |              | Y[6] |     |           | SERCOM5/<br>PAD[2] |   | TC7/<br>WO[0]      |           |            |

|                                         |                                         | 62/A2                                   | PB01 | VDDANA     |                  | EXTINT[1]  |     | AIN[9]  |              | Y[7] |     |           | SERCOM5/<br>PAD[3] |   | TC7/<br>WO[1]      |           |            |

|                                         | 47/A12                                  | 63/A1                                   | PB02 | VDDANA     |                  | EXTINT[2]  |     | AIN[10] |              | Y[8] |     |           | SERCOM5/<br>PAD[0] |   | TC6/<br>WO[0]      |           |            |

|                                         | 48/B11                                  | 64/C2                                   | PB03 | VDDANA     |                  | EXTINT[3]  |     | AIN[11] |              | Y[9] |     |           | SERCOM5/<br>PAD[1] |   | TC6/<br>WO[1]      |           |            |

#### Notes:

- 1. SERCOM4/SERCOM5 are not available on VQFN32/TQFP32 and WLCSP27 packages.

- 2. All analog pin functions are on peripheral function B. Peripheral function B must be selected to disable the digital control of the pin.

- 3. Only some pins can be used in SERCOM I<sup>2</sup>C mode. Refer to the Type column for using a SERCOM pin in I<sup>2</sup>C mode. Refer to "Electrical Characteristics" for details on the I<sup>2</sup>C pin characteristics.

- 4. TC6 and TC7 are not supported on the SAM D20E and SAM D20G devices. Refer to the 1. Configuration Summary for details.

- 5. The SWDIO function is only activated in the presence of a debugger.

#### **Related Links**

- 21. PORT I/O Pin Controller

- 32. Electrical Characteristics at 85°C

- 32.8.2. I2C Pins

#### 6.2 Other Functions

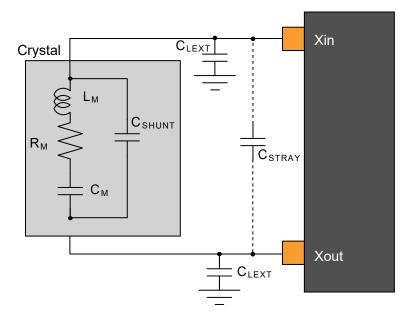

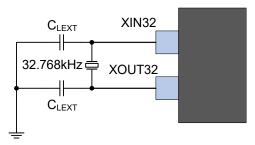

#### 6.2.1 Oscillator Pinout

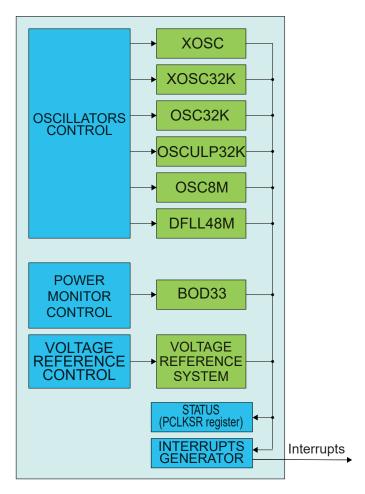

The oscillators are not mapped to the normal PORT functions and their multiplexing are controlled by registers in the System Controller (SYSCTRL).

Table 6-2. Oscillator Pinout

| Oscillator     | Supply | Signal | I/O pin |

|----------------|--------|--------|---------|

| XOSC           | VDDIO  | XIN    | PA14    |

|                |        | XOUT   | PA15    |

| XOSC32K VDDANA |        | XIN32  | PA00    |

|                |        | XOUT32 | PA01    |

#### **Related Links**

16. SYSCTRL - System Controller

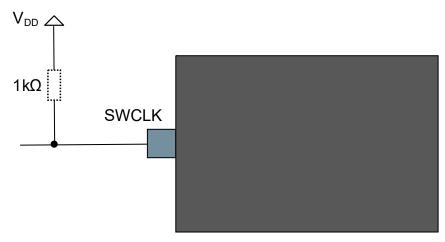

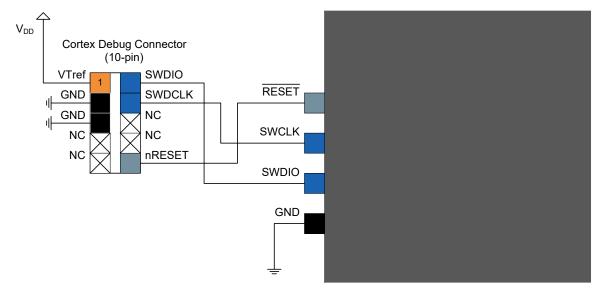

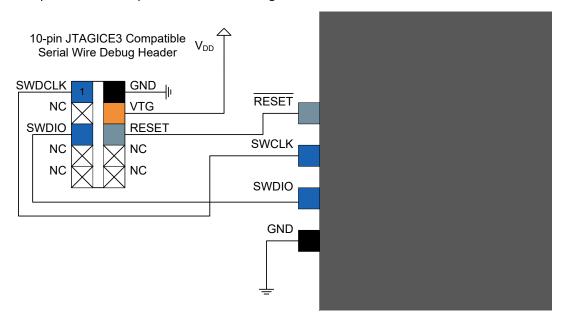

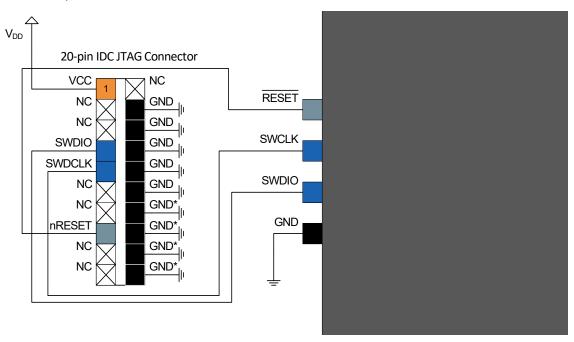

# 6.2.2 Serial Wire Debug Interface Pinout

Only the SWCLK pin is mapped to the normal PORT functions. A debugger cold-plugging or hotplugging detection will automatically switch the SWDIO port to the SWDIO function.

**Table 6-3.** Serial Wire Debug Interface Pinout

| Signal | Supply | I/O pin |

|--------|--------|---------|

| SWCLK  | VDDIO  | PA30    |

| SWDIO  | VDDIO  | PA31    |

#### **Related Links**

12. DSU - Device Service Unit

# 7. Power Supply and Start-Up Considerations Related Links

32.4. Supply Characteristics

#### 7.1 Power Domain Overview

# 7.2 Power Supply Considerations

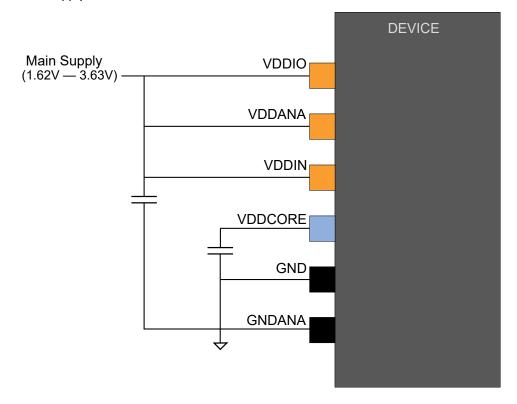

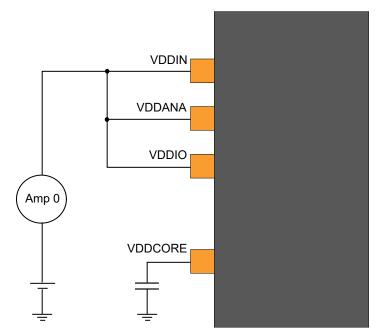

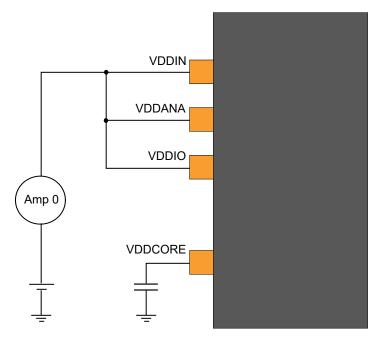

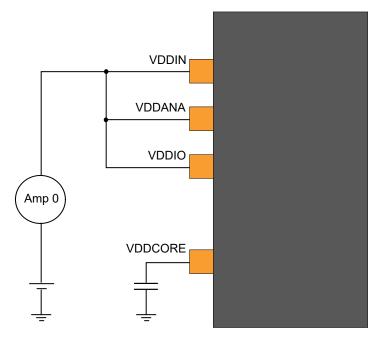

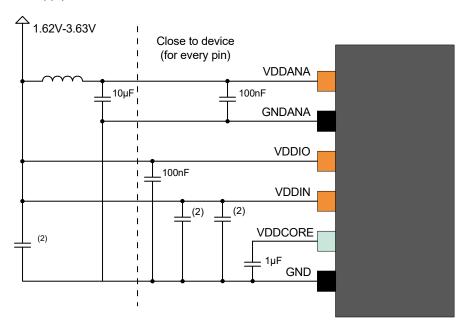

#### **7.2.1** Power Supplies

The device has the following power supply pins:

- VDDIO: Powers I/O lines, OSC8M and XOSC. Voltage is 1.62V to 3.63V.

- VDDIN: Powers I/O lines and the internal regulator. Voltage is 1.62V to 3.63V.

- VDDANA: Powers I/O lines and the ADC, AC, DAC, PTC, OSCULP32K, OSC32K, XOSC32K. Voltage is 1.62V to 3.63V.

- VDDCORE: Internal regulated voltage output. Powers the core, memories, peripherals, and DFLL48M. Voltage is 1.2V.

The same voltage must be applied to both VDDIN, VDDIO and VDDANA. This common voltage is referred to as  $V_{DD}$  in the data sheet.

The ground pins, GND, are common to VDDCORE, VDDIO and VDDIN. The ground pin for VDDANA is GNDANA.

For decoupling recommendations for the different power supplies. Refer to *Schematic Checklist* for details.

#### **Related Links**

36. Schematic Checklist

#### 7.2.2 Voltage Regulator

The voltage regulator has two different modes:

- Normal mode: To be used when the CPU and peripherals are running

- Low-Power (LP) mode: To be used when the regulator draws small static current. It can be used in Standby mode

# 7.2.3 Typical Powering Schematics

The device uses a single main supply with a range of 1.62V - 3.63V.

The following figure shows the recommended power supply connection.

Figure 7-1. Power Supply Connection

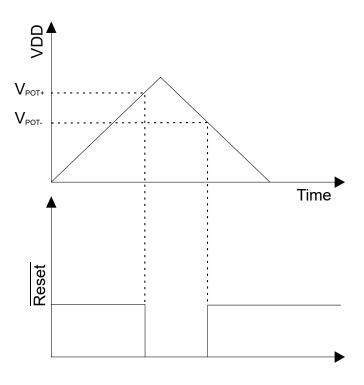

#### 7.2.4 Power-Up Sequence

#### 7.2.4.1 Minimum Rise Rate

The integrated Power-on Reset (POR) circuitry monitoring the VDDANA power supply requires a minimum rise rate. Refer to the *Electrical Characteristics* for details.

#### **Related Links**

32. Electrical Characteristics at 85°C

#### 7.2.4.2 Maximum Rise Rate

The rise rate of the power supply must not exceed the values described in Electrical Characteristics. Refer to the *Electrical Characteristics* for details.

#### **Related Links**

32. Electrical Characteristics at 85°C

# 7.3 Power-Up

This section summarizes the power-up sequence of the device. The behavior after power-up is controlled by the Power Manager. Refer to *PM – Power Manager* for details.

#### **Related Links**

15. Power Manager (PM)

#### **7.3.1** Starting of Clocks

After power-up, the device is set to its initial state and kept in reset, until the power has stabilized throughout the device. Once the power has stabilized, the device will use a 1MHz clock. This clock is derived from the 8MHz Internal Oscillator (OSC8M), which is divided by eight and used as a clock source for generic clock generator 0. Generic clock generator 0 is the main clock for the Power Manager (PM).

Some synchronous system clocks are active, allowing software execution.

Refer to the "Clock Mask Register" section in *PM – Power Manager* for the list of default peripheral clocks running. Synchronous system clocks that are running are by default not divided and receive a 1MHz clock through generic clock generator 0. Other generic clocks are disabled except GCLK\_WDT, which is used by the Watchdog Timer (WDT).

#### **Related Links**

15. Power Manager (PM)

#### 7.3.2 I/O Pins

After power-up, the I/O pins are tri-stated.

#### 7.3.3 Fetching of Initial Instructions

After reset has been released, the CPU starts fetching PC and SP values from the reset address, which is 0x00000000. This address points to the first executable address in the internal Flash. The code read from the Internal Flash is free to configure the clock system and clock sources. Refer to PM – Power Manager, GCLK – Generic Clock Controller and SYSCTRL – System Controller for details. Refer to the ARM Architecture Reference Manual for more information on CPU startup (http://www.arm.com).

#### **Related Links**

- 15. Power Manager (PM)

- 16. SYSCTRL System Controller

- 14. GCLK Generic Clock Controller

- 15. Power Manager (PM)

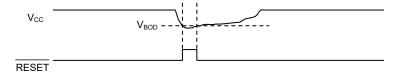

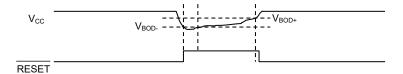

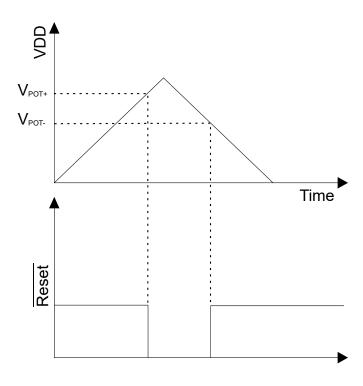

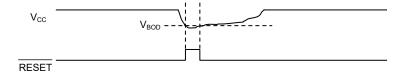

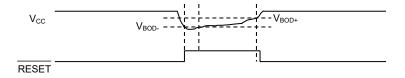

#### 7.4 Power-On Reset and Brown-Out Detector

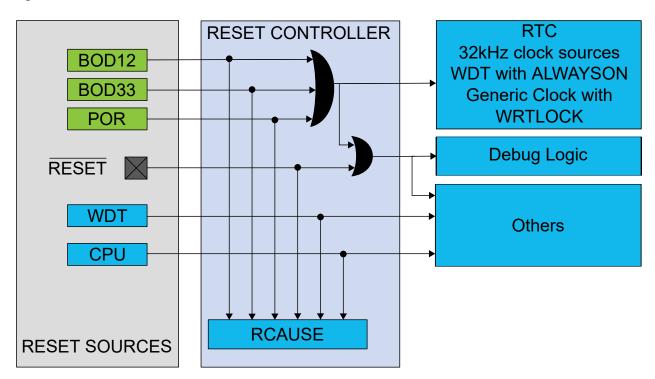

The SAM D20 embeds three features to monitor, warn and/or reset the device:

- POR: Power-On Reset on VDDANA

- BOD33: Brown-Out Detector on VDDANA

- BOD12: Voltage Regulator Internal Brown-Out Detector on VDDCORE. The Voltage Regulator Internal BOD is calibrated in production and its calibration configuration is stored in the NVM User Row. This configuration should not be changed if the user row is written to assure the correct behavior of the BOD12.

#### 7.4.1 Power-On Reset on VDDANA

POR monitors VDDANA. It is always activated and monitors voltage at startup and also during all the sleep modes. If VDDANA goes below the threshold voltage, the entire chip is reset.

#### 7.4.2 Brown-Out Detector on VDDANA

BOD33 monitors VDDANA. Refer to SYSCTRL - System Controller for details.

#### **Related Links**

16. SYSCTRL - System Controller

#### 7.4.3 Brown-Out Detector on VDDCORE

Once the device has started up, BOD12 monitors the internal VDDCORE.

# 8. Product Mapping

Figure 8-1. Product Mapping

This figure represents the full configuration of the SAM D20 device with maximum flash and SRAM capabilities and a full set of peripherals. Refer to the Configuration Summary for details.

## 9. Memories

#### 9.1 Embedded Memories

- Internal high-speed Flash

- Internal high-speed RAM, single-cycle access at full speed

- Dedicated Flash area for EEPROM Emulation

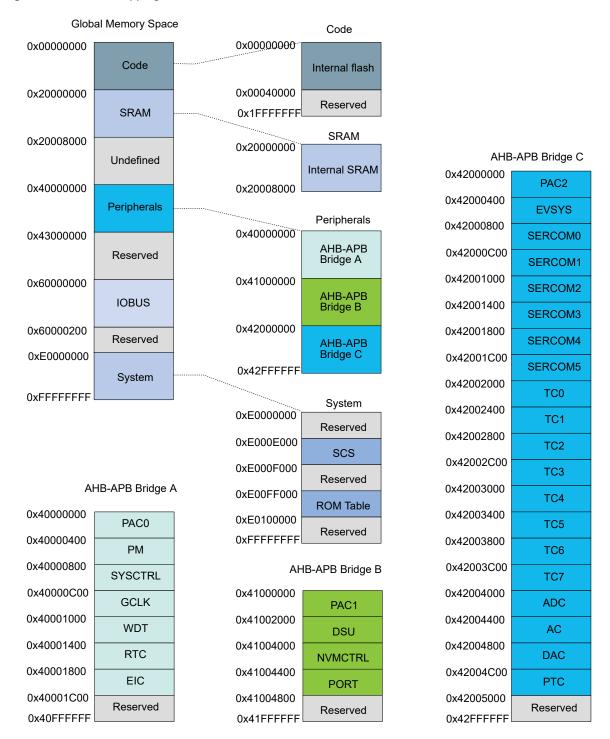

# 9.2 Physical Memory Map

The high-speed bus is implemented as a Bus Matrix. All high-speed bus addresses are fixed, and they are never remapped in any way, even during boot. The 32-bit physical address space is mapped as given in the below table.

Table 9-1. Physical Memory Map

| Memory              | Start Address |           | Size (Kbytes) |           |           |           |  |  |

|---------------------|---------------|-----------|---------------|-----------|-----------|-----------|--|--|

|                     |               | SAMD20x18 | SAMD20x17     | SAMD20x16 | SAMD20x15 | SAMD20x14 |  |  |

| Internal Flash      | 0x00000000    | 256       | 128           | 64        | 32        | 16        |  |  |

| Internal SRAM       | 0x20000000    | 32        | 16            | 8         | 4         | 2         |  |  |

| Peripheral Bridge A | 0x40000000    | 64        | 64            | 64        | 64        | 64        |  |  |

| Peripheral Bridge B | 0x41000000    | 64        | 64            | 64        | 64        | 64        |  |  |

| Peripheral Bridge C | 0x42000000    | 64        | 64            | 64        | 64        | 64        |  |  |

**Note:** x = G, J or E. Refer to Ordering Information.

Table 9-2. Flash Memory Parameters

| Device    | Flash Size | Number of Pages | Page Size | Row Size            |

|-----------|------------|-----------------|-----------|---------------------|

| SAMD20x18 | 256 Kbytes | 4096            | 64 bytes  | 4 pages = 256 bytes |

| SAMD20x17 | 128 Kbytes | 2048            | 64 bytes  | 4 pages = 256 bytes |

| SAMD20x16 | 64 Kbytes  | 1024            | 64 bytes  | 4 pages = 256 bytes |

| SAMD20x15 | 32 Kbytes  | 512             | 64 bytes  | 4 pages = 256 bytes |

| SAMD20x14 | 16 Kbytes  | 256             | 64 bytes  | 4 pages = 256 bytes |

#### Notes:

- 1. x = G, J or E. Refer to Ordering Information.

- 2. The number of pages (NVMP) and page size (PSZ) can be read from the NVM Pages and Page Size bits in the NVM Parameter register in the NVMCTRL (PARAM.NVMP and PARAM.PSZ, respectively). Refer to NVM Parameter (PARAM) register for details.

#### **Related Links**

10.3. High-Speed Bus System

2. Ordering Information (1)

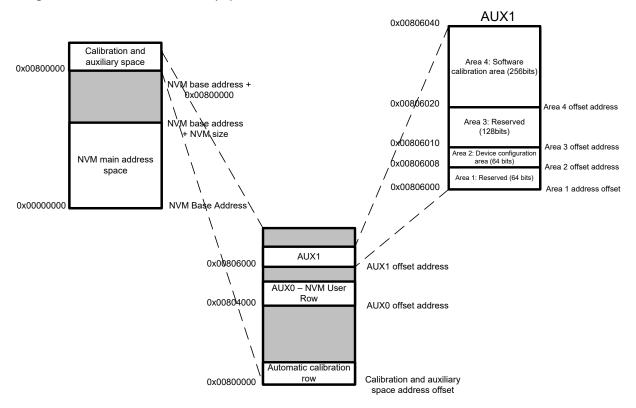

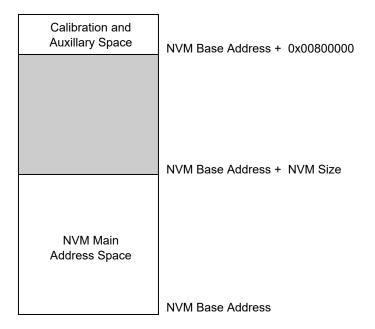

# 9.3 NVM Calibration and Auxiliary Space

The device calibration data are stored in different sections of the NVM calibration and auxiliary space presented in the following figure.

Figure 9-1. Calibration and Auxiliary Space

The values from the automatic calibration row are loaded into their respective registers at startup.

#### 9.4 **NVM User Row Mapping**

The first two 32-bit words of the NVM User Row contain calibration data that are automatically read at device power-on.

The NVM User Row can be read at address 0x804000.

To write the NVM User Row, refer to NVMCTRL - Non-Volatile Memory Controller.

When writing to the user row, the values do not get loaded by other modules on the device until a device Reset occurs.

Table 9-3. NVM User Row Mapping

| Bit Position     | Name     | Usage                                                                                                                                                                                                                                                                                                               |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

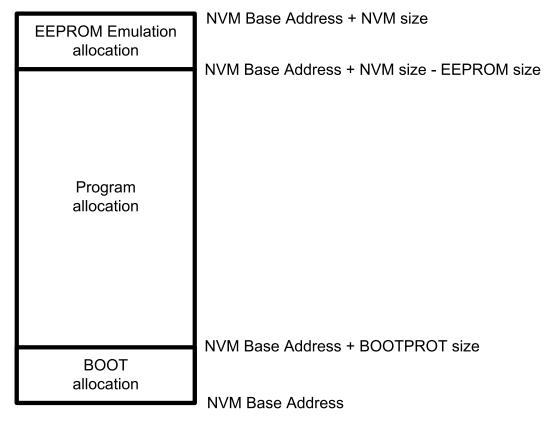

| 2:0              | BOOTPROT | Used to select one of eight different bootloader sizes. Refer to the "NVMCTRL – Non-Volatile Memory Controller". Default value = 0x7 except for WLCSP45 that has default value = 0x3.  Note: WLCSP27 devices boot ROM is not protected as the bootloader is self-upgradable through the I <sup>2</sup> C interface. |

| 3(1)             | Reserved | Do not modify the value of a reserved bit. Reading a reserved bit has no significance to the user application.                                                                                                                                                                                                      |

| 6:4              | EEPROM   | Used to select one of eight different EEPROM Emulation sizes. Refer to NVMCTRL – Non-Volatile Memory Controller. Default value = 7.                                                                                                                                                                                 |

| 7 <sup>(1)</sup> | Reserved | Do not modify the value of a reserved bit. Reading a reserved bit has no significance to the user application.                                                                                                                                                                                                      |

| contii               | nued             |                                                                                                                                                                                                   |

|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Bit Position</b>  | Name             | Usage                                                                                                                                                                                             |

| 13:8                 | BOD33 Level      | BOD33 Threshold Level at power on. Refer to SYSCTRL BOD33 register. Default value = 7 on all package grades except Extended Temperature with compliance to AEC-Q100 which has Default value = 34. |

| 14                   | BOD33 Enable     | BOD33 Enable at power on . Refer to SYSCTRL BOD33 register. Default value = 1.                                                                                                                    |

| 16:15                | BOD33 Action     | BOD33 Action at power on. Refer to SYSCTRL BOD33 register. Default value = 1.                                                                                                                     |

| 24:17 <sup>(1)</sup> | Reserved         | Do not modify the value of a reserved bit. Reading a reserved bit has no significance to the user application.                                                                                    |

| 25                   | WDT Enable       | WDT Enable at power on. Refer to WDT CTRL register. Default value = 0.                                                                                                                            |

| 26                   | WDT Always-On    | WDT Always-On at power on. Refer to WDT CTRL register. Default value = 0.                                                                                                                         |

| 30:27                | WDT Period       | WDT Period at power on. Refer to <i>WDT CONFIG register</i> . Default value = 0x0B.                                                                                                               |

| 34:31                | WDT Window       | WDT Window mode time-out at power on. Refer to <i>WDT CONFIG register</i> . Default value = 0x0B.                                                                                                 |

| 38:35                | WDT EWOFFSET     | WDT Early Warning Interrupt Time Offset at power on. Refer to WDT EWCTRL register. Default value = 0xB.                                                                                           |

| 39                   | WDT WEN          | WDT Timer Window Mode Enable at power on. Refer to <i>WDT CTRL register</i> . Default value = 0.                                                                                                  |

| 40                   | BOD33 Hysteresis | BOD33 Hysteresis configuration at power on. Refer to SYSCTRL BOD33 register. Default value = 1.                                                                                                   |

| 47:41                | Reserved         | Do not modify the value of a reserved bit. Reading a reserved bit has no significance to the user application.                                                                                    |

| 63:48                | LOCK             | NVM Region Lock Bits. Refer to <i>NVMCTRL – Non-Volatile Memory Controller</i> . Default value = 0xFFFF.                                                                                          |

#### Note:

1. It is required to preserve the value of a reserved bit while modifying the NVM User Row bits.

#### **Related Links**

20. NVMCTRL - Nonvolatile Memory Controller

16.8.14. BOD33

17.8.1. CTRL

17.8.2. CONFIG

17.8.3. EWCTRL

32.10.3.1. BOD33

# 9.5 NVM Software Calibration Area Mapping

The NVM Software Calibration Area contains calibration data that are measured and written during production test. These calibration values should be read by the application software and written back to the corresponding register.

The NVM Software Calibration Area can be read at address 0x806020.

The NVM Software Calibration Area can not be written.

Table 9-4.

NVM Software Calibration Area Mapping

| Bit Position | Name          | Description                                                         |

|--------------|---------------|---------------------------------------------------------------------|

| 26:0         | Reserved      |                                                                     |

| 34:27        | ADC LINEARITY | ADC Linearity Calibration. Should be written to ADC CALIB register. |

| 37:35        | ADC BIASCAL   | ADC Bias Calibration. Should be written to ADC CALIB register.      |

| 44:38        | OSC32K CAL    | OSC32KCalibration. Should be written to SYSCTRL OSC32K register.    |

| cont         | continued                        |                                                                                  |  |  |  |  |  |

|--------------|----------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Position | Name                             | Description                                                                      |  |  |  |  |  |

| 57:45        | Reserved                         |                                                                                  |  |  |  |  |  |

| 63:58        | DFLL48M COARSE CAL <sup>1)</sup> | DFLL48M Coarse calibration value, should be written to SYSCTRL DFLLVAL register. |  |  |  |  |  |

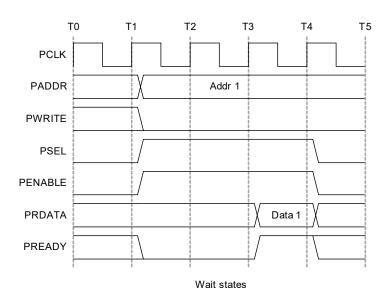

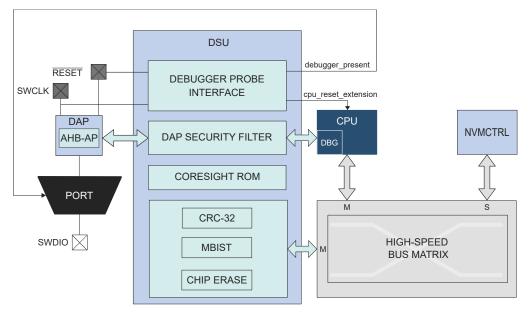

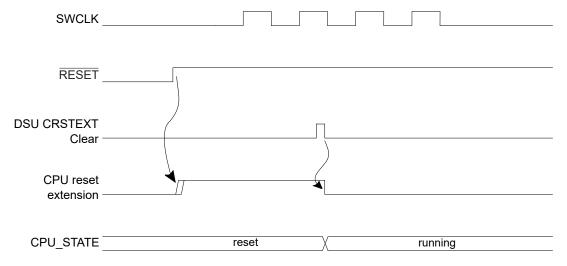

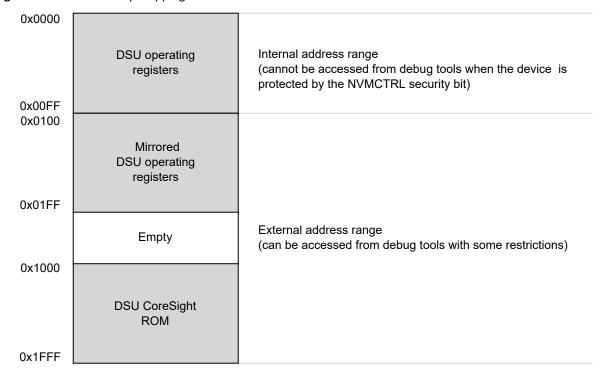

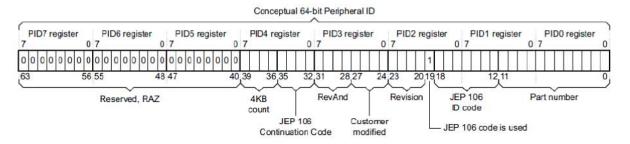

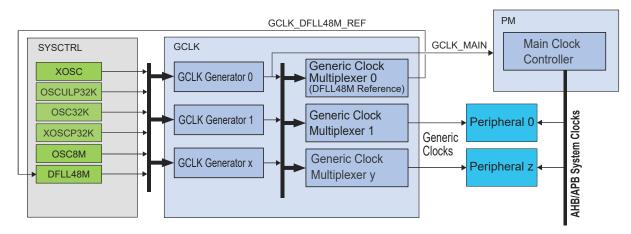

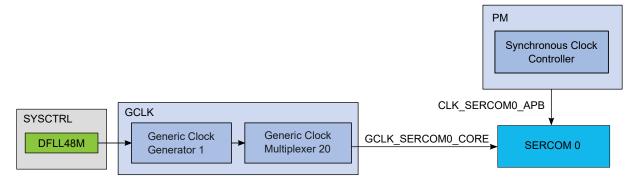

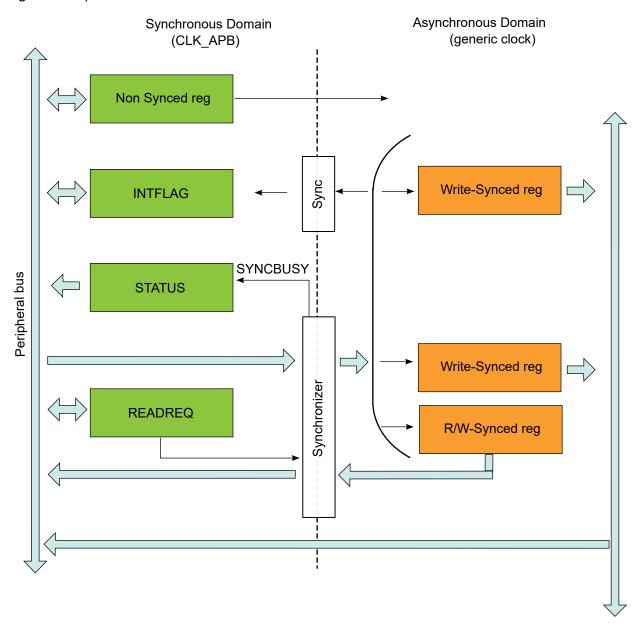

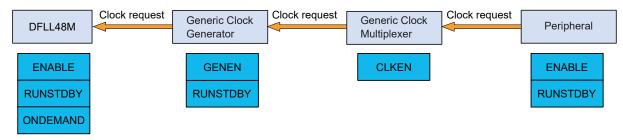

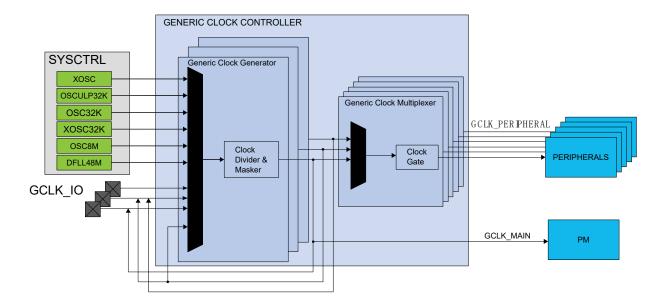

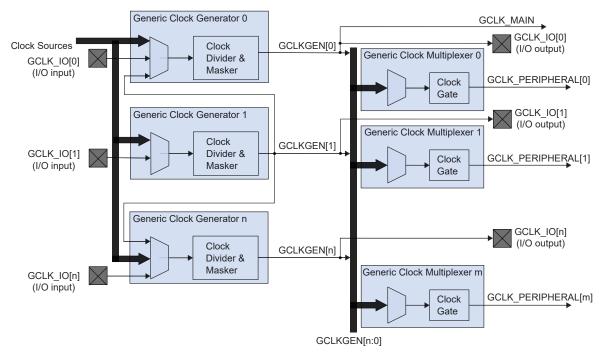

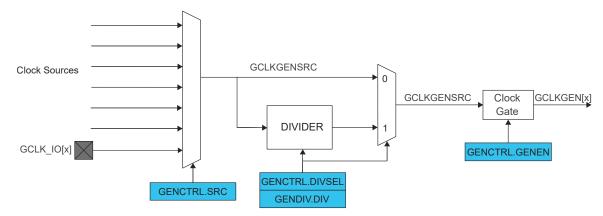

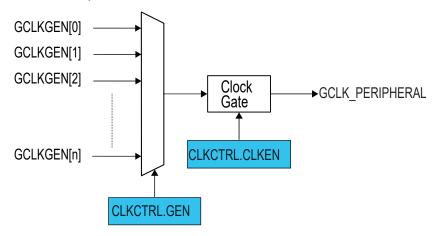

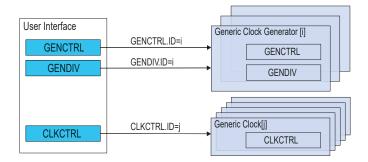

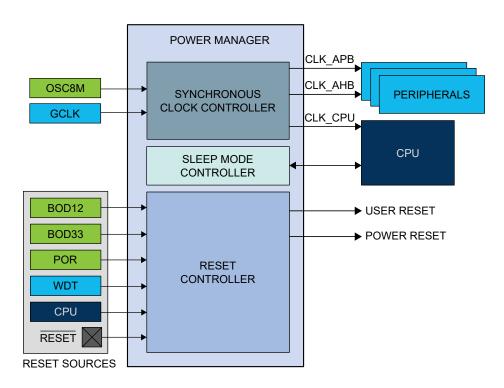

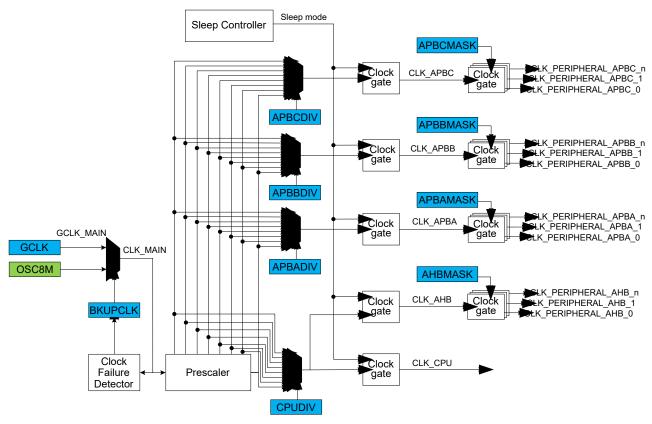

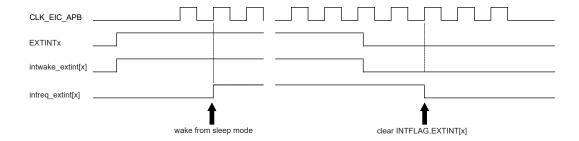

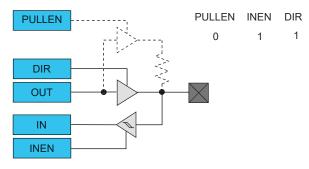

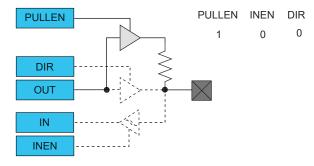

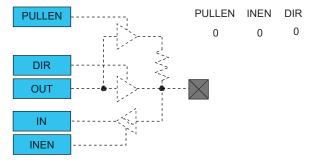

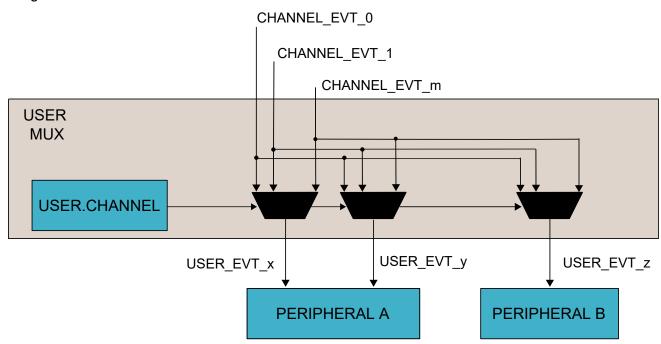

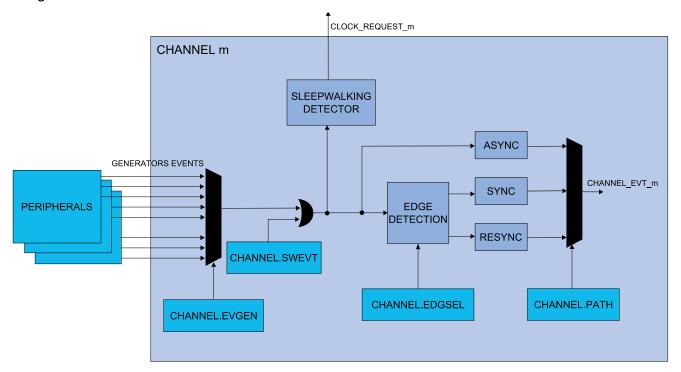

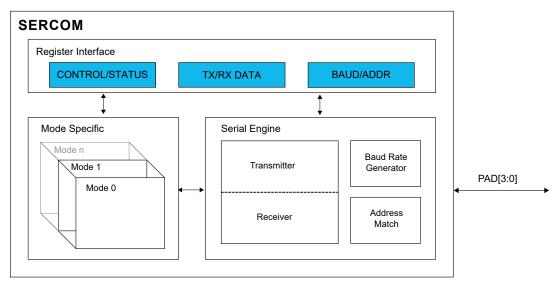

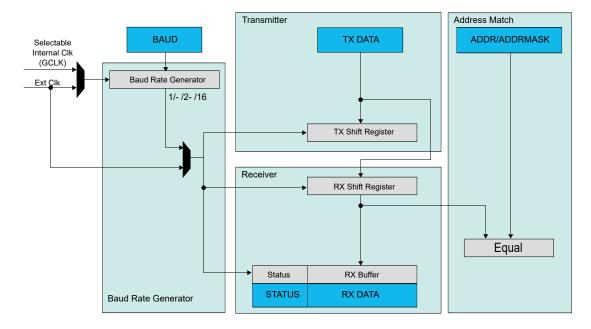

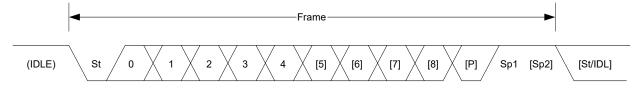

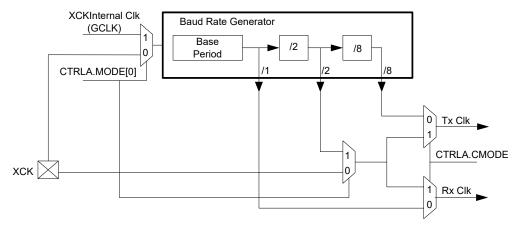

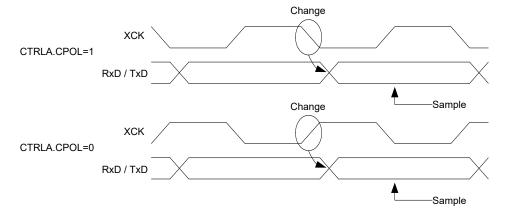

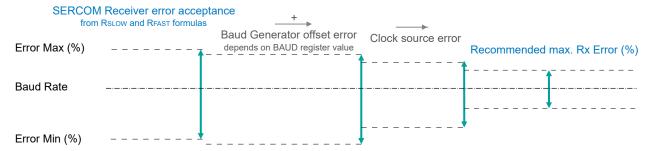

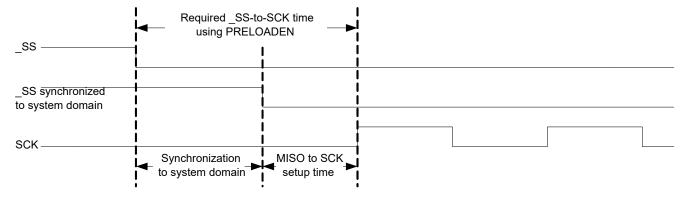

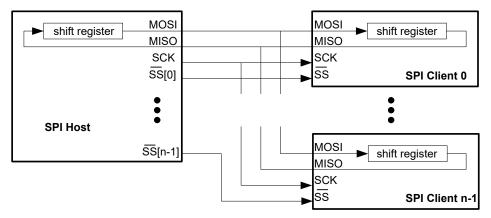

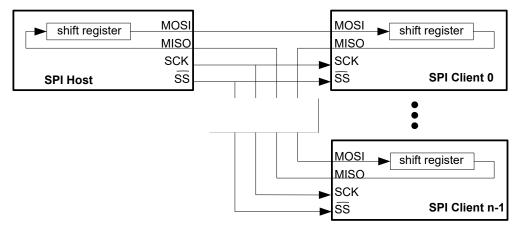

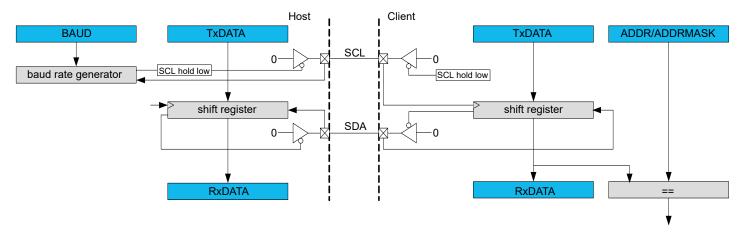

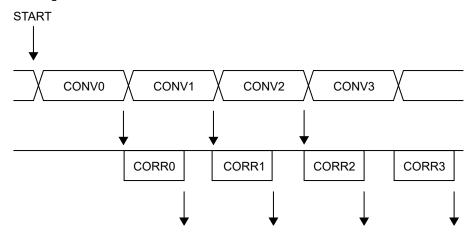

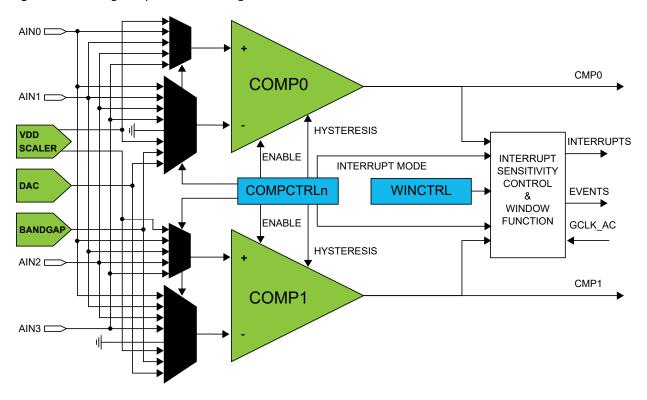

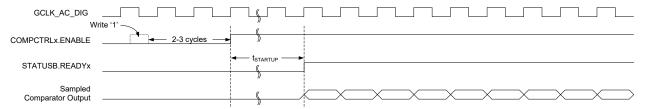

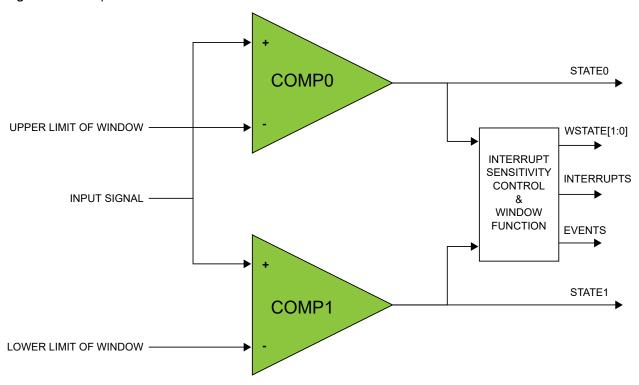

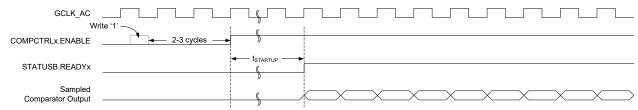

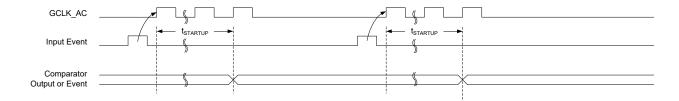

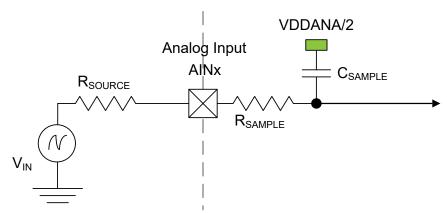

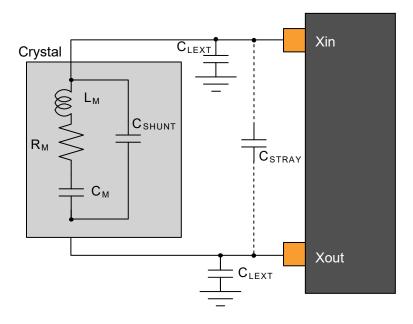

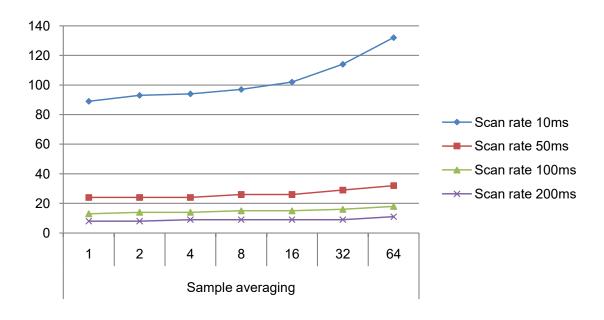

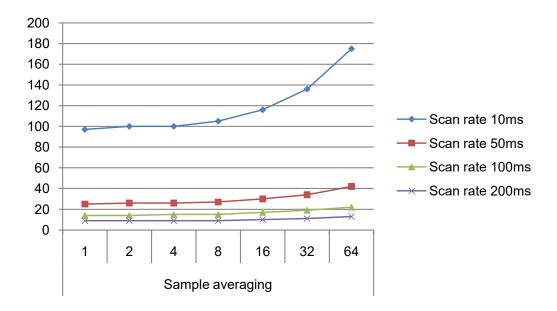

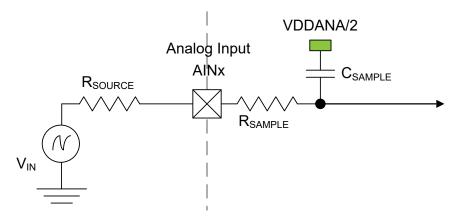

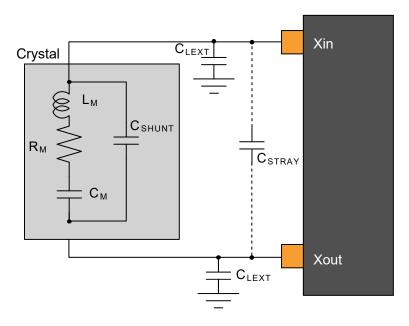

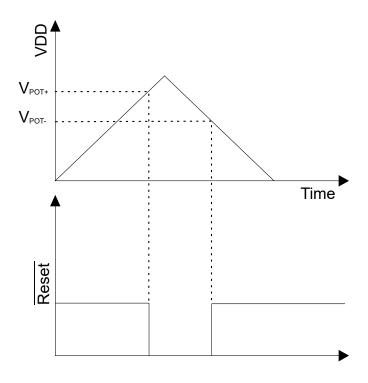

| 73:64        | DFLL48M fine CAL <sup>(1)</sup>  | DFLL48M Fine calibration value, should be written to SYSCTRL.DFLLVAL register.   |  |  |  |  |  |