#### Datasheet

## **Features & Benefits**

- Two independent simultaneously operating active light measurement channels

- Integrated DC light cancellation circuitry for active light channel DC light suppression

- Two logarithmic ambient light channels

- High input capacitance tolerant input current terminals

- Extremely high degree of adaptability for different optical systems

- Stand-by and sleep modes

- Integrated 16bit ADC

- Integrated temperature sensor

- Digital communication interface via SPI

- Integrated watchdog timer

- High safety design by comprehensive diagnostic and monitoring functions

- Minimum amount of external components

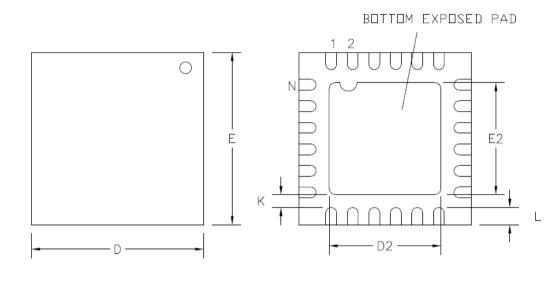

- Small-size SMD package QFN24 4x4 mm

## **Ordering Information**

| Product Code | Temperature Code | Package Code | <b>Option Code</b> | Packing Form Code |

|--------------|------------------|--------------|--------------------|-------------------|

| MLX75030     | R                | LW           | BAA-000            | RE or TU          |

| MLX75030     | С                | LW           | BAA-000            | RE or TU          |

#### Legend:

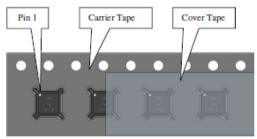

Temperature Code: Package Code: Option Code: Packing Form: Ordering example: R = -40 to 105°C, C = 0°C to 70°C LW = = Quad Flat Package (QFN) with wettable flanks BAA-000 = Design Revision RE = Reel, TU = Tube MLX75030RLW-BAA-000-RE

# **Application Examples**

- Optical proximity sensing & display dimming

- Touch-less gesture recognition

- Driver/passenger discrimination

- Touch Screen Wake-up on Proximity

## **Pin Description**

# **1. General Description**

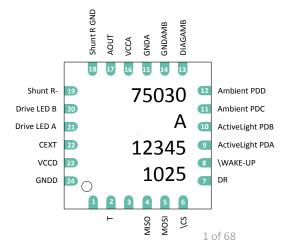

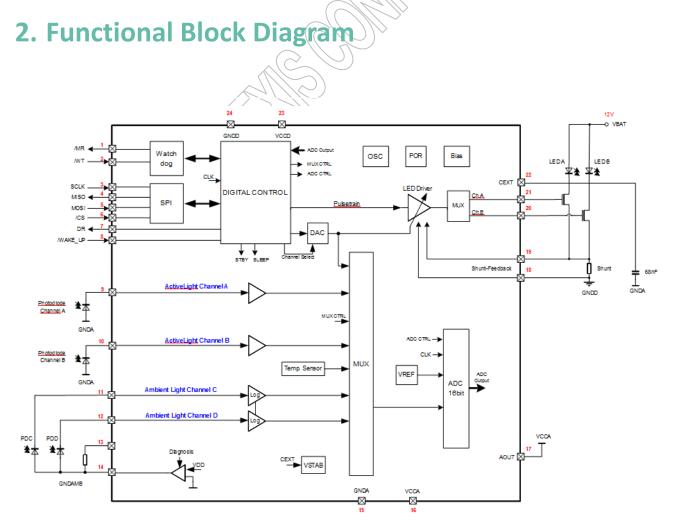

The MLX75030 Universal ActiveLight Sensor Interface has been designed to allow easy and robust dual-channel optical reflection and dual channel ambient light measurement. Therefore it is ideally suited for the design of responsive human-machine interfaces (HMI) that require proximity or gesture detection in environments subject to wide background light level variations, possibly in combination with display dimming.

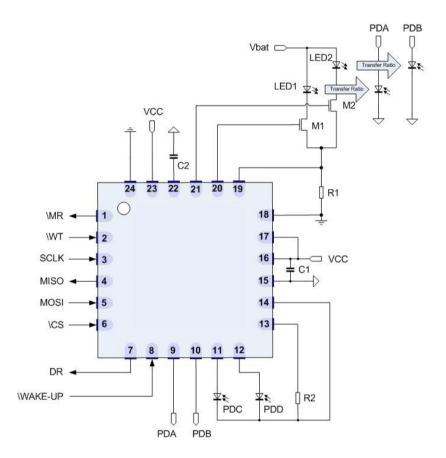

The MLX75030 IC consists of two optical sensor interface parts. Part one is optimized for active light measurements and is designed to control up to 2 external LEDs and to sense modulated light current from up to 2 external photodiodes on independent channels A and B. The ActiveLight detection is virtually independent from background light by means of integrated hardware-level ambient light suppression. Part two consists of two logarithmic current sensors C and D, which measure the photocurrent of externally connected photodiodes. Simple and programmable operation is ensured by internal control logic, configurable user registers and SPI communication.

Figure 1 : MLX75030 Functional Block Diagram

REVISION 008 - AUG 2018 3901075030

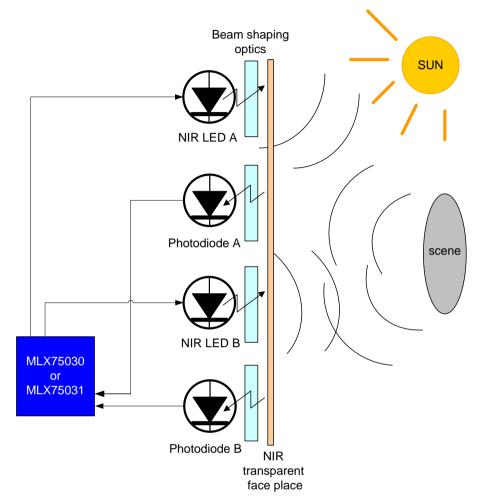

# **3. Application Diagram**

Figure 2 : Application diagram of a dual channel active reflection detector with 2 photodiodes and 2 LEDs. The measured signal is virtually independent of background light from the sun or other sources.

# **Table of Contents**

| 1. | General Description                                       | . 2 |

|----|-----------------------------------------------------------|-----|

| 2. | Functional Block Diagram                                  | . 2 |

|    | Application Diagram                                       |     |

|    | ble of Contents                                           |     |

|    | Glossary of Terms                                         |     |

|    | Absolute Maximum Ratings                                  |     |

|    | Pin Definitions & Descriptions                            |     |

|    | General Electrical Specifications                         |     |

|    | Detailed Description                                      |     |

| ۶. | 9.1. Analog Sensor Functions                              |     |

|    | 9.1.1. Active Light Sensor                                |     |

|    | 9.1.1.1. Active Light Channel DC Light Measurement        |     |

|    | 9.1.2. ActiveLight Channel DC Light compensation          |     |

|    | 9.1.3. Ambient Light Sensor                               |     |

|    | 9.1.3.1. Normal Operation                                 |     |

|    | 9.1.3.2. Calibration and temperature compensation         | 20  |

|    | 9.1.3.3. Diagnostics Mode Operation                       | 21  |

|    | 9.1.4. Temperature Sensor                                 | 21  |

|    | 9.1.5. DAC                                                | 22  |

|    | 9.1.6. LED Driver                                         | 23  |

|    | 9.1.7. POR                                                |     |

|    | 9.2. SPI                                                  |     |

|    | 9.2.1. General Description of SPI Interface               |     |

|    | 9.2.2. Detailed Explanation of SPI Instruction Words      |     |

|    | 9.2.2.1. NOP – Idle Command                               |     |

|    | 9.2.2.2. CR – Chip Reset Command                          |     |

|    | 9.2.2.3. RSLP/CSLP – Request Sleep/Confirm Sleep          |     |

|    | 9.2.2.4. RSTBY/CSTBY - Request Standby/Confirm Standby    |     |

|    | 9.2.2.5. NRM – Normal Running Mode                        | 28  |

|    | 9.2.2.6. SM – Start Measurement                           | 28  |

|    | 9.2.2.7. RO – Start Read-Out                              | 30  |

|    | 9.2.2.8. SM+RO - Start Measurement combined with Read-Out | 33  |

|    | 9.2.2.9. WR/RR – Write/Read Register                      | 34  |

|    | 9.2.2.10. SD – Start Diagnostics                          | 35  |

|    | 9.3. Internal Status Flags                                | 37  |

|    | 9.4. User Registers Overview                              | 39  |

|    | 9.4.1. SetAna register                                    |     |

|    | 9.4.2. SetAH register                                     |     |

|    | 9.4.3. SetAL register                                     |     |

|    | 9.4.4. SetBH register                                     |     |

|    | 9.4.5. SetBL register                                     | 42  |

Datasheet

| 9.4.6. SetPF register                                                                             | 43 |

|---------------------------------------------------------------------------------------------------|----|

| 9.4.7. Err register                                                                               | 44 |

| 9.4.8. Rst register                                                                               | 45 |

| 9.4.9. DCComp register                                                                            | 45 |

| 9.4.10. GainBuf register                                                                          | 46 |

| 9.4.11. Calib1/Calib2 register                                                                    | 47 |

| 9.4.12. EnChan register                                                                           | 51 |

| 9.4.13. Tamb register                                                                             | 52 |

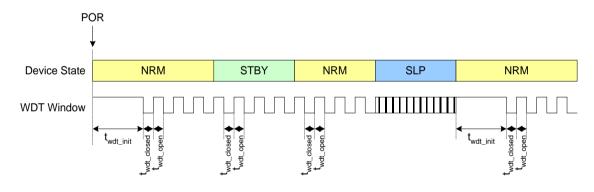

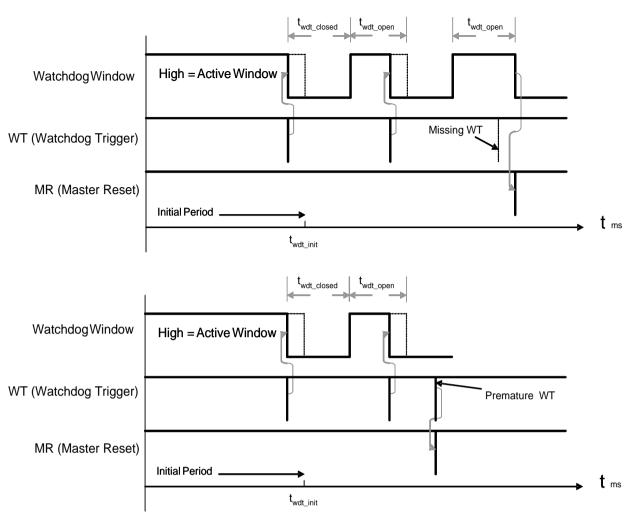

| 9.5. Window Watchdog Timer                                                                        | 53 |

| 9.6. Reset Behaviour                                                                              | 55 |

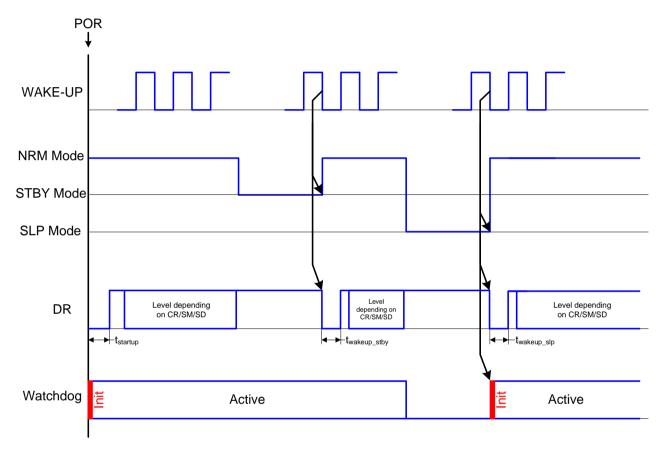

| 9.7. Wake-up from Sleep or Standby                                                                | 56 |

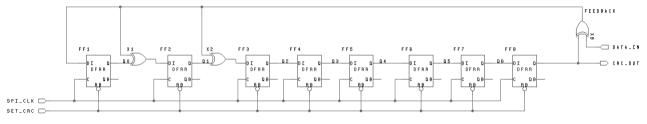

| 9.8. CRC Calculation                                                                              | 57 |

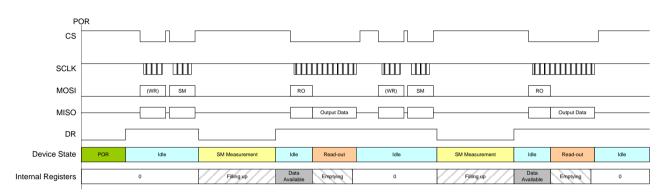

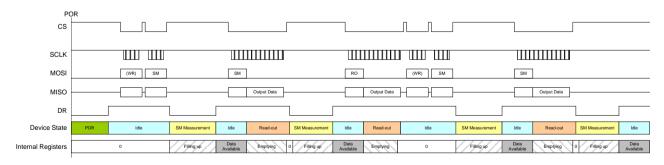

| 9.9. Global Timing Diagrams                                                                       | 58 |

| 10. Performance Graphs                                                                            | 59 |

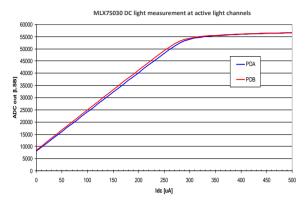

| 10.1. ActiveLight Channel DC Measurement                                                          | 59 |

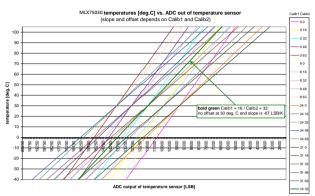

| 10.2. Temperature Sensor Characteristics                                                          | 59 |

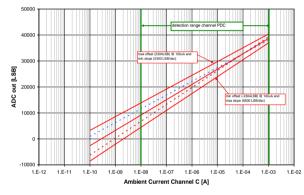

| 10.3. Ambient Light Channel C                                                                     |    |

| 10.4. Ambient Light Channel D                                                                     |    |

| 11. Application Information                                                                       |    |

| 11.1. Application circuit for 2 ActiveLight channels and 2 ambient light channels                 | 60 |

| 12. Application Comments                                                                          |    |

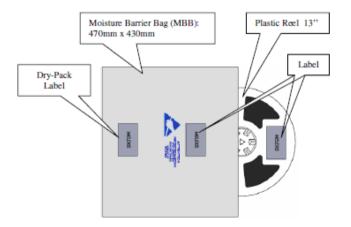

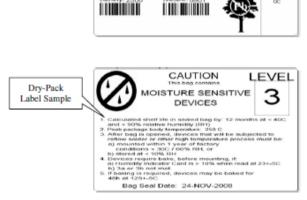

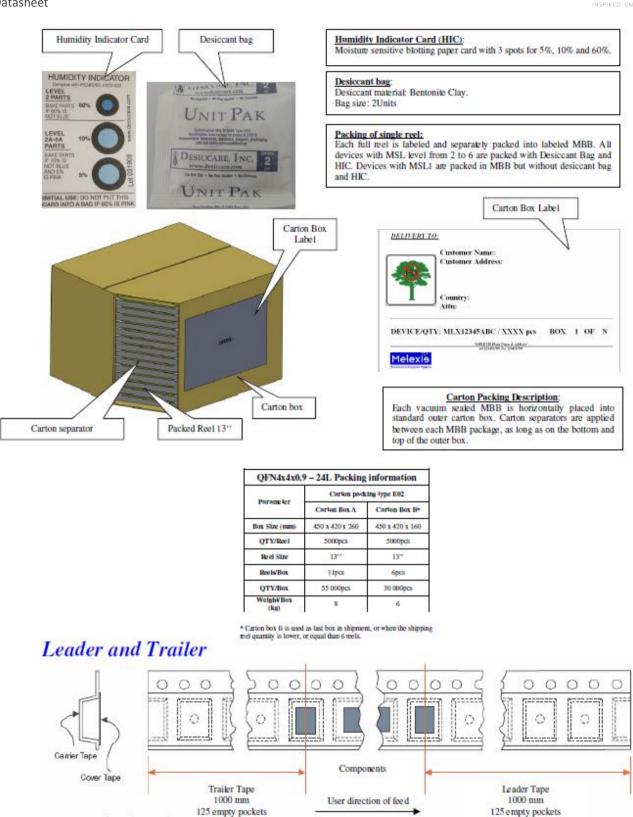

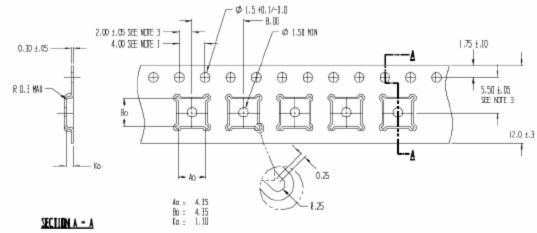

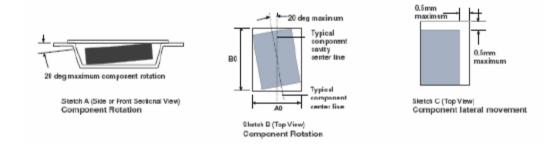

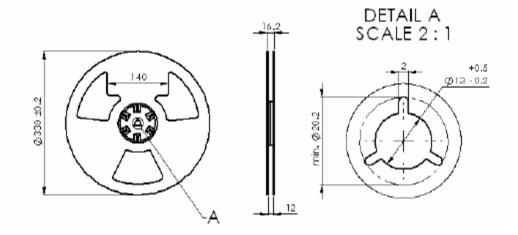

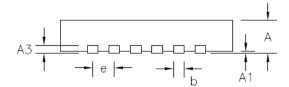

| 13. Tape and Reel Specification                                                                   |    |

| 14. Standard information regarding manufacturability of Melexis products with different soldering |    |

| processes                                                                                         |    |

| 15. ESD Precautions                                                                               |    |

| 16. Package Information                                                                           |    |

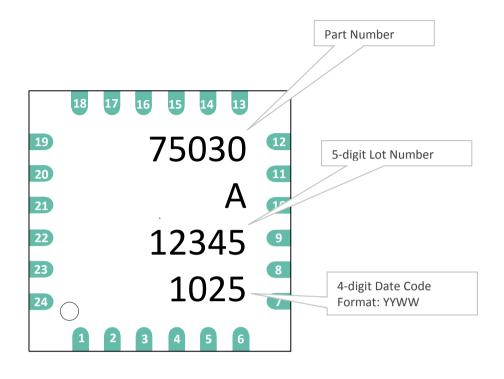

| 17. Marking Information                                                                           |    |

| 18. Disclaimer                                                                                    | 68 |

|                                                                                                   |    |

# 4. Glossary of Terms

| ADC      | Analog-Digital converter                              |

|----------|-------------------------------------------------------|

| CR       | Chip Reset                                            |

| CRC      | Cyclic Redundancy Check                               |

| CS       | Chip Select                                           |

| CSLP     | Confirm Sleep                                         |

| CSTBY    | Confirm Standby                                       |

| CTRL     | Control Signal                                        |

| DAC      | Digital to Analog Converter                           |

| DC       | Direct Current                                        |

| DR       | Device Ready                                          |

| EMC      | Electromagnetic Compatibility                         |

| GNDA     | Ground for analog Blocks of MLX7530                   |

| GNDD     | Ground for digital Blocks of MLX75030                 |

| IR       | Infrared                                              |

| LED      | Light emitting diode                                  |

| LPF      | Low-pass filter                                       |

| LSB      | Least Significant Bit                                 |

| MISO     | Master In Slave Out                                   |

| MOSI     | Master Out Slave In                                   |

| MR       | Master Reset                                          |

| MSB      | Most Significant Bit                                  |

| MUX      | Multiplexer                                           |

| NOP      | No Operation                                          |

| NP       | Number of Pulses                                      |

| NRM      | Normal Running Mode                                   |

| OSC      | Oscillator                                            |

| OTP      | One time programmable                                 |

| OTR      | Optical transfer ratio                                |

| PD       | Photodiode                                            |

| POR      | Power on reset                                        |

| RCO      | RC-Oscillator                                         |

| RO       | Read-Out                                              |

| RR       | Read Register                                         |

| RSLP     | Request Sleep                                         |

| RSTBY    | Request Standby                                       |

| S&H      | Sample and Hold                                       |

| SCLK     | SPI Shift Clock                                       |

| SC-LPF   | Switched Capacitor biquad Low-pass filter             |

| SM       | Start Measurement                                     |

| SNR      | Signal-to-Noise Ratio                                 |

| SPI      | Serial Peripheral Interface                           |

| TIA      | Transimpedance Amplifier                              |

| VBATT_30 | VBATT which is supplied from connection 30 of the car |

| VCCA     | Supply Voltage for the analog blocks                  |

| VCCD     | Supply Voltage for the digital blocks                 |

| VDD_30   | VDD which is supplied from connection 30 of the car   |

| VSENSE   | Voltage across the shunt resistor                     |

| WDT      | Watchdog Timer                                        |

| WR       | Write Register                                        |

| WT       | Watchdog Trigger                                      |

| uC       | Microcontroller                                       |

|          |                                                       |

Datasheet

# **5. Absolute Maximum Ratings**

Exceeding the absolute maximum ratings may cause permanent damage. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| Parameter                                          | Symbol                | Condition                                                       | Min  | Max                  | Units |

|----------------------------------------------------|-----------------------|-----------------------------------------------------------------|------|----------------------|-------|

| Supply voltage range                               | V <sub>DD</sub>       |                                                                 | -0.3 | 5.0                  | V     |

| Terminal current                                   | I <sub>terminal</sub> | per bondpad                                                     | -20  | +20                  | mA    |

| Terminal voltage                                   | V <sub>terminal</sub> | Pins 1-8, 14-24                                                 | -0.3 | V <sub>DD</sub> +0.3 | V     |

| Terminal voltage                                   |                       | <i>Pins 9-13</i> <sup>1</sup>                                   | -0.3 | V <sub>DD</sub> +0.3 | V     |

| Storage temperature                                | T <sub>stg</sub>      |                                                                 | -40  | +150                 | °C    |

| Junction temperature                               | Tj                    |                                                                 |      | +150                 | °C    |

| Power dissipation <sup>2</sup>                     | P <sub>tot</sub>      | For max ambient temperature of<br>100°C and<br>Teta_ja = 154K/W |      | 320                  | mW    |

| ESD capability of any pin                          | ESD <sub>HBM</sub>    | Human body model,<br>acc. to AEC-Q100-002                       | -2   | 2                    | kV    |

| (Human Body Model)                                 |                       | Pins 9-13                                                       | -1   | 1                    | kV    |

| ESD capability of any pin<br>(Charge device model) | ESD <sub>CDM</sub>    | Charge device model<br>acc. to AEC- Q100-011                    | -750 | +750                 | V     |

| Maximum latch-up free current at any pin           | I <sub>LATCH</sub>    | JEDEC- Standard EIA / JESD78                                    | -100 | +100                 | mA    |

Table 1 : Absolute Maximum Ratings

<sup>&</sup>lt;sup>1</sup> Pins 9-13 require special care with regard to the used ESD protection devices, since these nodes of the design are very sensitive to substrate noise and/or leakage currents.

$<sup>^2</sup>$  The Power dissipation is valid for  $\mathcal{G}_{JA}$  values for the 24 Pin QFN 4x4 package according to Table 27.

# 6. Pin Definitions & Descriptions

| Pin<br>NՉ | Name                      | Functional<br>Schematic | Туре           | Function                    |

|-----------|---------------------------|-------------------------|----------------|-----------------------------|

| 1         | \MR                       |                         | Digital Output | Master Reset                |

| 2         | \WT                       |                         | Digital Input  | Watchdog Trigger            |

| 3         | SCLK                      |                         | Digital Input  | SPI Shift Clock             |

| 4         | MISO                      |                         | Digital Output | SPI Data Output             |

| 5         | MOSI                      |                         | Digital Input  | SPI Data Input              |

| 6         | \CS                       |                         | Digital Input  | Chip Select                 |

| 7         | DR                        |                         | Digital Output | Device Ready                |

| 8         | \WAKE-UP                  |                         | Digital Input  | Normal Mode                 |

| 9         | ActiveLight<br>Detect PDA |                         | Analog Input   | IR Photo Diode A            |

| 10        | ActiveLight<br>Detect PDB |                         | Analog Input   | IR Photo Diode B            |

| 11        | Ambient PDC               |                         | Analog Input   | Ambient Light Photo Diode C |

| 12        | Ambient PDD               |                         | Analog Input   | Ambient Light Photo Diode D |

Datasheet

-

| 13 | DIAGAMB     |                                       | Analog Input  | Ambient channel diagnostic               |

|----|-------------|---------------------------------------|---------------|------------------------------------------|

| 14 | GNDAMB      |                                       | Analog I/O    | Ground Ambient Light Channels            |

| 15 | GNDA        |                                       | Ground        | Ground                                   |

| 16 | VCCA        |                                       | Supply        | Regulated Power Supply                   |

| 17 | AOUT        |                                       | Analog I/O    | Analog Test Output, connect to VCCA      |

| 18 | Shunt R GND |                                       | Analog Input  | Shunt resistor feedback to Ground        |

| 19 | Shunt R-    |                                       | Analog Input  | Shunt resistor feedback                  |

| 20 | Drive LED B | PAD<br>T                              | Analog Output | Drives FET gate for IR LED Emitter B     |

| 21 | Drive LED A | → → → → → → → → → → → → → → → → → → → | Analog Output | Drives FET gate for IR LED Emitter A     |

| 22 | CEXT        |                                       | Analog Input  | External blocking Cap, connected to GNDA |

| 23 | VCCD        |                                       | Supply        | Regulated external power supply          |

| 24 | GNDD        |                                       | Ground        | Ground                                   |

Table 2 : Pin definitions and descriptions

**Melexis**

# 7. General Electrical Specifications

DC Operating Parameters  $T_A = -40^{\circ}$ C to  $105^{\circ}$ C (R version),  $T_A = 0^{\circ}$ C to  $70^{\circ}$ C (C version),  $V_{DD} = 3.0$ V to 3.6V (unless otherwise specified)

| Parameter                           | Symbol             | Test Conditions               | Min                 | Тур  | Max                 | Units |

|-------------------------------------|--------------------|-------------------------------|---------------------|------|---------------------|-------|

| Supply Voltage range                | V <sub>DD</sub>    |                               | 3.0                 | 3.3  | 3.6                 | V     |

| Supply Current (active Mode)        | I <sub>DD</sub>    | without photodiode dc current |                     |      | 6                   | mA    |

| Standby Current                     | I <sub>SBY</sub>   | @ Vcc=3.6V, T=30°C            |                     |      | 500                 | uA    |

| Sleep Current                       | I <sub>Sleep</sub> | @ Vcc=3.6V, T=30°C            |                     |      | 50                  | uA    |

| Operation Temperature Range         | T <sub>A</sub>     |                               | -40                 |      | 105                 | °C    |

| Pull-up resistor                    | Rpu                | for SCLK and \CS              |                     | 50k  |                     | Ohm   |

| Pull-down resistor                  | Rpd                | for MOSI                      |                     | 50k  |                     | Ohm   |

| High-level Input Voltage            | V <sub>IH</sub>    |                               | 0.7 V <sub>DD</sub> |      | V <sub>DD</sub>     | V     |

| Low-level Input Voltage             | V <sub>IL</sub>    |                               | 0                   |      | 0.3 V <sub>DD</sub> | V     |

| Hysteresis on Digital Inputs        | V <sub>HYST</sub>  |                               |                     | 0.28 |                     | V     |

| High Output Voltage (not on pin MR) | V <sub>OH</sub>    | C <sub>L</sub> =30pF          | 0.8 V <sub>DD</sub> |      | V <sub>DD</sub>     | V     |

| Low Output Voltage (not on pin MR)  | V <sub>OL</sub>    | C <sub>L</sub> =30pF          | 0                   |      | 0.2 V <sub>DD</sub> | V     |

| Input leakage                       | I <sub>LK</sub>    |                               | -10                 |      | 10                  | μΑ    |

| Tri-state Output Leakage Current    | I <sub>oz</sub>    |                               | -10                 |      | 10                  | μΑ    |

| Input Capacitance, per Pin          | C <sub>IN</sub>    |                               |                     | 10   |                     | pF    |

| Output voltage Low, Pin MR          | V <sub>OutL</sub>  | I <sub>ODC</sub> =2mA         |                     |      | 0.1                 | V     |

Table 3 : Electrical specifications

Datasheet

# 8. Sensor Specific Specifications

DC Operating Parameters  $T_A = -40^{\circ}$ C to  $105^{\circ}$ C,  $T_A = 0^{\circ}$ C to  $70^{\circ}$ C (C version),  $V_{DD} = 3.0V$  to 3.6V (unless otherwise specified)

| Parameter                                                                    | Symbol                                  | Test Conditions                                                                                                                                                  | Min   | Тур   | Max   | Units  |

|------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| Active light signal optical transfer ratio                                   | $OTR = \frac{I_{LED}}{I_{PDAB}}$        |                                                                                                                                                                  | 30    |       | 80000 |        |

| dc sunlight signal                                                           | I <sub>Sun</sub>                        |                                                                                                                                                                  | 140   |       | 900   | uA     |

| fast full scale transition at $I_{sunmax}$                                   | t <sub>sunrise</sub>                    |                                                                                                                                                                  | 3.5   |       |       | ms     |

| min. relative active light<br>modulation<br>(referred to received IR signal) | $\frac{\Delta I_{PDAB\_min}}{I_{PDAB}}$ | <ul> <li>400Hz BW,</li> <li>max LED current of 1000mA</li> <li>25°C</li> <li>dc sun constant</li> <li>ActiveLight response time<br/>per channel 2.5ms</li> </ul> |       |       | 0.3   | %      |

| Carrier frequency range for<br>ActiveLight measurement                       | f <sub>o</sub>                          | selectable via "SetPF"<br>register, see also 9.4.6                                                                                                               | 45.7  |       | 109.4 | kHz    |

| Input capacitance PDA, PDB                                                   | C <sub>PDA,B</sub>                      | At 1.0 V reverse bias                                                                                                                                            |       |       | 10    | pF     |

| DC light measurement range                                                   | I <sub>DC range</sub>                   |                                                                                                                                                                  | 0     |       | 275   | uA     |

| DC light measurement offset                                                  | I <sub>DC offset</sub>                  | At I <sub>DC</sub> = 0uA                                                                                                                                         | 4096  | 7168  | 10240 | LSB    |

| DC light measurement slope                                                   | I <sub>DC sens</sub>                    |                                                                                                                                                                  | 115   | 150   | 184   | LSB/uA |

| DC light measurement                                                         |                                         | Idc range: OuA -> 275uA                                                                                                                                          |       | 5     | 12    | %      |

| DC light measurement word                                                    |                                         |                                                                                                                                                                  |       | 16    |       | Bit    |

| DC light measurement                                                         |                                         | for averaging of 8                                                                                                                                               |       | 13    |       | Bit    |

| TIA Test pulse                                                               | ADC <sub>TIA_test_00</sub>              | T=27°C,<br>DACA6=0, DACA7=0<br>Gain Anti-alias Filter=2<br>ADC Buffer bypassed                                                                                   | 35035 | 36182 | 37570 | LSB    |

| Temperature coefficient of<br>TIA Test pulse                                 | TC ADC <sub>TIA_test_00</sub>           | DACA6=0, DACA7=0<br>Gain Anti-alias Filter=2<br>ADC Buffer bypassed                                                                                              |       | -2.78 |       | LSB/K  |

| TIA Test pulse step width                                                    | ADC <sub>TIA_test_step</sub>            | T=27°C,<br>Gain Anti-alias Filter=2<br>ADC Buffer bypassed                                                                                                       | 4458  | 5932  | 7770  | LSB    |

| Temperature coefficient of<br>TIA Test pulse step width                      | TC ADC <sub>TIA_test_step</sub>         | Gain Anti-alias Filter=2<br>ADC Buffer bypassed                                                                                                                  |       | -4.8  |       | LSB/K  |

| ΓΙΑ Test pulse step width<br>variation                                       | $\Delta_{ADC\_TIA\_TEST\_STEP}$         | Gain Anitalias Filter=2<br>ADC Buffer bypassed                                                                                                                   |       | 5     | 10    | %      |

Critical error detected on TIA output, is TIA output outside 1.1V+/- (0.65  $\dots$  0.75V) Note:

• Critical error may occur if the referring active light Channel is disabled and the according diagnostic function is enabled (see EnChan register).

• Critical error may occur after enabling of the referring active light Channel due to analog settling time.

Table 4 : ActiveLight sensor channels specifications

Datasheet

| ActiveLig                                              | ght Channe                | I DC-Light Compensat                                           | tion  |       |       |       |

|--------------------------------------------------------|---------------------------|----------------------------------------------------------------|-------|-------|-------|-------|

| Parameter                                              | Symbol                    | Test Conditions                                                | Min   | Тур   | Max   | Units |

| Maximum ActiveLight Signal DC-Light compensation range | RS <sub>COMP_max</sub>    | in percent of LED current<br>DC_COMP_IC1,2,3,4,5=15<br>DAC=255 | 15    | 20    |       | %     |

| ActiveLight Signal Compensation<br>Offset              | RS <sub>COMP_Offset</sub> | in percent of LED current<br>@ Idc = 0uA                       |       |       | 0.8   | %     |

| Range of segment 1                                     | lamb_1                    | 1 <sup>rst</sup> corner dc current                             | 7.2   | 10.0  | 12.0  | uA    |

| Range of segment 2                                     | lamb_2                    | 2 <sup>nd</sup> corner dc current                              | 40.0  | 45.0  | 50.0  | uA    |

| Range of segment 3                                     | lamb_3                    | 3 <sup>rd</sup> corner dc current                              | 135.0 | 150.0 | 165.0 | uA    |

| Range of segment 4                                     | lamb_4                    | 4 <sup>th</sup> corner dc current                              | 440.0 | 500.0 | 560.0 | uA    |

| Full compensation level @ segment 1                    | lcomp_1                   | DC_COMP_IC1,2,3,4,5 = 15                                       | 1.5   | 3.5   | 4.7   | %     |

| Full compensation level @ segment 2                    | Icomp_2                   | DAC=255<br>in percent of LED current                           | 5.1   | 7.7   | 10.3  | %     |

| Full compensation level @ segment 3                    | Icomp_3                   | In percent of LED current                                      | 9.5   | 13.7  | 17.9  | %     |

| Full compensation level @ segment 4                    | Icomp_4                   | -                                                              | 13.6  | 18.8  | 24.0  | %     |

| Full compensation level @ 900uA<br>(max DC sunlight)   | lcomp_5                   | -                                                              | 15.0  | 20.7  | 25.8  | %     |

| Full compensation level @ segment 1                    | lcomp_1                   | DC_COMP_IC1,2,3,4,5 = 7                                        | 0.65  | 1.6   | 2.2   | %     |

| Full compensation level @ segment 2                    | lcomp_2                   | DAC=255                                                        | 2.4   | 3.6   | 4.8   | %     |

| Full compensation level @ segment 3                    | Icomp_3                   | in percent of LED current                                      | 4.4   | 6.4   | 8.4   | %     |

| Full compensation level @ segment 4                    | lcomp_4                   |                                                                | 6.3   | 8.85  | 11.4  | %     |

| Full compensation level @ 900uA<br>(max DC sunlight)   | Icomp_5                   |                                                                | 7.1   | 9.6   | 12.1  | %     |

| DC_COMP_IC1 = 15, other =0                             | I <sub>C_1</sub>          | in percent of LED current                                      | 1.4   | 2.3   | 2.8   | %     |

| DC_COMP_IC2 = 15, other =0                             | I <sub>C_2</sub>          | in percent of LED current                                      | 2.1   | 2.9   | 3.6   | %     |

| DC_COMP_IC3 = 15, other =0                             | I <sub>C_3</sub>          | in percent of LED current                                      | 5.0   | 6.6   | 8.2   | %     |

| DC_COMP_IC4 = 15, other =0                             | I <sub>C_4</sub>          | in percent of LED current                                      | 4.4   | 5.9   | 7.3   | %     |

| DC_COMP_IC5 = 15, other =0                             | I <sub>C_5</sub>          | in percent of LED current                                      | 2.0   | 3.0   | 4.1   | %     |

Table 5: DC light compensation specifications

Datasheet

|                                       | Ambient                  | t Light Channels (d                                                                               | etectors | C, D) |       |         |

|---------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|----------|-------|-------|---------|

| Parameter                             | Symbol                   | Test Conditions                                                                                   | Min      | Тур   | Max   | Units   |

| nput current range for<br>detectors C | I <sub>ambc</sub>        |                                                                                                   | 0.01     |       | 1040  | uA      |

| nput current range for<br>detectors D | I <sub>ambd</sub>        |                                                                                                   | 0.0005   |       | 20    | uA      |

| nput current threshold level          | $I_{ambc\_detect}$       |                                                                                                   | 333      |       |       | nA      |

| input current threshold level         | I <sub>ambd_detect</sub> |                                                                                                   | 5.5      |       |       | nA      |

| nput capacity on ambient              | C <sub>ambc</sub>        | at 0.6V                                                                                           |          |       | 1     | nF      |

| nput capacity on ambient              | Cambd                    | at 0.6V                                                                                           |          |       | 100   | pF      |

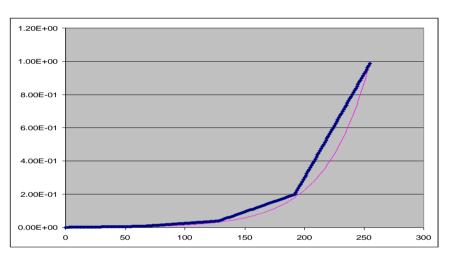

| Transfer function logarithmic         | V <sub>amb</sub>         | See section 10.3 and 10.4                                                                         |          |       |       |         |

| Output Ambient Channel C              |                          | At VCC=3,3V, lin=100uA                                                                            | 29464    | 32768 | 36072 | LSB     |

| Output Ambient Channel D              |                          | At VCC=3,3V, lin=10uA                                                                             | 29464    | 32768 | 36072 | LSB     |

| Slope Ambient Channel C               |                          | At VCC=3,3V and 105°C                                                                             | 5300     | 5900  | 6500  | LSB/dec |

| Slope Ambient Channel D               |                          | At VCC=3,3V and 105°C                                                                             | 5300     | 5900  | 6500  | LSB/dec |

| Ambient Channels Linearity<br>Error   |                          | for lin ≥ I <sub>ambx_detect</sub><br>including temperature<br>compensation                       |          | 3     | 5     | %       |

| Ambient light word length             |                          |                                                                                                   |          | 16    |       | bits    |

| Ambient light channel<br>resolution   |                          | for averaging of 16<br>measurements                                                               |          | 13    |       | bits    |

| Ambient light response time           |                          | See section 9.1.3 for a detailed explanation of this parameter.<br>for lin $\ge I_{ambx\_detect}$ |          |       | 3     | ms      |

| Ambient PDC voltage                   | V <sub>ambc</sub>        | At VCC=3,3V, lin=100uA                                                                            | 0.4      | 0.6   | 0.9   | V       |

| Ambient PDD voltage                   | V <sub>ambd</sub>        | At VCC=3,3V, lin=10uA                                                                             | 0.4      | 0.6   | 0.9   | V       |

Note:

• Err3 is set if output voltage OUTN or OUTP of the ambient channel SC filter is out of range (meaning: <40% of VCCA or >60% of VCCA). Critical error may occur after enabling of the referring Ambient Light Channel due to analog settling time.

Table 6 : Ambient light channel specifications

**Melexis**

| Datasheet |

|-----------|

|-----------|

| Temperature Sensor                          |                           |                                          |     |     |     |       |  |

|---------------------------------------------|---------------------------|------------------------------------------|-----|-----|-----|-------|--|

| Parameter                                   | Symbol                    | Test Conditions                          | Min | Тур | Мах | Units |  |

| Temp. sensor range                          | θ                         |                                          | -40 |     | 105 | °C    |  |

| Temp. sensor transfer function <sup>3</sup> | Və                        | @ VDD=3,3V                               | -82 | -67 | -51 | LSB/K |  |

| Temp. sensor error                          | θ <sub>error@0…105℃</sub> | @ VDD=3,3V,<br>T <sub>amb</sub> = 0105°C |     |     | ±5  | °C    |  |

| Temp. response time                         | t <sub>resp_9</sub>       |                                          |     |     | 1   | S     |  |

| Temp. sensor word length                    |                           |                                          |     | 16  |     | bits  |  |

| Temp. sensor resolution                     |                           | for averaging of 16<br>measurements      |     | 13  |     | bits  |  |

Table 7 : Temperature sensor specifications

| LED Driver              |                       |                                |       |     |                                       |       |  |

|-------------------------|-----------------------|--------------------------------|-------|-----|---------------------------------------|-------|--|

| Parameter               | Symbol                | Test Conditions                | Min   | Тур | Max                                   | Units |  |

| LED current             |                       | Shunt = 1 Ω                    | 1.05  |     | 993                                   | mA    |  |

| Shunt resistor values   |                       |                                | 1     |     | 10                                    | Ohm   |  |

| Shunt voltage           |                       |                                | 1.05  |     | 993                                   | mV    |  |

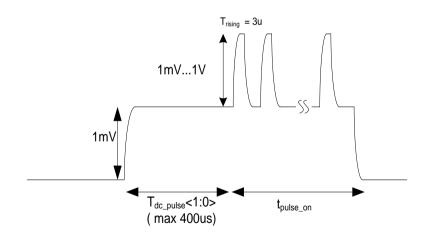

| Rising and falling time |                       |                                |       | 3   |                                       | us    |  |

| DC offset level         |                       |                                |       | 1   |                                       | mV    |  |

| Time before pulse       | T <sub>dc_pulse</sub> | See section 9.4.1              | 47.5  |     | 420                                   | us    |  |

|                         | Exter                 | nal important transistor param | neter |     |                                       |       |  |

| Max gate source voltage | V <sub>GS</sub>       | VDD=3V                         |       |     | 2                                     | V     |  |

| Max Gate/Basis current  | I <sub>G/B</sub>      | VDD=3V                         |       |     | 400                                   | uA    |  |

|                         |                       | Error condition Err5           |       | `   | i i i i i i i i i i i i i i i i i i i |       |  |

Table 8 : LED driver specifications

| POR                       |                      |                 |      |     |      |       |  |  |

|---------------------------|----------------------|-----------------|------|-----|------|-------|--|--|

| Parameter                 | Symbol               | Test Conditions | Min  | Тур | Max  | Units |  |  |

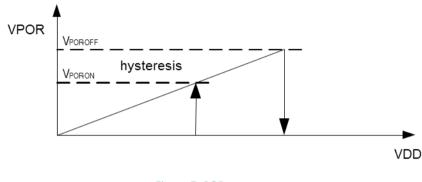

| POR on threshold voltage  | V <sub>POR-ON</sub>  |                 | 1.58 |     | 2.75 | V     |  |  |

| POR off threshold voltage | V <sub>POR-OFF</sub> |                 | 1.68 |     | 2.85 | V     |  |  |

| POR hysteresis voltage    | V <sub>HYS</sub>     |                 | 60   |     | 130  | mV    |  |  |

Table 9: Power on Reset specifications

<sup>3</sup> This value is stored in the Calib1 Register

| SPI and Timing                           |                          |                                          |            |              |                               |       |  |

|------------------------------------------|--------------------------|------------------------------------------|------------|--------------|-------------------------------|-------|--|

| Parameter                                | Symbol                   | Test Conditions                          | Min        | Тур          | Max                           | Units |  |

| SPI word length                          |                          |                                          |            |              | 8                             | bit   |  |

| SPI Clock Frequency                      | $f_{SCLK} = 1/t_{SCLK}$  |                                          | 0.5        | 1            | 5                             | MHz   |  |

| Frequency of Internal RC Oscillator      | $f_{RCO} = 1/T_{RCO}$    |                                          |            | 2.5          | ±7.5%                         | MHz   |  |

| CS low prior to first SCLK edge          | t <sub>cs_sclk</sub>     |                                          | 50         |              |                               | ns    |  |

| CS high after last SCLK edge             | t <sub>sclk_cs</sub>     |                                          | 50         |              |                               | ns    |  |

| CS high time between transmissions       | t <sub>cs_inter</sub>    |                                          | 50         |              |                               | ns    |  |

| Time between CS high and DR low          | t <sub>cs_dr</sub>       |                                          | 0          |              | 21.84<br>(232us) <sup>4</sup> | μs    |  |

| Min low time on WAKE_UP pin              | t <sub>wu_l</sub>        |                                          | 100        |              |                               | μs    |  |

| Min low time on WT pin                   | t <sub>wt_l</sub>        |                                          | 10         |              |                               | μs    |  |

| WDT initial active window time           | t <sub>wdt_init</sub>    | After POR, Watchdog<br>Reset and Wake-Up |            | 140          | ±7.5%                         | ms    |  |

| WDT open window time                     | t <sub>wdt_open</sub>    |                                          |            | 70           | ±7.5%                         | ms    |  |

| WDT closed window time                   | t <sub>wdt_closed</sub>  |                                          |            | 70           | ±7.5%                         | ms    |  |

| MR low time during reset                 | t <sub>MR</sub>          | After Watchdog Reset                     |            | 2            | ±7.5%                         | ms    |  |

| Start-up time after power-on             | t <sub>startup</sub>     |                                          |            | 50           | ±7.5%                         | ms    |  |

| Start-up time after power-on for SPI     | t <sub>startup_SPI</sub> |                                          |            |              | 15                            | μs    |  |

| Start-up time after wake-up from sleep   | twakeup_slp              |                                          |            | 50           | ±7.5%                         | ms    |  |

| Start-up time after wake-up from standby | t <sub>wakeup_stby</sub> |                                          |            | 50           | ±7.5%                         | ms    |  |

|                                          | Error                    | condition Err2                           |            |              |                               |       |  |

|                                          | RCO stu                  | ck at High or Low                        |            |              |                               |       |  |

|                                          | Error                    | condition Err4                           |            |              |                               |       |  |

| Internal voltage regulator : err4 is     | set if the regula        | tor does not start (detection            | on thresho | old in the r | ange [1V;2V]                  |       |  |

Table 10 : Serial peripheral interface specifications

<sup>4</sup> with random measurement start, the max time can be up to 232us, if an autozeroing phase of the IC is executed.

**Melexis**

# 9. Detailed Description

## 9.1. Analog Sensor Functions

## 9.1.1. Active Light Sensor

The MLX75030 works with two separate transmit- and receive-channels A and B. In order to perform an active light measurement, carrier modulated light signal bursts are transmitted by the LED(s) and received by the ActiveLight channel detectors connected to the pins 9 and 10. Both receive-channels can work separate or in parallel.

The measured ActiveLight signal current is amplified and converted to digital numbers by the on-board ADC by following formula:

$$A_{ActiveLightADC} = I_{ActiveLightPD} \frac{4.10^4 * K_{DEMOD} * GAIN ADJ AA * GAIN BUF}{50,3 \frac{\mu V}{LSB}} + 2^{15}$$

Where

- A<sub>ActiveLightADC</sub> is the ActiveLight signal value in DN

- *I<sub>ActiveLightPD</sub>* is the ActiveLight signal current in uA

- K<sub>DEMOD</sub> is a correlation gain value between 0.25 and 0.5, depending on the setting of Tdem bits in register SetAna

- GAIN\_ADJ\_AA is the Anti-aliasing filter gain, set by SetAL and SetBL registers, defaulting to value 2

- GAIN\_BUF is the ADC input buffer gain, set by SetAna and GainBuf registers, defaulting to value 1

It is recommended to use the default values of  $GAIN\_ADJ\_AA$  and  $GAIN\_BUF$ . It is recommended to optimize the value of  $K_{DEMOD}$ .

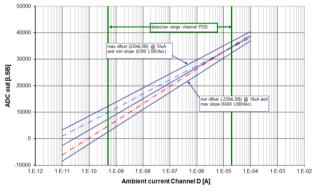

### 9.1.1.1. Active Light Channel DC Light Measurement

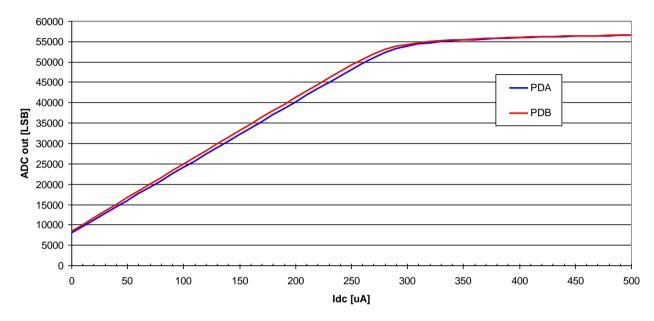

The input DC current compensation circuitry of the transimpedance amplifier is able to supply and measure the dc current supplied to the photodetector. Both active light channels are identical in structure. In order to reach a feasible resolution in the current range of interest (low currents in the range up to 275uA), the measurement characteristic will saturate for currents above the I<sub>DC</sub> current range, however the compensation circuit is nevertheless able to supply the specified current levels up to 900uA to the detector. The given ADC word length for the active light channel dc light data is 16Bit.

The DC light measurement can be used to estimate ambient light conditions and compensate DC light dependent parameters (see next section).

Figure 3: Typical ActiveLight channel DC measurement characteristics for both channels A and B

## 9.1.2. ActiveLight Channel DC Light compensation

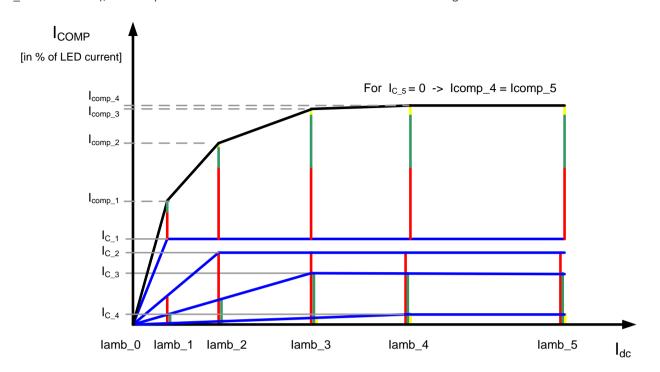

Under certain operating conditions, the spectral sensitivity of some photodiodes is not constant and varies with the amount of (infrared) dc-light received. For the ActiveLight measurements this means that the ActiveLight signal can change rapidly if the sensor experiences highly changing sunlight conditions, even if all other conditions are constant. This results in reduced ActiveLight signal sensitivity of the system under changing dc-light conditions.

The variation of the ActiveLight signals as a function of DC-light can be partially compensated by automatically adapting the amplitude of the sensors' transmitted infrared light pulses for ActiveLight measurement.

In order to make the system as flexible as possible, the compensation can be adapted to different photodiode types by definition of the compensation characteristics as a piecewise linear curve like described in Figure 4. The values of the 5 corner points of the curve can be defined by the corresponding 4-Bit words PD\_COMP\_ICx<3:0> (x = 1..5) in the register maps, see section 9.4. The PD light compensation can be enabled by setting the EN\_PDCOMP bit to "1".

In order to calculate the decimal values PD\_COMP\_ICx<3:0> (x = 1..5) for a certain photodiode, one has to measure the relative ActiveLight signal levels  $p_x$  at 5 different DC light levels  $I_{amb_x}$  while the EN\_PDCOMP is set to "0" (a calculation example is given below, where  $A@Iamb_x$  is the measured ActiveLight signal at DC light signal  $I_{amb_x}$ ):

$p_0$  = pulse level at ( $I_{amb_0}$  = 0) = 1 (this is the 100% reference)

Datasheet

$$p_{1} = \text{pulse level at } (I_{amb_{1}} = 10\text{uA}) = \text{e.g. } 0.97440 = \frac{A @ Iamb_{0} - 2^{15}}{A @ Iamb_{1} - 2^{15}}$$

$$p_{2} = \text{pulse level at } (I_{amb_{2}} = 45\text{uA}) = \text{e.g. } 0.94224 = \frac{A @ Iamb_{0} - 2^{15}}{A @ Iamb_{0} - 2^{15}}$$

$$p_{3} = \text{pulse level at } (I_{amb_{3}} = 150\text{uA}) = \text{e.g. } 0.91556 = \dots$$

$$p_{4} = \text{pulse level at } (I_{amb_{4}} = 500\text{uA}) = \text{e.g. } 0.89858 = \dots$$

$$p_{5} = \text{pulse level at } (I_{amb_{5}} = 900\text{uA}) = \text{e.g. } 0.89477 = \dots$$

Based on these relative ActiveLight pulse levels, one can calculate the following parameters (x = 1..5):

$$r_{comp_i} = 3 \cdot 10^{-5} (1 - p_x)$$

| Ycomp_1             | 1 |   | 1  | .285714 | -0.28571 | 0        | 0        | 0        |   | r <sub>comp_1</sub> |

|---------------------|---|---|----|---------|----------|----------|----------|----------|---|---------------------|

| Y <sub>comp_2</sub> | 2 |   | -1 | 1.28571 | 1.714286 | -0.42857 | -1.8E-17 | 1.78E-17 |   | r <sub>comp_2</sub> |

| Ycomp_3             | 3 | = | 0  | )       | -1.42857 | 1.857143 | -0.42857 | -7.9E-17 | • | r <sub>comp_3</sub> |

| Y <sub>comp_4</sub> | 1 |   | 0  | )       | 0        | -1.42857 | 2.678571 | -1.25    |   | r <sub>comp_4</sub> |

| Ycomp_5             | 5 |   | 0  | )       | 0        | 0        | -2.25    | 2.25     |   | r <sub>comp_5</sub> |

For the calculation example, we get the following values:

| r <sub>comp_1</sub> |   | 7.68E-07 |

|---------------------|---|----------|

| r <sub>comp_2</sub> |   | 1.73E-06 |

| r <sub>comp_3</sub> | = | 2.53E-06 |

| r <sub>comp 4</sub> |   | 3.04E-06 |

| r <sub>comp_5</sub> |   | 3.16E-06 |

The settings PD\_COMP\_ICx<3:0> (x = 1..5) can be derived from the  $y_{comp_x}$  (x = 1..5) as follows:

$$PD\_COMP\_IC1[3:0] = round \left(\frac{y_{comp\_1}}{0.4 \times 0.132 \ 10^{-6}}, 0\right)$$

$$PD\_COMP\_IC2[3:0] = round \left(\frac{y_{comp\_2}}{0.4 \times 0.165 \ 10^{-6}}, 0\right)$$

$$PD\_COMP\_IC3[3:0] = round \left(\frac{y_{comp\_3}}{0.4 \times 0.334 \ 10^{-6}}, 0\right)$$

$$PD\_COMP\_IC4[3:0] = round \left(\frac{y_{comp\_4}}{0.4 \times 0.334 \ 10^{-6}}, 0\right)$$

$$PD\_COMP\_IC5[3:0] = round \left(\frac{y_{comp\_5}}{0.4 \times 0.180 \ 10^{-6}}, 0\right)$$

For the calculation example, this means:

PD\_COMP\_IC1[3:0] = 9dec PD\_COMP\_IC2[3:0] = 14dec PD\_COMP\_IC3[3:0] = 7dec PD\_COMP\_IC4[3:0] = 5dec PD\_COMP\_IC5[3:0] = 3dec

Datasheet

These values can be written inside the corresponding registers, see section 9.4. When the PD compensation is enabled (EN PDCOMP = "1"), the compensation will modulate the LED current of the ActiveLight channels.

Figure 4: Example of a compensation curve  $I_{COMP}$  for  $I_{C_5}=0$ . The dc-currents of the corner points are fixed in the design and cannot be influenced. The compensation components  $I_{C_1}...I_{C_5}$  are defined by the registers DC\_COMP\_IC1...5 with 4 bits each. The resulting compensation characteristics are shown in the black graph.

## 9.1.3. Ambient Light Sensor

### 9.1.3.1. Normal Operation

The ambient light detection system of the MLX75030 consists of two independent channels C and D and an on-chip controllable dedicated ground pin GNDAMB. GNDAMB should not be directly connected to GND. An external photodiode is connected in between each channel and GNDAMB.

The ambient light signal is low pass filtered on chip.

The signal of a 1ms switched-capacitor filters is sampled by the ADC (on request by an SPI command, each 2.5ms), where it is converted into a 16bit digital word.

The total input stage, this means from the external diode up to the 1ms filter, has a cut-off frequency at ~160Hz. Sampling this output every 2.5ms, commanded by SPI, would make a sample rate of 400Hz, which well above the Nyquist frequency of the present frequency content of 160Hz.

Within the specified input current range the ambient input stages bias the external photodiodes with > 0V in normal operation.

#### Datasheet

### 9.1.3.2. Calibration and temperature compensation

The output of each ambient channel has a strong temperature dependence and a slight process dependence that can be compensated at run time. This is shown in following equation (channel x, where x = C or D):

$$I_{x} = \left(1 + TC_{Iref} \Delta T\right) \left(1 + \alpha \frac{O_{x}}{300^{2}} \Delta T\right) \mathbf{e}^{\alpha \left(\frac{ambout_{x} - 2^{15}}{T}\right) + \beta}$$

(1)

- *I<sub>x</sub>*: calculated input light value

- *ambout<sub>x</sub>*: 16-bit ADC converted value of the ambient channel

- *TC<sub>Iref</sub>*: temperature coefficient of the reference current (typ. Value = +375ppm/K)

- *O<sub>x</sub>*: offset of the measurement (digital value)

- $\alpha_x$ ,  $\beta_x$ : calibration values for channel x (see below)

During calibration at least 2 light levels ( $I_{x1}$  and  $I_{x2}$ ) have to be supplied to the target ambient channel (x) with its photodiode at the same known temperature T. The closer these values are chosen to the range used in application, the more accurate the final result will be. During the setting of these light levels, the output of ambient channel x: ambout<sub>x1</sub> and ambout<sub>x2</sub> are measured. This results in 2 equations and 2 unknowns:  $\alpha_x$  and  $\beta_x$ . Both unknowns can be calculated from following formulas:

$$\alpha = \frac{T \ln\left(\frac{I_1}{I_2}\right)}{ambout_1 - ambout_2} \quad \text{and} \quad \beta = \ln\left(\frac{I_1}{1}\right) - \alpha\left(\frac{ambout_1 - 2^{15}}{T}\right) \quad (2)$$

Note that these 2 values automatically correct any gain error of the connected photodiode and used lens system.

#### Datasheet

### 9.1.3.3. Diagnostics Mode Operation

In diagnostics mode, the status of the external photodiodes is checked. The following checks are performed for each ambient light channel X where X is C or D:

- X disconnected

- GNDAMB disconnected

- X shorted to GNDA/GNDD/GNDAMB

- X shorted to VCCA/VCCD

- GNDAMB shorted to GNDA/GNDD

- GNDAMB shorted to VCCA/VCCD

- X shorted to other ambient light channel

Note that in spite of the ability to detect any error by the ambient diagnostics, an error on an ambient pin might still have other unwanted effects.

- Shorting any channel to GNDA/GNDD/GNDAMB will make the readout of the whole ambient block useless. At this time a maximum current of 14mA might be constantly pulled from the supply, independent of the amount of channels that is shorted to GNDA/GNDD/GNDAMB.

- During normal operation, node GNDAMB should be considered a ground pin. Shorting this pin to any other voltage might result in a short current of max 800mA!

- Because of such unwanted effects, a detection of an error in diagnostics mode should be followed by a disabling of the ambient channels in order to avoid disturbing the operation of other blocks in the system.

- Note that unused channels should be connected with an external resistance (~60kOhm) to GNDAMB. Doing so will avoid disturbing the other channels, but will give a constant error on the channel connected to GNDAMB.

## 9.1.4. Temperature Sensor

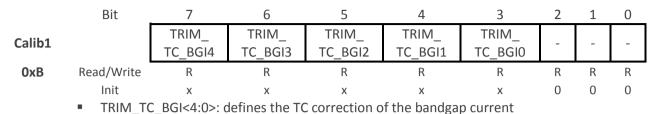

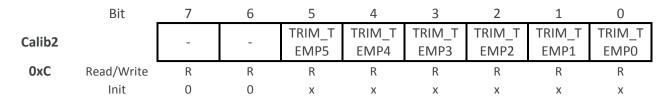

The on-chip temperature sensor measures the IC temperature. The output voltage of the sensor is converted by the 16-bit ADC. The sensor will be trimmed for the best result during the production. This trimming value is not applied to the temperature sensor internally, but is available to the customer through two on-chip registers Calib1 and Calib2, see 9.4.11. The Calib1 register contains the slope of the temperature curve in LSB/K. The Calib2 register contains the offset of the curve at a defined temperature at which the chip is tested in production.

The temperature is calculated from the temperature readout (*tempout*) and the gain and offset calibration data (calibration data measured at 30°C) according to the formula:

$$T_{K} = 303.15K + \frac{(11775 + 67(calib2 - 32)) - tempout}{67 + (calib1 - 16)}$$

K

or in °C:

$$T = 30^{\circ}\text{C} + \frac{(11775 + 67(calib2 - 32)) - tempout}{67 + (calib1 - 16)} ^{\circ}\text{C}$$

Where:

- tempout: digital temperature readout (16 Bit)

- calib1: contents of calib1 register (5 Bit)

- calib2: contents of calib2 register (6 Bit)

Datasheet

## 9.1.5. DAC

For active light sensor applications, the MLX75030 DAC has been designed to have the following features: To generate a pulse voltage signal from 1mV to 1V, so that LED current driven by LED driver can be 1mA to 1A if a 1 $\Omega$  shunt resistor is used between pins 18 and 19. After controlling and slewing circuitry, the final output voltage over external shunt resistor is like in Figure 6.

| DAC piece (2MSBs<br>B[7:6] ) | Steps each piece<br>(6LSBs B[5:0] ) | step size for<br>1 bit (V) | Range covered<br>(V) | Range start (V) | Range end (V) |

|------------------------------|-------------------------------------|----------------------------|----------------------|-----------------|---------------|

| 00                           | 64                                  | 1.00E-04                   | 6.40E-03             | 1.05E-03        | 7.35E-03      |

| 01                           | 64                                  | 5.00E-04                   | 3.20E-02             | 7.65E-03        | 3.92E-02      |

| 10                           | 64                                  | 2.50E-03                   | 1.60E-01             | 4.07E-02        | 1.98E-01      |

| 11                           | 64                                  | 1.25E-02                   | 8.00E-01             | 2.06E-01        | 9.93E-01      |

Figure 5 : Piece Wise Linear DAC voltage VS DAC codes

Figure 6: Vshunt waveform

Datasheet

## 9.1.6. LED Driver

LED driver will set the DAC voltage on external shunt resistor by a closed regulation loop.

## 9.1.7. POR

The Power On Reset (POR) is connected to voltage supply. The POR cell generates a reset signal (high level) before the supply voltage exceeds a level from 2.7V. The cell contains a hysteresis of 100mV.

Figure 7: POR sequence

## 9.2. SPI

## 9.2.1. General Description of SPI Interface

After power-on, the sensor enters a reset state (invoked by the internal power-on-reset circuit). A start-up time t<sub>startup</sub> after power-on, the internal reference voltages have become stable and a first measurement cycle can start. To indicate that the start-up phase is complete, the *DR* pin will go high (*DR* is low during the start-up phase).

The control of this sensor is completely SPI driven. For each task to be executed, the proper command must be uploaded via the SPI. The SPI uses a four-wire communication protocol. The following pins are used:

- **CS:** when CS pin is low, transmission and reception are enabled and the *MISO* pin is driven. When the CS pin goes high, the *MISO* pin is no longer driven and becomes a floating output. This makes it possible that one micro-processor takes control over multiple sensors by setting the CS pin of the appropriate sensor low while sending commands. The idle state of the chip select is high.

- **SCLK:** clock input for the sensor. The clock input must be running only during the upload of a new command or during a read-out cycle. The idle state of the clock input is high.

- **MOSI:** data input for uploading the different commands and the data that needs to be written into some registers. The idle state of the data input is low.

- MISO: data output of the sensor.

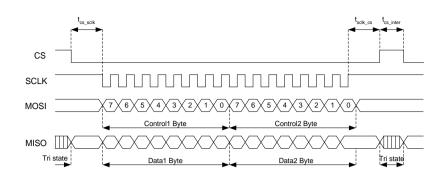

A SPI timing diagram is given in Figure 8. This is the general format for sending a command. First the *CS* pin must be set low so that the sensor can accept data. The low level on the *CS* pin in combination with the first rising clock edge is used to start an internal synchronization counter that counts the incoming bits. Data on the *MOSI* pin is clocked in at the rising clock edge. Data on the *MISO* pin is shifted out during the falling clock edge. Note that the tri-state of the *MISO* pin is controlled by the state of *CS*.

After uploading a command, the CS pin must be set high for a minimum time of  $t_{cs_{inter}}$  in order to reset the internal synchronization counter and to allow new commands to be interpreted.

Datasheet

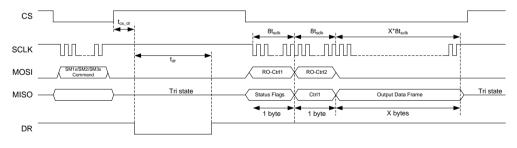

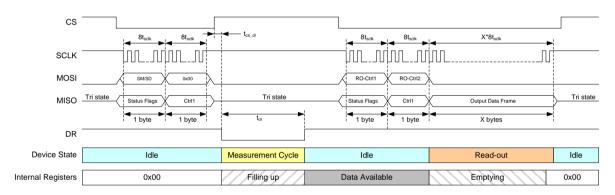

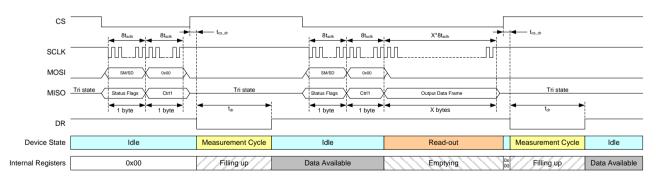

Figure 8 : SPI Timing Diagram for 2 byte instructions

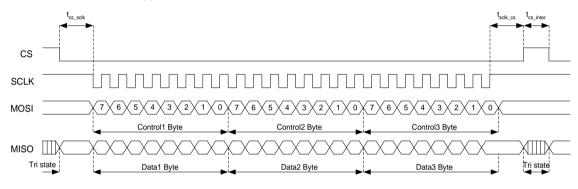

The basic structure of a command consists of 2 bytes: the Control1 Byte and the Control2 Byte that are uploaded to the device and the Data1 Byte and the Data2 Byte that are downloaded to the micro-controller. Exceptions are the commands needed to read and write the user registers (WR/RR). These commands need 3 bytes. The timing diagram is given in Figure 9.

All data transfer happens with MSB first, LSB last. Referring to Figure 8 and Figure 9 : within a byte, bit 7 is always defined as the MSB, bit 0 is the LSB. This applies to all data transfers from master to slave and vice versa.

The MSB of the Control1 Byte (bit 7) is a command token: setting this bit to 1 means that the Control1 Byte will be interpreted as a new command. If the MSB is 0, the next bits are ignored and no command will be accepted. The idle command has a Control1 Byte of 0x00. The command type (chip reset, power mode change, start measurements, start read-out, read/write register) is selected with the next bits 6..0 of the Control1 Byte.

The Control2 Byte consists of 0x00, to allow clocking out the Data2 Byte. The Data2 Byte contains always the Ctrl1 Byte that was uploaded. Thus the micro-controller can check that the Data2 Byte is an exact replica of the Ctrl1 Byte, to verify that the right command is uploaded to the device.

The Data1 Byte contains some internal status flags to allow checking the internal state of the device.

The internal status flags are defined in the table below.

See section 9.3 for more information concerning the operation of the status flags.

| Status flag | Status when bit is set                                                                                 | Status when bit is clear                         |

|-------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Bit 7 (MSB) | Previous Command was invalid                                                                           | Previous Command was valid                       |

| Bit 65      | Power State:<br>11 = (reserved)<br>10 = Normal Running Mode<br>01 = Stand-by State<br>00 = Sleep State |                                                  |

| Bit 4       | Sleep Request was sent                                                                                 | No Sleep Request available                       |

| Bit 3       | Standby Request was sent                                                                               | No Standby Request available                     |

| Bit 2       | Device is in TestMode                                                                                  | Device is not in TestMode                        |

| Bit 1       | Internal Oscillator is enabled (Standby Mode or Normal Running Mode)                                   | Internal Oscillator is shut down (Sleep<br>Mode) |

| Bit 0 (LSB) | Critical Error occurred                                                                                | No Error is detected                             |

Table 12 : Internal Status Flags as given in the Data1 Byte

Table 13 : Instruction set of the Active light sensor summarizes the instruction set of the sensor.A detailed explanation of these different commands is given in Section 9.2.2.

| Symbol | Command Description | Control1 Byte                                       | Control2 Byte                      | Control3 Byte                                                  |

|--------|---------------------|-----------------------------------------------------|------------------------------------|----------------------------------------------------------------|

| NOP    | Idle Command        | 0000 0000                                           | 0000 0000                          | N/A                                                            |

| CR     | Chip Reset          | 1111 0000                                           | 0000 0000                          | N/A                                                            |

| RSLP   | Request Sleep       | 1110 0001                                           | 0000 0000                          | N/A                                                            |

| CSLP   | Confirm Sleep       | 1010 0011                                           | 0000 0000                          | N/A                                                            |

| RSTBY  | Request Standby     | 1110 0010                                           | 0000 0000                          | N/A                                                            |

| CSTBY  | Confirm Standby     | 1010 0110                                           | 0000 0000                          | N/A                                                            |

| NRM    | Normal Running Mode | 1110 0100                                           | 0000 0000                          | N/A                                                            |

| SM     | Start Measurement   | 1101 R <sub>2</sub> R <sub>1</sub> R <sub>0</sub> T | $M_6M_3 M_2 M_1 M_0 P$             | N/A                                                            |

| SD     | Start Diagnostics   | 1011 0000                                           | $M_6M_3 M_2 M_1 M_0 P$             | N/A                                                            |

| RO     | Start Read-Out      | 1100 0011                                           | 0000 0000                          | N/A                                                            |

| WR     | Write Register      | 1000 0111                                           | D <sub>7</sub> D <sub>0</sub>      | A <sub>3</sub> A <sub>0</sub> P <sub>1</sub> P <sub>0</sub> 00 |

| RR     | Read Register       | 1000 1110                                           | A <sub>3</sub> A <sub>0</sub> 0000 | 0000 0000                                                      |

#### Table 13 : Instruction set of the Active light sensor

Besides the above instruction set, there are some test commands available for production test purposes. To prevent unintentional access into these test modes, it requires multiple commands before the actual test mode is entered.

Datasheet

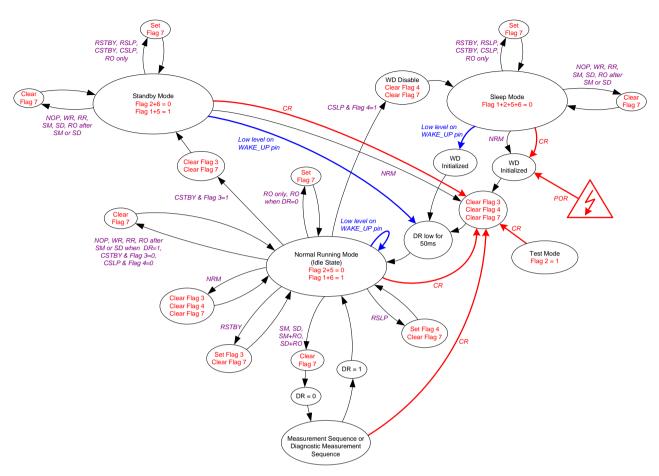

An overview of modes in which the device can operate is shown in Figure 10 : State Diagram of the MLX75030below. It also indicates which commands are available in the different operation modes.

Figure 10 : State Diagram of the MLX75030

## 9.2.2. Detailed Explanation of SPI Instruction Words

## 9.2.2.1. NOP – Idle Command

The Idle Command can be used to read back the internal status flags that appear in the Data1 Byte. The state of the device is not changed after the NOP command is uploaded.

### 9.2.2.2. CR – Chip Reset Command

After upload of a Chip Reset command, the sensor returns to a state as it is after power-up (Normal Running Mode) except for the watchdog counter, the state of the *MR* line and the contents of the 'Rst' register. The watchdog counter, the 'Rst' register and the state of the *MR* line will not be influenced by a CR command.

The CR command can be uploaded at any time, even during a measurement or a read-out cycle, provided that the internal synchronization counter is reset. This is done by setting the *CS* pin high for at least a time  $t_{cs\_inter}$ .

When a CR command is uploaded during sleep mode resp. standby mode, the device goes automatically into normal running mode. Note that this requires a time t<sub>wakeup\_slp</sub> resp. t<sub>wakeup\_stby</sub> before the internal analog circuitry is fully set up again.

Right after upload of a CR command, the *DR* pin will go low during a time t<sub>startup</sub>. Once the wake-up/reset phase is complete, the *DR* pin will go high.

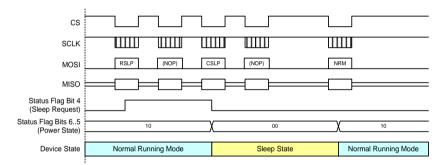

## 9.2.2.3. RSLP/CSLP – Request Sleep/Confirm Sleep

To avoid that the slave device goes unintentionally into sleep mode, the master has to upload two commands. First a RSLP (Request Sleep) shall be uploaded, then the slave sets bit 4 of the internal status flag byte high. The master has to confirm the sleep request by uploading a CSLP (Confirm Sleep). Afterwards the slave will go into Sleep Mode, hereby reducing the current consumption.

The status flag can be cleared by uploading a CR command or a NRM command. Note that uploading a Chip Reset makes the device switching into normal running mode.

When the device is operating in Sleep Mode, the WAKE\_UP pin will be monitored. A falling edge on WAKE\_UP will wake up the device and will switch it into Normal Running Mode.

When the device is operating in Sleep Mode, the *WT* pin will be monitored. If a falling edge is detected, the Critical Error flag in the Internal Status Flag Byte will be set high and the corresponding bit in the 'Err' register will be set high (refer also to Sections 9.3 and 9.4.7).

Note that no pull-up or pull-down resistor is foreseen on the  $WAKE\_UP$  pin. To avoid that parasitic spikes can wake up the device, the  $WAKE\_UP$  input is debounced (typical debounce time is in the range of 2µs). The low time on the  $WAKE\_UP$  pin should be at least a time  $t_{wu\_l}$ .

The state of the DR pin will not be changed when going into Sleep Mode. However, after a wake-up event the DR pin is set low during a time  $t_{wakeup\_slp}$ .

## 9.2.2.4. RSTBY/CSTBY - Request Standby/Confirm Standby

To put the device in Standby Mode, a similar system is used: the master shall send the RSTBY command, requesting the slave to go into Standby Mode. The slave device sets bit 3 of the internal status flag byte high, indicating that it wants to go into standby. The master has to confirm this by sending the CSTBY byte.

The status flag can be cleared by uploading a CR command or a NRM command. Uploading a Chip Reset makes the device switching into normal running mode.

When the device is operating in Standby Mode, the *WAKE\_UP* pin will be monitored. A falling edge on *WAKE\_UP* will wake up the device and will switch it into Normal Running Mode.

Note that no pull-up or pull-down resistor is foreseen on the  $WAKE\_UP$  pin. To avoid that parasitic spikes can wake up the device, the  $WAKE\_UP$  input is debounced (typical debounce time is in the range of 2µs). The low time on the  $WAKE\_UP$  pin should be at least a time  $t_{wu\_l}$ .

The state of the DR pin will not be changed when going into Standby Mode. However, after a wake-up event the DR pin is set low during a time  $t_{wakeup\_stby}$ .

## 9.2.2.5. NRM – Normal Running Mode

The NRM command shall be used to wake up the device from Sleep Mode, or to go from Standby into Normal Running Mode. This requires a time  $t_{wakeup\_slp}$  resp.  $t_{wakeup\_stby}$  before the internal analog circuitry is fully set up again. The NRM will also clear the Sleep Request or Standby Request flag.

When the NRM command is uploaded during normal running mode, the state of the device will not be influenced, except when the Sleep Request or Standby Request flag was set high due to a RSLP or RSTBY command. In this case, the Sleep Request or Standby Request flag will be cleared; the state of the DR pin will not change.

### 9.2.2.6. SM – Start Measurement

The SM command is used to start up measurement cycles. Several types of measurements can be selected with the measurement selection bits  $M_{6}$ .. $M_{0}$  in the Control2 Byte:

- M<sub>6</sub>: setting this bit high enables the temperature measurement

- M<sub>5</sub>: setting this bit high enables the read-out of the two ambient light channels

- M<sub>4</sub>: setting this bit high enables the DC light measurement in the active light channel(s)

- M<sub>3</sub>: setting this bit high fires LED A

- M<sub>2</sub>: setting this bit high fires LED B

- M<sub>1</sub>: setting this bit high enables the active light measurement in channel A

- M<sub>0</sub>: setting this bit high enables the active light measurement in channel B

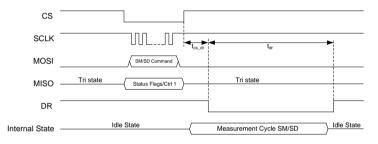

A typical timing diagram is given in Figure 11. After uploading the SM command, the measurement cycle is started as soon as the *CS* pin is set high. The ADC starts converting all the needed analog voltages and stores the digital values in registers. A time  $t_{cs\_dr}$  after *CS* is set high, the state of the *DR* pin goes low. A time  $t_{dr}$  after *DR* was set low, the state of the *DR* pin becomes high, indicating that all measurements are completed and that the resulted data is available for read-out (read-back of the stored data in the registers). This time can be up to 231.84us, if an internal autozeroing process is under execution and needs to be finished.

Table 14 : Example measurement execution times tdr gives an overview of some execution times  $t_{dr}$  for the basic types of measurements.

Datasheet

| Measurement Type                                                                                                                                                                                     | Min. t <sub>dr</sub><br>(µs) | Max. t <sub>dr</sub><br>(µs) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|

| Temperature measurement                                                                                                                                                                              | 269                          | 298                          |

| Ambient light measurements on all channels C and D                                                                                                                                                   | 388                          | 430                          |