# **General description**

The epc611 chip is a general-purpose, monolithic, fully integrated photoelectric CMOS device for optical distance measurements and object detection. Its working principle is based on 3D TOF measurement.

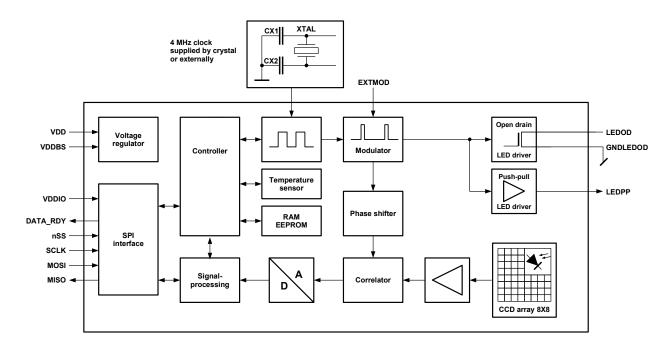

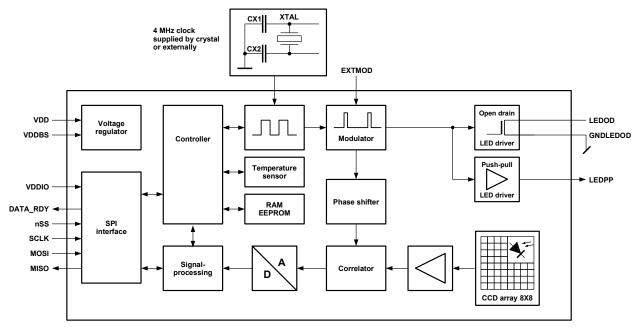

The system-on-chip (SOC) contains:

- A full data acquisition path including the modulation driver for LEDs or Laser Diodes, the photo-receiver with an 8x8 pixel TOF CCD array, the signal conditioning, the A/D converter and the basic signal processing.

- An on-chip controller managing data acquisition and data communication.

- An SPI interface for the command and data communication.

- A supply-voltage power management unit.

Various modes allow the chip to operate as a very fast one-pixel range-finder chip, as fast one-pixel range-finder chip with low distance noise, as 8x8 TOF imager chip, etc. By adding a microprocessor and few external components, a fully functional TOF range-finder or a TOF camera can be built. It measures the object distance per pixel individually and simultaneously.

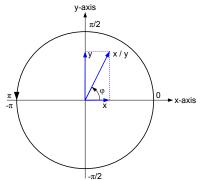

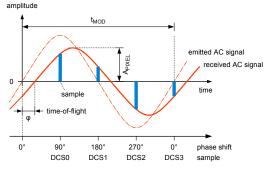

The working principle is based on the elapsed time-of-flight (TOF) of a photon (modulated light) emitted by the illumination and reflected back by the object to the photosensitive receiver. The receiver measures the phase-shift between the emitted and received signal which is proportional to the distance.

The very high photo-sensitivity allows operating range of several tens of meters and accuracy down to a centimeter depending on the lens, the illumination power and the modulation frequency.

# Features

- Operating range up to 240 m

- Resolution in the millimeter range

- On-chip high power LED or Laser Diode driver

- Easy-to-use operation in combination with a microprocessor

- Fast frame rates:

- □ 4-pixel-sum range-finder UFS mode: up to 8'000 fps

- $\hfill\square$  64-pixel-sum range-finder ULN mode: 4'000 fps

- $\hfill\square$  64-pixel imager TIM mode: up to 3'000 fps

- Output data: 12..18 bit resolution, depending on operating mode

- HDR (High-Dynamic-Range) range-finder mode

- Excellent ambient-light suppression up to 100 kLux.

- Internal or external modulation control

- Low power consumption

- Fast SPI interface for command and data transfer

- Fully SMD compatible flip-chip CSP24 package with very small footprint

# Applications

- Altimeter for drones

- Scanner for SLAM data acquisition in mobile robots

- People and object counting

- Door opening, machine controlling and safeguarding

- Volumetric mapping of objects

- Automatic vehicle guidance

- Low cost seating position detection in cars

- Gesture control (man-machine-interface)

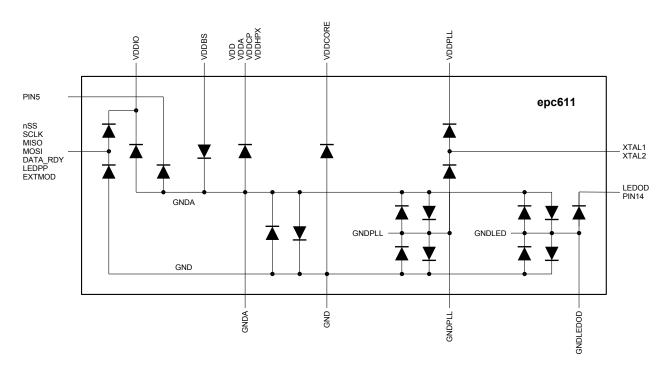

Figure 1: epc611 block diagram

# Functional block diagram

# **Table of Contents**

| 1.  | Electrical, optical and timing characteristics                                                             | 4  |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | 1.1. Operating conditions and electrical characteristics                                                   |    |

|     | 1.2. Absolute maximum ratings                                                                              |    |

|     | 1.3. Timing parameters                                                                                     |    |

|     | 1.4. Optical characteristics                                                                               |    |

|     | <ul> <li>1.5. Sensitivity</li> <li>1.6. Ambient-light suppression (ABS)</li> </ul>                         |    |

|     | 1.7. Other optical parameters                                                                              |    |

|     | 1.8. Temperature sensor characteristics                                                                    |    |

|     | 1.9. Distance measurement temperature drift                                                                |    |

| 2.  | Pin-out                                                                                                    | 8  |

|     | 2.1. Pin mapping                                                                                           |    |

|     | 2.2. Pin list                                                                                              |    |

|     | 2.3. Power domain separation and ESD protection                                                            | 9  |

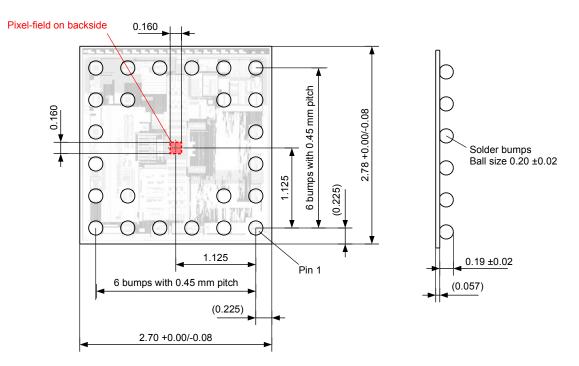

| 3.  | Packaging and layout information                                                                           | 10 |

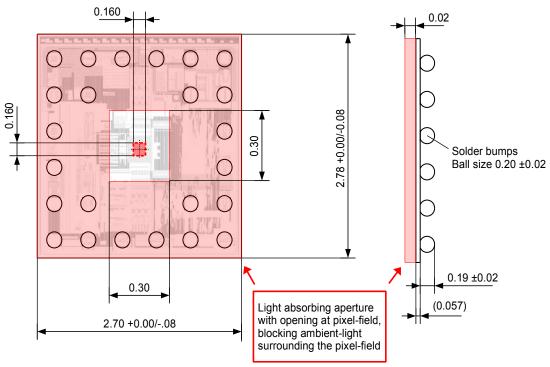

|     | 3.1. Mechanical dimensions                                                                                 |    |

|     | 3.2. Mechanical dimensions with aperture                                                                   |    |

|     | 3.3. Pin 1 marking                                                                                         |    |

|     | 3.4. PCB design and SMD manufacturing process considerations                                               |    |

|     | 3.5. Design precautions                                                                                    |    |

|     | 3.6. Tape and reel information                                                                             |    |

| 4.  | Ordering information                                                                                       |    |

| _   | 4.1. Chip version identification                                                                           |    |

| 5.  | Hardware implementation                                                                                    |    |

|     | 5.1. Block diagram                                                                                         |    |

|     | <ul><li>5.2. Typical application diagram</li><li>5.3. Application diagram part list</li></ul>              |    |

|     | 5.3. Application diagram part list                                                                         |    |

|     | 5.5. Clock sources                                                                                         |    |

|     | 5.5.1. System clock supply                                                                                 |    |

|     | 5.5.2. External modulation EXTMOD                                                                          |    |

|     | 5.6. Illumination (LED) driver                                                                             | 18 |

|     | 5.6.1. LEDOD pin                                                                                           |    |

|     | 5.6.2. LEDPP pin                                                                                           |    |

|     | 5.7. DLL (Delay line)                                                                                      |    |

|     | 5.8. Pixel-field<br>5.8.1. Pixel architecture                                                              |    |

|     | 5.8.2. Pixel-field organization and readout                                                                |    |

|     | 5.8.3. Pixel saturation detection                                                                          |    |

|     | 5.8.4. ADC conversion over- and underflow                                                                  |    |

| 6.  | Imaging                                                                                                    |    |

| ••• | 6.1. epc611 functional overview                                                                            |    |

|     | 6.2. Time-of-flight modes (TOF)                                                                            |    |

|     | 6.2.1. eTIM mode: 8x8 pixel 3D Tof IMager                                                                  | 24 |

|     | 6.2.2. ULN mode: Ultra Low Noise range-finder (sum of 8x8 pixels)                                          |    |

|     | 6.2.3. UFS mode: Ultra Fast and Sensitive range-finder (sum of 2x2 binned pixels)                          |    |

|     | 6.2.4. UHD mode: Ultra High Dynamic range-finder, low noise (8 different int. times, each sum of 8 pixels) |    |

|     | 6.3. Grayscale imager modes     6.3.1. GIM mode: 8x8 pixel Grayscale IMager                                |    |

|     | 6.3.2. GBI mode: 4x4 pixel Grayscale Binned pixel Imager                                                   |    |

|     | 6.3.3. Alternative grayscale modes                                                                         |    |

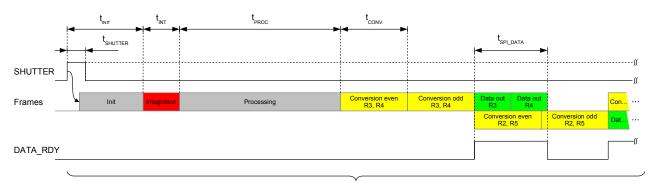

|     | 6.4. Imaging timing and frame rates                                                                        | 42 |

|     | 6.4.1. Single measurement control                                                                          | 43 |

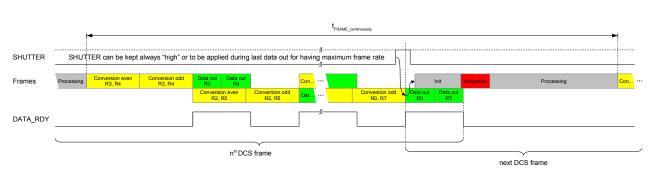

|     | 6.4.2. Continuous measurement control (auto-run)                                                           |    |

|     | 6.5. Integration time setting                                                                              |    |

|     | 6.5.1. Single integration time per frame                                                                   |    |

|     | 6.5.2. Multiple integration time per frame         6.6. Distance measurement (3D TOF)                      |    |

|     | 6.7. Distance calculation algorithm                                                                        |    |

|     | 6.8. Unambiguity range versus time base setting                                                            |    |

|     | 6.9. Quality of the measurement                                                                            |    |

|     | 6.10. Grayscale imaging / ambient-light measurement                                                        |    |

|     | 6.11. Calibration and compensation of TOF cameras                                                          |    |

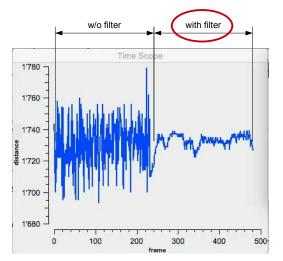

|     | 6.12. Noise reduction and signal filtering                                                                 | 49 |

| 7. | Temperature sensor                                       | 50   |

|----|----------------------------------------------------------|------|

|    | 7.1. Initialization                                      |      |

|    | 7.2. Read-out during runtime                             | . 50 |

|    | 7.3. Calculating temperature in °C                       | 51   |

| 8. | Application information                                  | 52   |

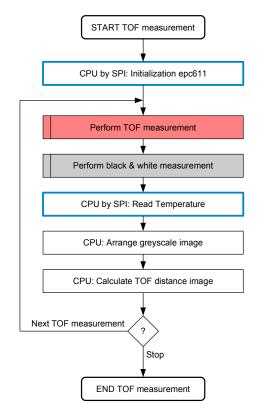

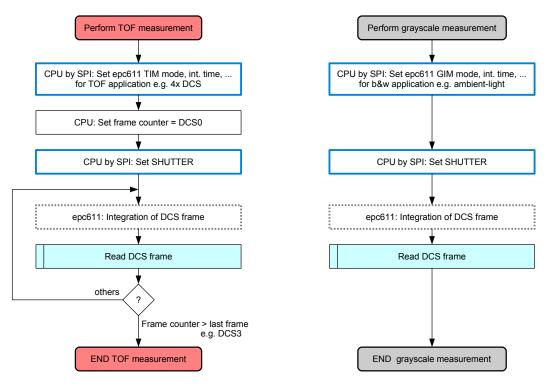

|    | 8.1. Example sequence from start-up to frame acquisition |      |

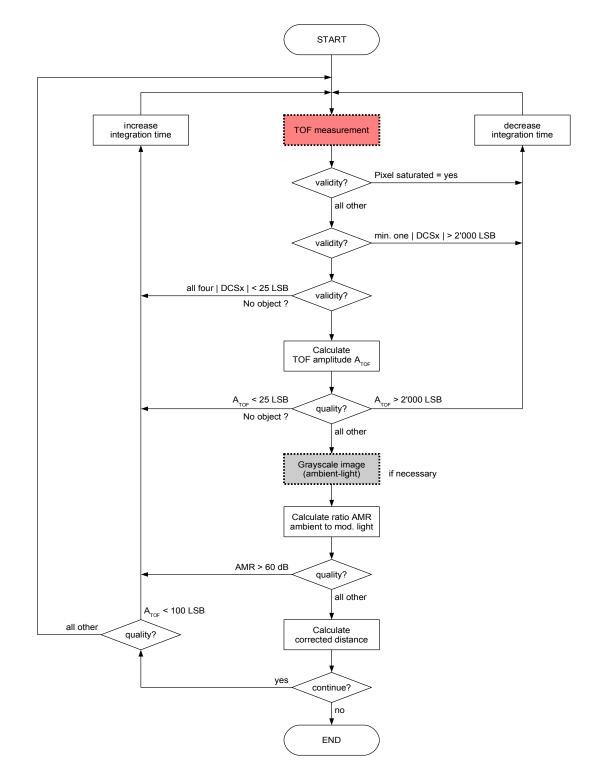

|    | 8.2. 3D TOF distance measurement flow                    |      |

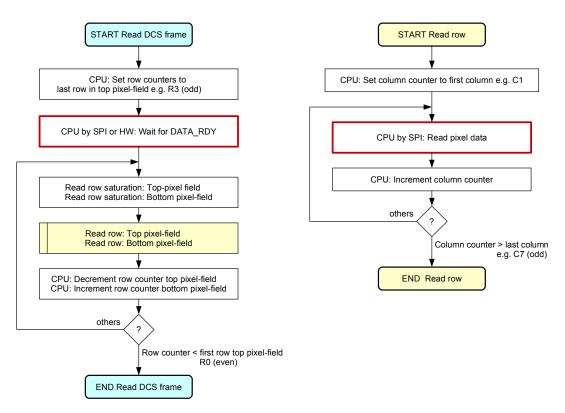

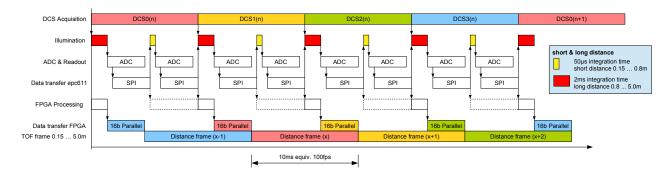

|    | 8.3. Rolling DCS frames                                  |      |

|    | 8.4. Enhanced rolling DCS frame mode                     |      |

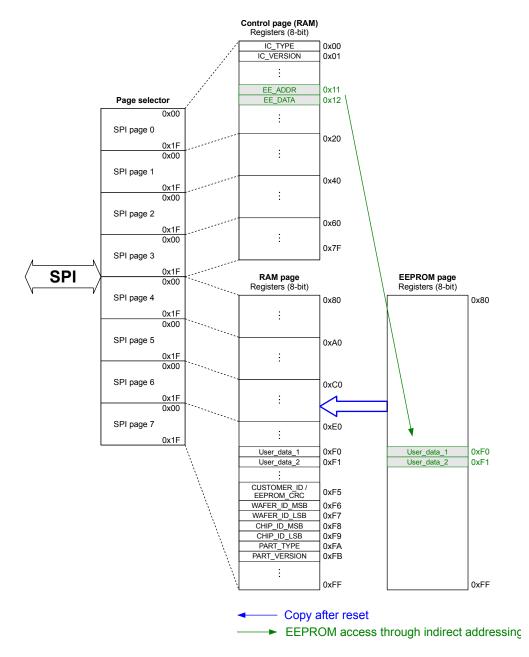

| 9. | Parameter and configuration memory                       | 55   |

|    | 9.1. Sequencer program                                   |      |

|    | 9.2. Data memory map                                     |      |

|    | 9.2.1. Control page                                      |      |

|    | 9.2.2. RAM page                                          |      |

|    | 9.2.3. EEPROM page                                       | . 56 |

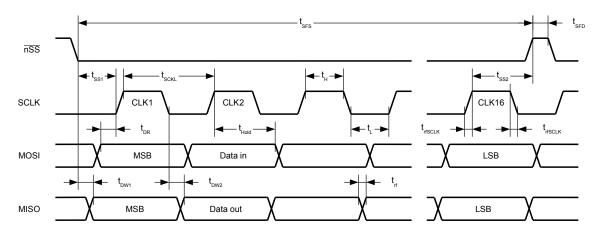

| 10 | . SPI interface                                          | 57   |

|    | 10.1. SPI timing                                         |      |

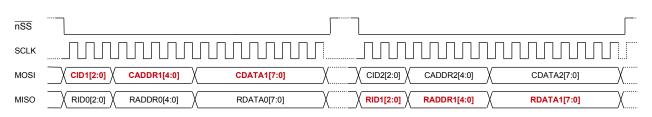

|    | 10.2. SPI frame format                                   |      |

|    | 10.3. SPI commands                                       |      |

|    | 10.4. SPI response                                       | . 59 |

|    | 10.5. SPI pixel data readout and DATA_RDY                | . 60 |

| 11 | . Register map                                           | 61   |

|    | 11.1. SPI Page 0                                         |      |

|    | 11.2. SPI Page 1                                         |      |

|    | 11.3. SPI Page 2                                         |      |

|    | 11.4. SPI Page 3                                         | . 63 |

|    | 11.5. SPI Page 4                                         | 63   |

|    | 11.6. SPI Page 5                                         | . 65 |

|    | 11.7. SPI Page 6                                         | . 65 |

|    | 11.8. SPI Page 7                                         | . 66 |

| 12 | . Control command examples                               | 67   |

|    | 12.1. Reading part version                               |      |

|    | 12.2. Reading IC version                                 |      |

|    | 12.3. Reading WAFER ID and CHIP ID                       |      |

|    | 12.4. Writing to EEPROM                                  |      |

|    | 12.5. Reading from EEPROM                                |      |

|    | 12.6. Latest version of the sequencer program            |      |

| 13 | . Addendum                                               |      |

|    | 13.1. Terms, definitions and abbreviations               |      |

|    | 13.2. Related documents                                  |      |

| 14 |                                                          |      |

| 14 |                                                          | 11   |

# 1. Electrical, optical and timing characteristics

All characteristics are at typical operational ratings,  $T_A = +25^{\circ}C$ , modulation frequency 10MHz, unless otherwise stated.

| Parameter                | Description                                                | Conditions/Comments                                                  | Vsc               | Min.                    | Тур.       | Max.                    | Units  |

|--------------------------|------------------------------------------------------------|----------------------------------------------------------------------|-------------------|-------------------------|------------|-------------------------|--------|

| V <sub>DD</sub>          | Main supply voltage                                        | Ripple <sup>1</sup> < ±100 mV                                        | V <sub>DD</sub>   | 8.0                     | 8.5        | 9.0                     | V      |

| V <sub>DDIO</sub>        | IO supply voltage                                          | Ripple <sup>1</sup> < ±50 mV                                         | V <sub>DDIO</sub> | 2.43                    | 3.3        | 5.5                     | V      |

| V <sub>DDBS</sub>        | Bias supply voltage                                        | Ripple <sup>1</sup> < ±50 mV                                         | V <sub>DDBS</sub> | -11.5                   | -11        | -10.5                   | V      |

| I <sub>VDD-Average</sub> | Average main supply current                                | @ nominal voltage                                                    |                   |                         | 18         |                         | mA     |

| IVDDIO-Average           | Average IO supply current                                  | @ 3.3 V                                                              |                   |                         | 100        |                         | μA     |

|                          | Bias supply current <sup>2</sup>                           |                                                                      |                   |                         | 0.1        | 2.0                     | mA     |

| V <sub>ON_LEDOD</sub>    | LEDOD on-voltage forward voltage (refer to Chapter 5.6.1.) | @ I <sub>LEDOD-ON</sub> = 100 mA<br>@ I <sub>LEDOD-ON</sub> = 200 mA |                   |                         | 0.1<br>0.2 |                         | V<br>V |

| I <sub>OFF_LEDOD</sub>   | LEDOD leakage current                                      | @ LEDOD off-voltage                                                  |                   |                         |            | 10                      | μA     |

| V <sub>IH_VDDIO</sub>    | Digital high level input voltage                           | Excluding XTALIN                                                     | V <sub>DDIO</sub> | 0.7xV <sub>DDIO</sub>   |            |                         | V      |

| VIL_VDDIO                | Digital low level input voltage                            | Excluding XTALIN                                                     |                   |                         |            | 0.3xV <sub>DDIO</sub>   | V      |

| V <sub>IH_XTALIN</sub>   | Digital high level input voltage                           | XTALIN                                                               | +1.8V             | 1.35                    |            |                         | V      |

| VIL_XTALIN               | Digital low level input voltage                            | XTALIN                                                               |                   |                         |            | 0.2                     | V      |

|                          | Digital high level input current                           | V <sub>IH</sub> max.                                                 |                   |                         |            | 10.0                    | μA     |

|                          | Digital low level input current                            | V <sub>IL</sub> min.                                                 |                   | -10                     |            |                         | μA     |

| CIn_VDDIO                | Digital input capacitance                                  |                                                                      |                   |                         |            | 3                       | pF     |

| V <sub>OH_VDDIO</sub>    | Digital high level output voltage                          |                                                                      | V <sub>DDIO</sub> | 0.8 x V <sub>DDIO</sub> |            |                         | V      |

| V <sub>OL_VDDIO</sub>    | Digital low level output voltage                           |                                                                      |                   |                         |            | 0.2 x V <sub>DDIO</sub> | V      |

|                          | Digital high level output current                          | Push-pull pin LEDPP only                                             |                   |                         |            | 50                      | mA     |

|                          | Digital low level output current                           |                                                                      |                   | -50                     |            |                         | mA     |

| C <sub>Out_VDDIO</sub>   | Digital output load capacitance                            |                                                                      |                   |                         |            | 20                      | pF     |

| P <sub>Avarage</sub>     | Power dissipation (average)                                |                                                                      |                   |                         | 155        |                         | mW     |

| R <sub>Th</sub>          | Thermal resistance                                         | on PCB with underfill                                                |                   |                         | 65         |                         | °K/W   |

| T <sub>OP</sub>          | Operating temperature                                      |                                                                      |                   | -40                     |            | 105                     | °C     |

# 1.1. Operating conditions and electrical characteristics

Notes:

1

Min. and Max. voltage values include noise and ripple voltages.

<sup>2</sup> Value 0.1 mA is for a camera with lens and a bright illuminated white target. Goes up for strong illumination (approx. 550 μW/mm<sup>2</sup>, no lens) up to typ. 2 mA.

## 1.2. Absolute maximum ratings

| Parameter                                                                                                      | Conditions                                                                                          |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Main supply voltage V <sub>DD</sub>                                                                            | -0.5 +9.5 V                                                                                         |

| IO supply voltage V <sub>DDIO</sub>                                                                            | -0.5 +5.5 V                                                                                         |

| Bias supply voltage V <sub>DDBS</sub>                                                                          | -12.0 +0.5 V                                                                                        |

| Voltage to any pin in the same $V_{sc}$ supply class. Refer to Figure 4 and Table 9.                           | $V_{\text{SC}}$ min - 0.3 V … $V_{\text{SC}}$ max + 0.3 V                                           |

| LED sink current $I_{\text{ON}\_\text{LED}}$ (modulated peak current, refer to Figure 16 and Chapter 5.6.1.)^1 | 400 mA @T <sub>J</sub> 85°C<br>25 mA @T <sub>J</sub> 125°C<br>linear reduction between 85 and 125°C |

| LED off-voltage V <sub>OFF_LED</sub> (open-drain output)                                                       | 7.5 V                                                                                               |

| ESD rating                                                                                                     | JEDEC HBM class 1C (1kV to < 2kV)                                                                   |

| Junction temperature (T <sub>j</sub> )                                                                         | -40°C to +125°C                                                                                     |

| Relative humidity                                                                                              | 0 95%, non-condensing                                                                               |

Notes:

Table 2: Absolute maximum rating

The overall ON/OFF time of the LED during the measurement cycle shall not exceed a 28% duty-cycle. Refer to  $t_{INT}$  and  $t_{FRAME}$  of Figure 40 and Figure 41. The duty-cycle of the modulation signal itself is always 1:1 resp. 50%.

# 1.3. Timing parameters

| Parameter                   | Description                                        | Conditions                                                                                                                         | Min.  | Тур. | Max.  | Units |

|-----------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| t <sub>startup</sub>        | Start-up time or RESET                             | After applying external supplies                                                                                                   |       | 340  | 1'000 | μs    |

| t <sub>RESET</sub>          | RESET                                              |                                                                                                                                    |       | 340  |       | μs    |

| $t_{\text{EEPROM}_{Write}}$ | Write EEPROM                                       | Waiting time per byte                                                                                                              |       |      | 25    | ms    |

| t <sub>DLL</sub>            | DLL delay for 1 step                               | Approx. 30 cm distance shift per step. Refer for details to register P3[0x13] and Figure 18, for exact value to register P6[0x1A]. |       | 2.1  |       | ns    |

| f <sub>XTAL</sub>           | Clock frequency                                    | Crystal (or ceramic resonator)                                                                                                     |       | 4    |       | MHz   |

| $df_{\text{XTAL}}$          | Clock frequency deviation                          | Any deviation is added as a linear distance error                                                                                  |       |      | ±100  | ppm   |

| f <sub>JITTER</sub>         | Clock frequency phase jitter                       | Peak-to-peak, cycle to cycle                                                                                                       |       |      | 50    | ps    |

| f <sub>LED</sub>            | LED modulation frequency                           |                                                                                                                                    | 0.625 |      | 20    | MHz   |

| <b>f</b> <sub>EXTMOD</sub>  | Ext. modulation clock                              | Refer to Chapter 5.5.2                                                                                                             |       |      | 80    | MHz   |

| t <sub>LED_rise/fall</sub>  | Required rise/fall time of the illumination LED/LD | @ 50 ohm load<br>Note: Use VCSELs or high-speed LEDs with<br>short switching times e.g. Osram SFH4059, etc.                        |       |      | 12    | ns    |

| f <sub>SCLK</sub>           | SPI clock frequency                                |                                                                                                                                    |       |      | 16    | MHz   |

| t <sub>H</sub> / t∟         | SCLK HIGH / LOW period                             |                                                                                                                                    | 15    |      |       | ns    |

Table 3: Timing parameters

# 1.4. Optical characteristics

Typ. operational ratings,  $T_A = +25^{\circ}C$ , unless otherwise stated.

| Parameter           | Description               | Conditions/Comments | Min. | Тур.      | Max. | Units |

|---------------------|---------------------------|---------------------|------|-----------|------|-------|

| A <sub>PIXEL</sub>  | Pixel photosensitive area | 100% fill factor    |      | 20x20     |      | μm    |

| A <sub>SENSOR</sub> | Pixel-field area          | 8x8 pixel           |      | 0.16x0.16 |      | mm    |

Table 4: Optical characteristics

# 1.5. Sensitivity

@ integration time 100 µs

| Parameter               | Description                                |       | Min. | Тур. | Max. | Units                           |

|-------------------------|--------------------------------------------|-------|------|------|------|---------------------------------|

|                         | Modulation frequency 12MHz                 | 640nm | 0.75 | 0.9  | 1.05 |                                 |

| TOF sensitivity STOF    | Amplitude 1,400 LSB                        | 850nm | 0.50 | 0.6  | 0.70 | <u>nW/mm<sup>2</sup></u><br>LSB |

|                         |                                            | 940nm | 0.65 | 0.8  | 0.95 |                                 |

| TOF <sub>SENS</sub> FPN | Sensitivity fix pattern noise, @ 1,400 LSB |       |      | 40   | 100  | LSB                             |

| TOF <sub>DIST</sub> FPN | Distance fix pattern noise, @ 1,400 LSB    |       |      | 18   | 50   | mm                              |

| I <sub>Dark</sub>       | Dark current (drift during readout)        |       |      | 5    | 20   | LSB/ms                          |

|                         | Normal operation                           |       | 0.19 | 0.25 | 0.31 | nW/mm <sup>2</sup>              |

| Grayscale sensitivity   | Temperature sensing mode                   |       | 0.48 | 0.62 | 0.76 | LSB                             |

| H <sub>v</sub>          | Optical sensitivity                        |       |      | 150k |      | LSB<br>Lux/sec                  |

| GS <sub>STD</sub>       | Grayscale standard deviation               |       |      | 25   | 100  | LSB                             |

Table 5: Sensitivity

#### 1.6. Ambient-light suppression (ABS)

An important function of the 3D TOF pixel is the ambient-light suppression. It removes DC or low frequency modulated light caused by sunlight, room illumination, etc. from the modulated light generated by the camera illumination. The amount of collected ambient light is proportional to the integration time. The longer the integration time, the more unwanted light will be collected. It's a good practice to keep the integration time for TOF imaging below 1ms. In addition, optical bandpass filters to block the unwanted light spectrum is mandatory.

| Parameter      | Ambient light suppression | Integration<br>time | Wavelengt<br>h | Min. | Тур. | Max. | Units              |

|----------------|---------------------------|---------------------|----------------|------|------|------|--------------------|

| E <sub>e</sub> | Irradiance, DC light      | 100 µs              | 640nm          | 0.30 |      |      | mW/mm <sup>2</sup> |

|                |                           |                     | 850nm          | 0.20 |      |      |                    |

|                |                           |                     | 940nm          | 0.25 |      |      |                    |

| Parameter | Ambient light suppression      | Integration<br>time | Center<br>wavelength | Bandwidth | Min. | Тур. | Max. | Units |

|-----------|--------------------------------|---------------------|----------------------|-----------|------|------|------|-------|

| E         | Luminance equivalent, sunlight | 500µs               | 640nm                | ±27.5nm   | 85   |      |      | kLux  |

|           |                                |                     | 850nm                | ±32.5nm   | 70   |      |      |       |

|           |                                |                     | 940nm                | ±30nm     | 190  |      |      |       |

Table 6: Ambient light suppression

Note:

The default and suggested chip configuration is set to achieve highest possible frame rate and using additional ambient-light correction according the Application note AN10 Calibration and compensation: Register P4[0x10], bit 3 = 0 and P5[0x0B] = 0x00. A 20% more efficient ambient-light suppression is possible, if the following registers are modified:

P4[0x10], bit 3 = 1 P5[0x0B] = 0x01

It turns the LED modulation before each integration for additional  $40\mu s$  @ 20MHz modulation frequency on. This modulation is independent of the effective integration time. The on-time depends on the modulation frequency by  $t_{oN} = 40\mu s * 20$ MHz / modulation frequency.

#### 1.7. Other optical parameters

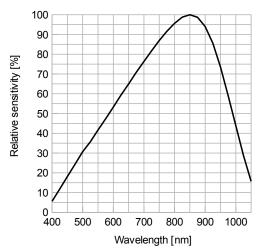

Figure 2: Relative spectral sensitivity (S $_{\lambda}$ ) vs. wavelength

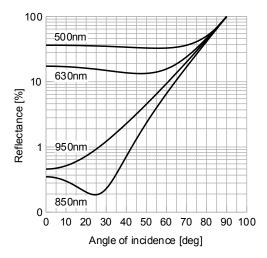

Figure 3: Reflectance vs. illumination angle (AOI)

# 1.8. Temperature sensor characteristics

| Parameter         | Description             | Conditions             | Min. | Тур.  | Max. | Units |

|-------------------|-------------------------|------------------------|------|-------|------|-------|

| T <sub>TEMP</sub> | Measurement range       |                        | -40  |       | +105 | °C    |

| P <sub>TEMP</sub> | Sensor resolution       |                        |      | 14    |      | bit   |

| k                 | Temperature sensor gain |                        |      | 0.134 |      | K/LSB |

| Lin               | Linearity               | Over temperature range |      | 5     |      | %     |

| T                 | Calibration temperature |                        | 26.5 | 27.0  | 27.5 | °C    |

Table 7: Temperature sensor characteristics

Note: Refer also to Chapter 7.

# 1.9. Distance measurement temperature drift

| @10MHz mo          | dulation frequency   |      |      |      |       |

|--------------------|----------------------|------|------|------|-------|

| Parameter          | Description          | Min. | Тур. | Max. | Units |

| ТС <sub>РІХ</sub>  | Pixel                |      | 11.3 |      | mm/K  |

| TC <sub>OD</sub>   | LED/LD driver        |      | 2.7  |      | mm/K  |

| TC <sub>DLLn</sub> | DLL stage, per stage |      | 0.65 |      | mm/K  |

Table 8: Optical characteristics

Note: Values vary from imager to imager. Refer for details to Figure 19 and application note AN10 Calibration and Compensation, chapter temperature compensation.

# 2. Pin-out

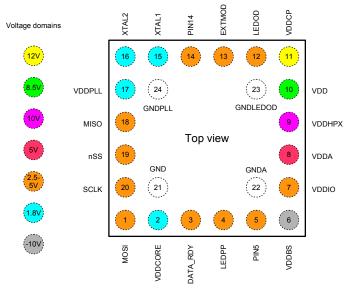

2.1. Pin mapping

Figure 4: Pin mapping (top view, solder balls are bottom-side, pixel-field is top-side)

| Pin No.   | Pin name           | Supply class V <sub>sc</sub> | Pin type | Rst level       | Description                                                       |

|-----------|--------------------|------------------------------|----------|-----------------|-------------------------------------------------------------------|

| l/O pins  |                    |                              |          |                 |                                                                   |

| 19        | nSS                | V <sub>DDIO</sub>            | DI       | V <sub>он</sub> | SPI slave selection                                               |

| 20        | SCLK               | V <sub>DDIO</sub>            | DI       | Vol             | SPI slave clock                                                   |

| 1         | MOSI               | V <sub>DDIO</sub>            | DI       | V <sub>OL</sub> | SPI slave data input                                              |

| 18        | MISO               | V <sub>DDIO</sub>            | DO       | V <sub>OL</sub> | SPI slave data output                                             |

| 3         | DATA_RDY           | V <sub>DDIO</sub>            | DIO      | V <sub>OL</sub> | Data ready notifier, no pull-up or pull-down resistor on this pin |

| 4         | LEDPP <sup>1</sup> | V <sub>DDIO</sub>            | DIO      | Vol             | LED push/pull output                                              |

| 13        | EXTMOD             | V <sub>DDIO</sub>            | DIO      | V <sub>OL</sub> | Modulator/demodulator external clock input                        |

| Analog pi | ns                 |                              |          |                 |                                                                   |

| 15        | XTAL1              | V <sub>DDPLL</sub>           | AI       |                 | Oscillator clock input for crystal, resonator or digital clock    |

| 16        | XTAL2              | V <sub>DDPLL</sub>           | AO       |                 | Oscillator output to crystal or resonator                         |

| 12        | LEDOD <sup>1</sup> | V <sub>DDLEDOD</sub>         | AOD      |                 | LED open-drain output                                             |

| 14        | PIN14              | V <sub>DDIO</sub>            | AI       |                 | Connect this pin to GND                                           |

| 5         | PIN5               | V <sub>DDA</sub>             | AOI      |                 | Test pad (suggested), no connection                               |

| Supply pi | ns                 |                              |          |                 |                                                                   |

| 10        | VDD                | V <sub>DD</sub>              | PWR      |                 | Main supply voltage +8.5V                                         |

| 6         | VDDBS              | V <sub>DDBS</sub>            | PWR      |                 | Bias supply voltage -10V                                          |

| 7         | VDDIO              | V <sub>DDIO</sub>            | PWR      |                 | Digital IO supply voltage                                         |

| 11        | VDDCP              | V <sub>DDCP</sub>            | PWR      |                 | Internally generated analog supply voltage +12V                   |

| 9         | VDDHPX             | V <sub>DDPXH</sub>           | PWR      |                 | Internally generated analog supply voltage +10V                   |

| 8         | VDDA               | V <sub>DDA</sub>             | PWR      |                 | Internally generated analog supply voltage +5V                    |

| 2         | VDDCORE            | V <sub>DDC</sub>             | PWR      |                 | Internally generated digital supply voltage +1.8V                 |

| 17        | VDDPLL             | V <sub>DDPLL</sub>           | PWR      |                 | Internally generated digital supply voltage +1.8V                 |

| 22        | GNDA               | V <sub>SSA</sub>             | GND      |                 | Analog ground                                                     |

| 23        | GNDLEDOD           | V <sub>SSLEDOD</sub>         | GND      |                 | LED driver ground                                                 |

| 21        | GND                | V <sub>SSIO</sub>            | GND      |                 | Digital ground                                                    |

| 24        | GNDPLL             | VVDDPLL                      | GND      |                 | PLL ground                                                        |

Notes:

<sup>1</sup> LEDPP and LEDOD should not be used at the same time to drive LEDs on the PCB because they exhibit different phase delays.

"Pin type" in Table 9 defines the following:

- DI: Digital input

- DO: Digital output

- DIO: Digital input/output (bidirectional)

- Al: Analog input

- AO: Analog output

- AOD: Analog output, open-drain

- PWR: Supply

"Rst. Level' in Table 9 defines the level of the IO pins during/after reset.

# 2.3. Power domain separation and ESD protection

The epc611 chip has 9 different power domains and 4 ground references internally, which are interconnected with ESD protection diodes. All pins are also equipped with ESD protection diodes. The diodes have a breakthrough voltage of 0.3V. The designer has to take care that none of these diodes become conductive either at power-up, power-down or during normal operation.

Figure 5: I/O pins and ESD protection diagram

# 3. Packaging and layout information

# 3.1. Mechanical dimensions

The packaging technology is chip scale packaging (CSP).

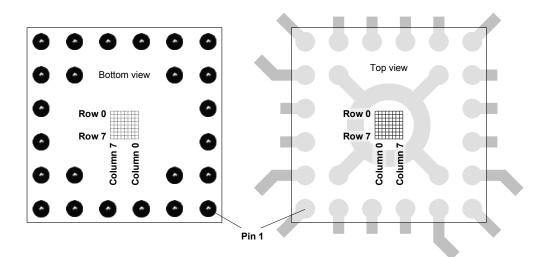

The center of the effective pixel-field (8x8) is positioned relative to the center of CSP pin 1. This point corresponds to the intersection of the middle of columns and the middle of rows when mapped to the pixel-field coordinate system on the die (see Figure 6 and Figure 7).

Figure 6: Mechanical dimensions

# Notes:

- ⊕ ⊖

- All dimensions in mm

- Not specified tolerances: ±0.001 mm

- Dimensions in brackets: Informal only

- Top side is illumination side

Figure 7: Orientation of the pixel-field (pixel order) Note: Readout is different. Refer to Figure 20.

#### 3.2. Mechanical dimensions with aperture

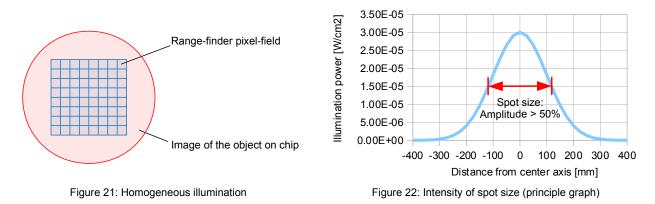

CMOS circuits are sensitive to light. That is why they can be used for photo-sensing, imaging, etc. However, if strong light is radiating the chip beside the pixel field, analog and digital circuits can be affected in its function by such parasitic light. It is called parasitic light sensi-tivity (PLS). A known effect is a shift of the measured distance under strong ambient light.

Imager lenses have always a larger field of view than the pixel-field area (refer to Figure 21). In order to prevent the chip being illuminated by strong ambient light, we print a blocking aperture on the photo-sensitive side of the imager as shown in Figure 8. The cover has an opening of 300  $\mu$ m. With regard to the 160 x160  $\mu$ m pixel-field size, this aperture has a tolerance of ±50  $\mu$ m in x and y axis. It consists of an industrial adhesive that reaches OD6 from a thickness of 9 $\mu$ m. This means that 0.0001% of the light is transmitted.

Figure 8: Mechanical dimensions for epc611 with aperture

Notes:

- •

- All dimensions in mm

- Not specified tolerances: ±0.001 mm

- Dimensions in brackets: Informal only

- Top side is photosensitive side

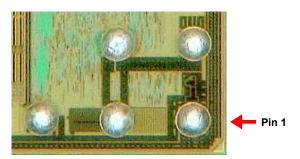

#### 3.3. Pin 1 marking

The following images show the epc611 chip from the bottom side with a view of the solder balls. Please note the location of pin 1. Please note the location of pin 1. It's highly recommended to check the pin 1 orientation with a vision system during the SMT assembly process.

epc611 chip from the solder ball side

Bottom right corner from the solder ball side

Figure 9: Pin 1 marking

Pin 1

Location of the pixel-field area

The pixel-field area is neither marked on the front nor on the backside of the IC. As a visible reference, a metal ring of the IC can be used. It is visible from the solder ball side. From the front side (photosensitive side) it can also be seen with a camera, which is sensitive in the near infrared wavelength domain (950 ... 1'150 nm).

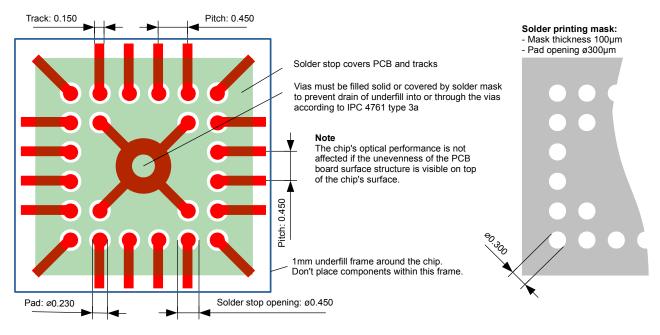

#### 3.4. PCB design and SMD manufacturing process considerations

As the epc611 chip comes in a very small 24 pin chip scale package with only 50 µm thickness, special care must be taken when making the PCB layout. In addition, careful handling during the assembly process must be ensured in order to avoid mechanical damage during the assembly process. Because the silicon chip is small and lightweight compared to the solder balls, it is highly recommended that all tracks to the chip come straight from the side. A symmetrical design is highly recommended to achieve high production yields. The pads and the tracks should also have exactly the same width, at least 1mm from the pad. They should be covered by a solder-resistant mask in order to avoid drain of the solder tin alloy onto the track.

Figure 10: Layout recommendations (dimensions in mm)

Underfill of the components reduces stress on the solder pads caused by temperature cycling, mechanical bending, etc. Furthermore, thermal and mechanical fatigue is reduced and longterm reliability increased. Underfill material and underfill selection is application specific. It should follow JEDEC-STD JEP150: Stress-Test-Driven Qualification of and Failure Mechanisms Associated with Assembled Solid State Surface-Mount Components. Please also, refer to the application note AN08 CSP Assembly Process-Rules, which can be downloaded from the ESPROS Website at www.espros.com, section Downloads. Following these recommendations will help to achieve high manufacturing yield.

**IMPORTANT:** It is strongly recommended to implement these design rules as accurate as possible into a specific PCB layout.

#### 3.5. Design precautions

The sensitivity of the sensor area is very high in order to achieve a long operating range. As a result, the epc611 device is very sensitive to EMI. Special care should be taken to keep the chip away from the signal tracks and other sources which may induce unwanted signals. To keep the noise floor low in the sensitive receiver path of the chip, a low impedance connection to the supply ground is needed. Figure 10 suggests a recommended grounding of the chip (if a ground plane is not feasible): Feed all grounds into a central via-hole with a drill diameter e.g. 0.5 ... 0.6 mm

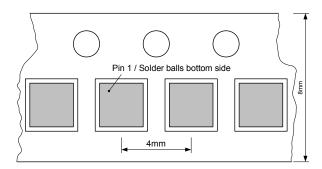

#### 3.6. Tape and reel information

The devices are packaged into embossed tapes for automatic placement systems. The tape is wound on 178 mm (7 inch) or 330 mm (13 inch) reels and individually packaged for shipment. General tape-and-reel specification data are available in a separate datasheet and indicate the tape size for various package types. Further tape-and-reel specifications can be found in the Electronic Industries Association EIA-Standard 481-1, 481-2, 481-3.

Figure 11: Tape dimensions (in mm)

ESPROS does not guarantee that there are no empty cavities in the tape. The pick-and-place machine should check for the presence of a chip during picking.

Pin 1 is marked on the bottom side of the chip, refer to Chapter 3.3..

# 4. Ordering information

| Part number | Part name                             | Package | RoHS compliance |  |  |

|-------------|---------------------------------------|---------|-----------------|--|--|

| P100 378    | epc611-CSP24                          | CSP24   | Yes             |  |  |

| P100 855    | epc611-CSP24A (with printed aperture) | CSP24   | Yes             |  |  |

Table 10: Ordering information

# 4.1. Chip version identification

■ Reading the extension -XXX of the part name on the packaging labels or delivery papers: epc611-CSP24-XXX.

■ Reading register P7[0x1B]. Refer to Chapter 11.8.

More detailed information regarding chip version as well as the latest sequencer code can be found in Chapter 12.6.

# 5. Hardware implementation

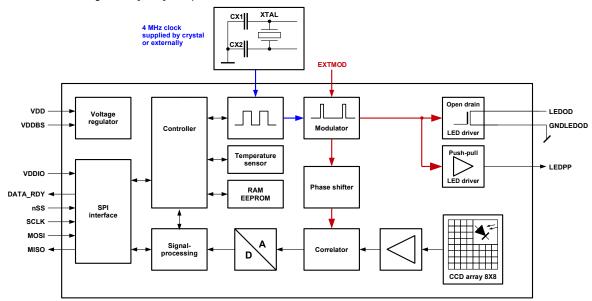

5.1. Block diagram

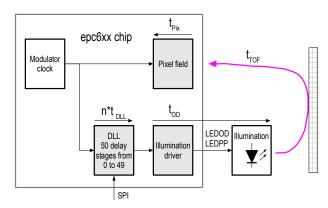

Figure 12: epc611 block diagram

Figure 12 shows the relationship between the functional blocks and the signal flow. Based on clock and mode setup, the modulation signal is generated and output over the LED driver to the external illumination (LED, VCSEL or laser diode LD). The illumination can be driven either directly by an open-drain MOS transistor (LEDOD) or digitally by the LEDPP output alternatively.

The pixel-field converts the returning IR light from the object to electrons. They are transferred depending on the phase information of the demodulation signal into two storage gates within each pixel (MGA and MGB). The AD conversion translates the phase information into a digital signal. After formatting, this is transmitted by the Serial Peripheral Interface (SPI) for external distance calculation.

All communication and/or data exchange with the epc611 occurs via the SPI interface.

The EEPROM holds default configuration and calibration data. The configuration is copied into the RAM registers during power up.

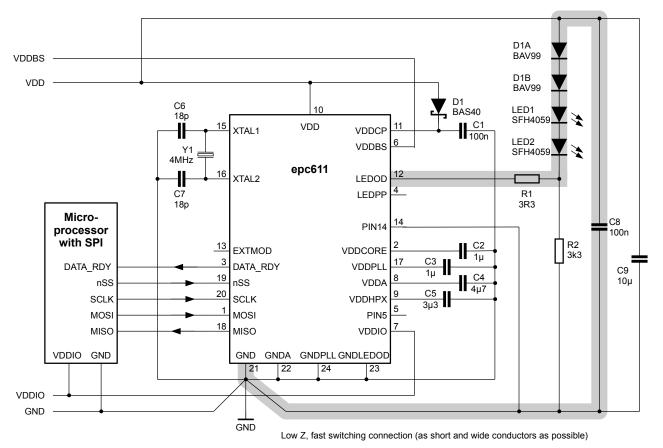

Figure 13: Typical application diagram

| Part No. | Description   | Pin No. | Value  |            |        | Tolerance | Supply class V <sub>sc</sub> | Comments           |

|----------|---------------|---------|--------|------------|--------|-----------|------------------------------|--------------------|

|          |               |         | Min.   | Тур.       | Max.   |           |                              |                    |

| C1       | VDDCP         | 11 - 22 | 18 nF  | 100 nF     | 100 nF | ±20 %     | +12 V                        | Ceramic X7R        |

| C2       | VDDCORE       | 2 - 21  | 1 µF   | 1 µF       | 3.3 µF | ±20 %     | +1.8 V                       | Ceramic X7R        |

| C3       | VDDPLL        | 17 - 24 | 1 µF   | 1 µF       | 3.3 µF | ±20 %     | +1.8 V                       | Ceramic X7R        |

| C4       | VDDA          | 8 - 22  | 3.3 µF | 4.7 μF     | 4.7 µF | ±20 %     | +5 V                         | Ceramic X7R        |

| C5       | VDDHPX        | 9 - 22  | 3.3 µF | 3.3 µF     | 4.7 µF | ±20 %     | +10 V                        | Ceramic X7R        |

| C6       | XTAL1         | 15 - 21 |        | See note 1 |        |           | +1.8 V                       | Ceramic NP0        |

| C7       | XTAL1         | 16 - 21 |        | See note 1 |        |           | +1.8 V                       | Ceramic NP0        |

| D1       | VDD and VDDCP | 10 - 11 |        |            |        |           |                              | Schottky diode     |

| X1       | XTAL          | 15 - 16 |        | 4 MHz      |        | ±100 ppm  | +1.8 V                       | Quartz / Resonator |

# 5.3. Application diagram part list

Table 11: Values of the components related to epc611 chip (Figure 13)

# Notes:

<sup>1</sup> Refer to the datasheet of the crystal or resonator manufacturer, e.g. 18 pF

<sup>2</sup> Pin PIN5: Do not make any electrical connection except on a test pad (suggested)

### 5.4. Hardware implementation notes

- 1. On our website you can download the epc611 Altium files with symbol, footprint and 3D model. Link: espros.com/downloads/01\_Chips/Altium\_Library/

- 2. epc611 is supplied with two positive (V<sub>DDIO</sub> and V<sub>DD</sub>) and one negative (V<sub>DDBS</sub>) DC voltages. Further voltages are generated on-chip.

Internally generated supplies shall be decoupled by corresponding external capacitors. Decoupling capacitors must be placed next to each supply pair in order to minimise noise and instantaneous voltage drops. Do not use these voltages to supply any other circuitry.

- 4. V\_DD is the main supply. It needs to be stable and well regulated.

- 5. V<sub>DDIO</sub> supplies the SPI interface digital I/Os. It must match the microprocessor's I/O voltage levels e.g. to 3.3 V. The supply range is according the specifications in Table 1.

- 6. V<sub>DDBS</sub> voltage biases the pixel-field such as the reverse-bias of a photodiode. The use of a stable supply source with a low ripple is required. There is no circuit dependent current consumption, except the photo-generated current (refer to Table 1, note 3).

- 7. All GND pins must have a good, powerful common connection with a minimum of noise.

- 8. The D1 Schottky diode is vital to ensure the correct power-up of the device.

- 9. Digital IO pins run up to 16 MHz and the high speed digital IO pin EXTMOD up to 80 MHz. The IO supply wires and layers need to be carefully designed and isolated so as to not introduce any noise onto the digital IO pins.

- 10. The nSS, SCLK, MOSI, and MISO signals refer to the SPI slave interface. Refer to Chapter 10.

- 11. DATA\_RDY indicates valid image data. **IMPORTANT:** It is not permitted to have any pull-up or pull-down resistor on this pin including pins of the application's CPU. The pin configuration of the application's CPU must always be set to input and never to output.

- 12. EXTMOD is an option to inject an external modulation clock.

- 13. Pin PIN5: It is not permitted to have any electrical connection except on a test pad (suggested).

- 14. It is recommended to have "not connected pins" (PINxx) available on test pads. This helps in several ways e.g. checking for correct orientation of the chip or for short-cuts after assembly.

- 15. Pins not listed here or explained later have to be connected according to Figure 13.

#### 5.5. Clock sources

#### 5.5.1. System clock supply

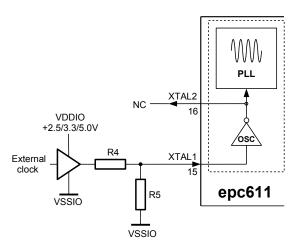

- 1. XTAL1 and XTAL2 are the input/output pins of the internal oscillator. They can be used either with a 4.0 MHz crystal or resonator. The capacitor values C6 and C7 should follow the recommendation in the datasheet of the crystal or resonator (refer to Figure 13).

- Instead of a crystal, an external 4 MHz clock source can be connected to XTAL1. XTAL2 output pin left unconnected. The input clock signal level must match V<sub>DDPLL</sub> supply level (see Table 1). If the external clock source voltage domain is above 1.8V, a resistor divider adapts it e.g. in Figure 14 and Table 12.

- 3. **IMPORTANT:** Precision and stability of the optical performance depends directly on this signal. Therefore, the external clock source must provide a clean, jitter-free and stable clock with fast rise and fall times.

Figure 14: Resistor divider to adjust clock levels to VDDPLL

| Resistor | Clock signal amplitude $V_{CLK}$ |          |          |  |  |  |  |  |  |  |

|----------|----------------------------------|----------|----------|--|--|--|--|--|--|--|

|          | 2.5 V                            | 3.3 V    | 5.0 V    |  |  |  |  |  |  |  |

| R4       | 1.0 kOhm                         | 1.0 kOhm | 2.0 kOhm |  |  |  |  |  |  |  |

| R5       | 2.2 kOhm                         | 1.2 kOhm | 1.2 kOhm |  |  |  |  |  |  |  |

Table 12: Resistor divider table

### 5.5.2. External modulation EXTMOD

The modulation clock can be supplied from an external clock source via the EXTMOD input, see Figure 15.

The external EXTMOD clock is used for example in concepts for reliable multi camera applications. It allows the use of other modulation patterns e.g. frequency-division multiple access (FDMA) or frequency hopping. These concepts are explained in detail in various relevant documents. The user is free to apply any digital waveform up to 80 MHz during frame acquisition as EXTMOD signal. The user is also free to use modulations such as pseudo-random edge jitter, dithering, etc.

The signal from the EXTMOD pin is used as input for register P4[0x05] if bit 6 in register P4[0x00] is set to 1, instead of the clock generated internally.

Refer for the effective LED modulation signal to register P4[0x05].

The unambiguity range and the integration time are in this case based on the EXTMOD:

Integration time = integration length multiplier \* (Integration length + 1) \*(1/  $f_{mod_clk}$ )

For more details refer to register P4[0x05], Chapter 6.5. and 6.8.

Figure 15: The EXTMOD signal flow (marked red)

# 5.6. Illumination (LED) driver

The chip can either directly drive laserdiodes (LD e.g. VCSELs) and LEDs (LEDOD pin) or supply the modulation signal at I/O level on LEDPP pin for driving external, more powerful illumination sources. The modulation signal is 50% duty-cycle square-wave modulated and toggles up to 20 MHz.

The register P4[0x10] allows various settings e.g. polarity (inverts both LEDOD and LEDPP pins), depending on the external LED circuit used.

#### **IMPORTANT:**

- There are certain non-modulating DC modes which keep LED driver output turned on. Users must take care to avoid any damage by not exceeding operating conditions and max. limits of components.

- LEDOD is a power driving pin. Take care of the additional on-chip heat dissipation depending on the switching current, the integration time and the frame rate. It heats up the chip additionally and causes an additional temperature drift.

- Phase stability of the illumination may suffer from temperature, aging, etc. of the components. This can result in a distance error. A corresponding compensation by the user's software is suggested.

#### 5.6.1. LEDOD pin

LEDOD is an open-drain nMOS FET driver output. This allows direct drive of illumination sources e.g. LD or LED. When the LED driver is active (ON), the LED current flows through the resistor R1 into the LEDOD pin, through the on-chip driver and comes out of the chip on the VSSLED ground pin (Figure 13).

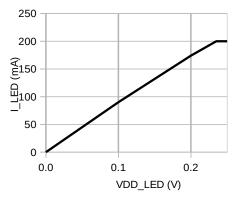

Figure 16: Typ. LEDOD output characteristics Refer for maximum values to Table 1 and Table 2

The LEDOD pin toggles up to 20 MHz, or according to the modulation clock, with a current maximum of 200 mA limited by the R1 resistor. This signal creates a lot of ground noise. Therefore, the VSSLED pin is decoupled from the other analog grounds internally. It must be shorted with the other analog ground pins using a low-ohmic connection the shortest distance possible on the PCB. This way, there will be

minimal voltage differences in the ground planes of the board. The LED supply line must be isolated properly from any analog supply on the PCB to minimize noise coupling from the LED drivers.

The number of LEDs depends on the level of the LED supply voltage and the turned-on forward voltage drop of the LEDs. The maximum voltage to the LEDOD pin is limited by the resistor R2 during LED off state.

#### 5.6.2. LEDPP pin

The LEDPP pin is the alternative push-pull driver providing symmetric rise/fall times to drive external illumination drivers. It works from the +2.5/+5.0V  $V_{DDIO}$  supply and swings in the same voltage range as the IO pins. Do not use SPI communication during integration time. LEDPP pin solely should toggle during integration time. As a result, the LEDPP signal is not affected by the switching noise of other signal lines. LEDPP = LOW (approx. 0V) corresponds to LEDOD = OFF (max. output voltage).

LEDOD and LEDPP pins must not be used at the same time for driving the external illumination. They exhibit different phase delays and this can result in incorrect distance measurements.

### 5.7. DLL (Delay line)

The modulation signal can intentionally be delayed in order to add a phase-shift between the modulation of the light source and the demodulation of the backscattered light, refer to Figure 18.

Figure 17: Block diagram of the DLL function

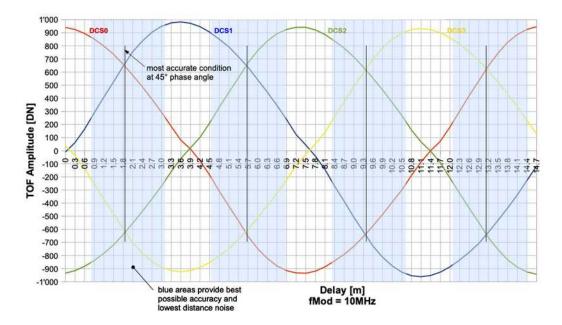

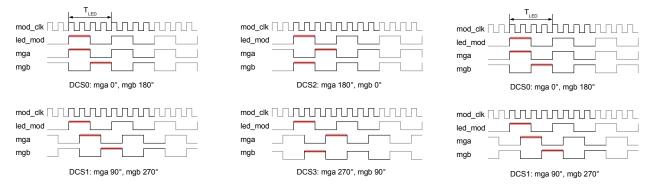

The purpose in doing this can be to ensure, the phase-shift between the modulated and the demodulated signal has a certain value in a specific distance range. For example, the highest distance accuracy with lowest distance noise can be achieved when the phase angle of demodulation is 45°. This is the case when all four DCS amplitudes have the same or a similar value. The worst situation is if one DCS pair is at its maximal amplitude whereas the other DCS pair is around zero (refer to Figure 17).

The DLL can be enabled in register P5[0x0E] whereas the delay of the LED modulation can be set in steps  $t_{\text{DLL}}$  by register P3[0x13] (approx. 2ns/step). The exact step  $t_{\text{DLL}}$  can be calculated with the value and the formula listed in register P6[0x1A]. This value varies from chip to chip and is also temperature dependent. The user must characterize the overall temperature drift of the complete camera to match the compensation.

Figure 18: DCS amplitudes for the 4 DCSx (measurement data)

**Example for 10 MHz modulation frequency:** If we want to optimize the accuracy of our TOF camera in the short range domain, e.g. 0m to 1m, the situation shown in Figure 18 is not ideal at all. The modulation frequency of the data shown in Figure 18 is 10 MHz whereas 50 DLL steps of approx. 2 ns are equivalent to 15 m distance. Shown in the diagram, the worst condition is in the first three DLL steps, which is equal to 0 ... 0.9 m. From then on, the distance accuracy improves until DLL step 12. In other words, the distance accuracy from distance 0.9 ... 3.0 m is very good, but not from 0 ... 0.9 m. In order to be within an accurate distance measurement regime, the DLL should be shifted by 3 steps which means that the LED is delayed by 6ns.

# 5.8. Pixel-field

### 5.8.1. Pixel architecture

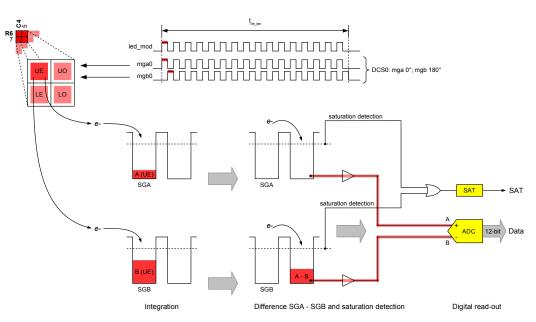

The pixels are placed in groups of 2x2 pixels (UE, UO, LE, LO), referred to hereafter as "pixel group". They are binned depending on the operating mode. The pixel performs two basic operations: Measurement (integration) and readout (A/D conversion).

This pixel group architecture allows the epc611 to operate the pixel-field in different modes and in combinations thereof, according the following chapters.

Figure 19: The 2x2 pixel group and simplified function overview

Each pixel has its own pair of storage gates, SGA and SGB. During integration, they accumulate the charges (e-) created by the modulated light reflected from the object (see Figure 24). They are controlled by the mga and mgb demodulation signals. When the integration is finished, the stored charges of SGA and SGB are read out as the difference A - B (ambient-light suppression) and converted into a single 12 bit digital value and 1 bit saturation flag. The output value can be either positive or negative, depending on the demodulated phase and the offset of the signal chain.

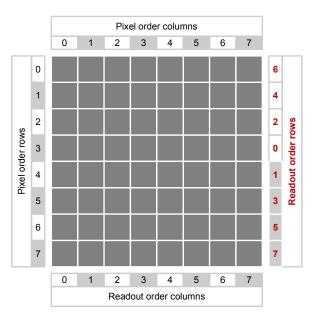

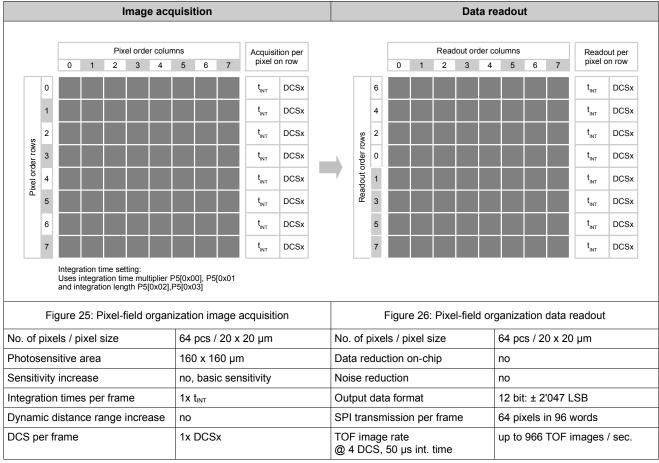

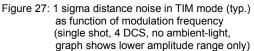

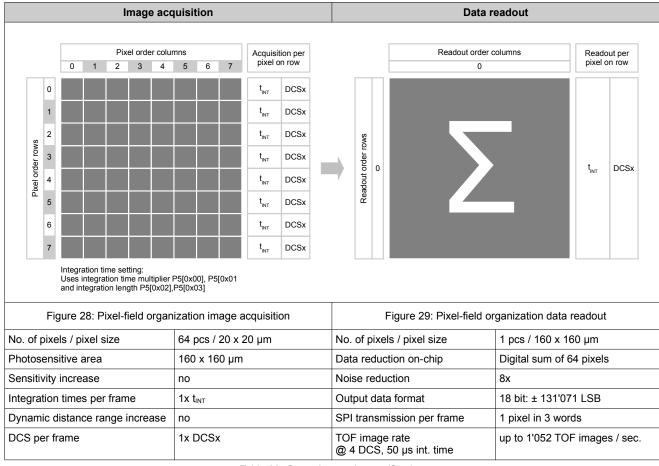

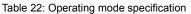

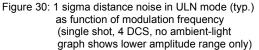

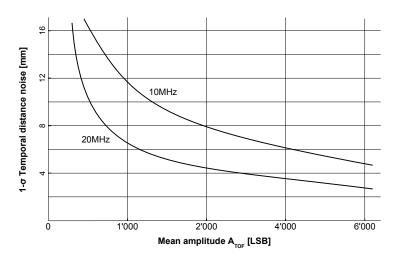

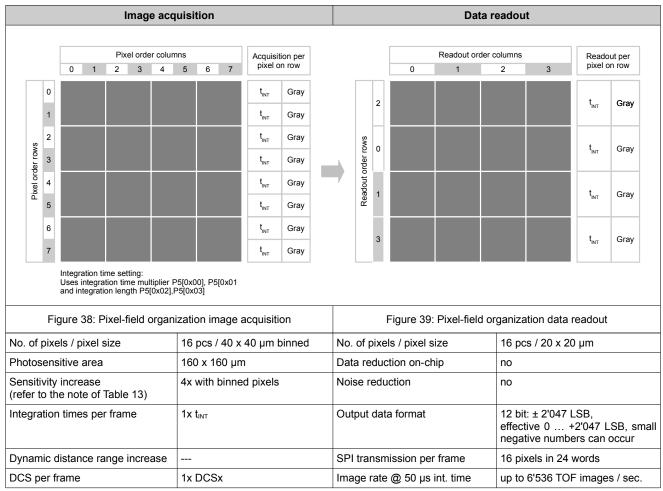

#### 5.8.2. Pixel-field organization and readout

The basic pixel-field of the epc611 is 8x8 pixels (Figure 20).

| Parameter                | Pixel       | Units        |       |

|--------------------------|-------------|--------------|-------|

|                          | Basic pixel | Binned pixel |       |

| Pixel size               | 20 x 20     | 40 x 40      | μm    |

| Pixel-field organization | 8 x 8       | 4 x 4        | Pixel |

| Sensitivity              | 1x          | approx. 4x   |       |

| Resolution               | 12          | 12           | bit   |

Table 13: Pixel-field organization

#### Figure 20: Basic pixel-field

Alternatively, enhanced range-finder features use horizontally and vertically analog binned 2x2 pixel groups, so-called "binned pixels". Refer to Table 13 and for example Figure 29. More details are listed in the descriptions of the different specific operating modes.

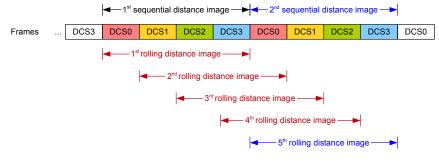

In general, the data readout of the pixel-field is vertically split in the middle into two equal parts, top and bottom. Refer to the right y-axis description in red in Figure 20. This is due to the row readout which always converts two rows at same time, one from upper half and one from bottom half of the pixel-field, starting at the centre. The readout order for the columns is from left to right.

#### 5.8.3. Pixel saturation detection

The pixels collect continuously modulated and non-modulated ambient-light during the integration period. Depending on these light intensities, sometimes the pixels collect more charge (over-exposure) than they can accommodate in their storage gates (refer to Figure 19). In such a case, the 12 bit sample data is not valid and cannot be used for distance calculation. Therefore, each pixel generates a "saturation flag" together with the sample data. It is set if one or more (in case of binned or summed pixels) are saturated. Binned pixels cannot collect more charge than a basic single pixel. The saturation flag is embedded and transmitted in the SPI data, depending on the operating mode. Refer for details to the specific mode description and Chapter 6.9.

#### 5.8.4. ADC conversion over- and underflow

If pixels are strongly illuminated, they can reach the top or bottom end of the AD converter. This will be indicated by the flags "ADC over- or underflow". Pixels, summed up on-chip, set this flag if one (or more) of the summing pixels reaches one of these limits. The flag is embedded and transmitted in the SPI data depending on the operating mode. Refer for details to the specific mode description and Chapter 6.9.

# 6. Imaging

## 6.1. epc611 functional overview

The epc611 design offers the possibility to adapt the properties of the chip to the user's target application. Instead of operating the chip as an TOF imager with 8x8 pixel, the configuration of the pixel-field can be changed to optimized, case specific, range-finder applications e.g. lowest noise, fastest speed, highest distance dynamic, no motion-blur, a mixture of these, etc. An overview is shown in Table 14 and Table 15 whereas more detailed information is available in the chapter of each specific operation mode.

| Name | Description                             | Additional features                                             |

|------|-----------------------------------------|-----------------------------------------------------------------|

| TIM  | 8x8 pixel 3D TOF Imager                 |                                                                 |

| ULN  | Ultra low noise range-finder            | Digital sum of 8x8 pixels                                       |

| UFS  | Ultra fast and sensitive range-finder   | Digital sum of 2x2 binned pixels                                |

| UHD  | Ultra high dynamic (HDR) range-finder   | Low noise, 8 different int. times, each digital sum of 8 pixels |

| GIM  | 8x8 pixel grayscale imager              |                                                                 |

| GBI  | 4x4 pixel grayscale binned pixel imager | Binned pixels                                                   |

Table 14: Basic mode overview

| Name | Frame rate <sup>2</sup>              | Sensitivity    |                 | Dynamic<br>range |                    |               |                 |

|------|--------------------------------------|----------------|-----------------|------------------|--------------------|---------------|-----------------|

|      | 1 DCS rolling                        | per pixel size | Noise reduction | max. signal      | Da                 | ata format    | Max. increase   |

| TIM  |                                      | / 20 µm        |                 |                  | 12 bit ± 2'047 LSB |               |                 |

| ULN  | ~ 1.1x                               | / 20 µm        | 8x              | 64x              | 18 bit             | ± 131'071 LSB |                 |

| UFS  | ultra fast: $\sim$ 3.2x <sup>1</sup> | 4x / 40 µm     | 2x              | 4x               | 14 bit             | ± 8'191 LSB   |                 |

| UHD  | ~ 1.1x                               | / 20 µm        | 2.8x            | 8x               | 15 bit             | ± 16'383 LSB  | ultra HDR: ≤ 8x |

Table 15: Basic features TOF modes (reference: TIM mode)

Notes:

<sup>1</sup> UFS mode uses a reduced photosensitive area 80x80 µm instead of 160x160 µm. This allows having 4x more illumination on the chip surface by using same optical emitting power with an adequately adapted receiving lens system.

<sup>2</sup> Find more details in Chapter 6.4.

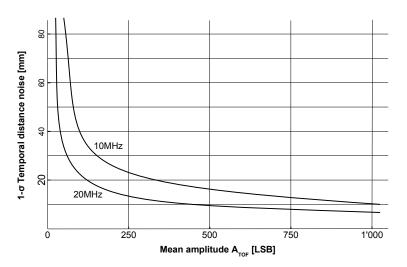

Notes on distance resolution and noise:

4 DCS mode:

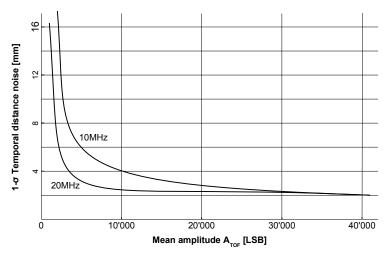

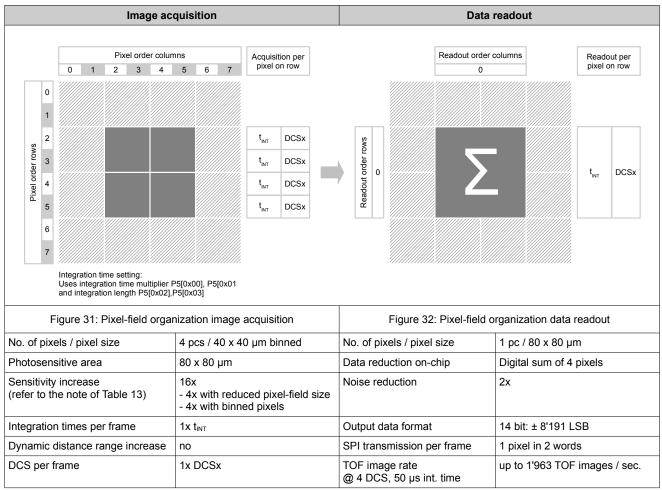

The distance resolution is the unambiguity distance divided by 8 times the current TOF amplitude (educated guess). The distance noise depends on the current TOF amplitude and decreases with increasing TOF amplitude. Refer to the graph of the corresponding operation mode e.g. Figure 28.

2 DCS mode:

Decreases distance resolution by factor 2 compared to 4 DCS mode. Increases distance noise by factor 1.4 compared to 4 DCS mode.

Data reduction:

Distance data - Take care, data reduction of data formats during distance calculation and compensation can/will increase distance noise. Recommendation: Do data reduction only at last stage of the distance calculation and compensation.

Values used in the manual for specification, unless otherwise stated: DCS data: normalized to 12 bit, signed integer TOF amplitude data: normalized to 11 bit, unsigned integer.

# 6.2. Time-of-flight modes (TOF)

The epc611 can be used in two basic time-of-flight application modes:

- Imager mode : Multipoint measurement by using the 8x8 pixel 3D TOF imager mode (TIM).

- Range-finder mode: Single point measurement. It is applicable for all the other modes.

# IMPORTANT ADVICE FOR RANGE-FINDER MODES:

- 1. Homogeneous illumination of the pixel-field

- The field of view of the entire 8x8 pixel pixel-field must be equal to or smaller than the target. Conversely, the size of the 8x8 pixel pixel-field must be smaller than the spot-size image of the object on the chip. Rule: The pixels collect all the photons in their FOV independent of target's distances and reflectivities. The distance will be calculated

Rule: The pixels collect all the photons in their FOV independent of target's distances and reflectivities. The distance will be calculated based on the collected photons (DCSx values of the pixels). The result, sum over the involved pixels, is equally to the vectorial addition of their vectors.

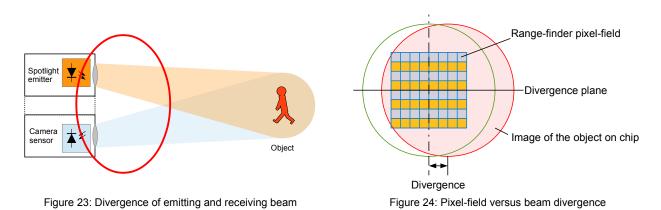

2. Orientation of the pixel-field versus the divergence of the emitting and receiving beam The plane formed by the emitting and receiving diverging beam axis must be parallel to the row axis. It reduces the influences of the intensity variations over distance, caused by divergence. The effect is usually visible due to fact that the spot on the object is not perfectly illuminated evenly.

© 2024 ESPROS Photonics Corporation Characteristics subject to change without notice

## 6.2.1. eTIM mode: 8x8 pixel 3D Tof IMager

Table 16: Operating mode specification

Operating mode selection: Depends on the number of DCS frames per SHUTTER stimulation:

|               | Register       | P1[0x02]                               | P1[0x05]                               | P4[0x12]             | P4[0x15]     |  |

|---------------|----------------|----------------------------------------|----------------------------------------|----------------------|--------------|--|

| Mode          | DCS / SHUTTER  | DCS selection<br>1 <sup>st</sup> frame | DCS selection<br>2 <sup>nd</sup> frame | Modulation selection | Readout mode |  |

| 4 DCS         | DCS 0, 1, 2, 3 | 0x34                                   | 0x3D                                   | 0x30                 |              |  |

| 2 DCS         | DCS 0, 1       | 0x34                                   | 0x3D                                   |                      |              |  |

|               | DCS 2, 3       | 0x32                                   | 0x33                                   | 0x10                 |              |  |

| 1 DCS rolling | DCS 0          | 0x34                                   |                                        |                      | 0x23         |  |

|               | DCS 1          | 0x31                                   | Netword                                | 000                  |              |  |

|               | DCS 2          | 0x32                                   | Not used                               | 0x00                 |              |  |

|               | DCS 3          | 0x33                                   |                                        |                      |              |  |

Table 17: Register settings for the operating mode selection

Integration time setting: Follow Chapter 6.5.1, Single integration time per frame.

#### Data readout: 12 bit/pixel, 64 pixel/frame with 96 SPI accesses

It starts in the centre of the vertical axis and uses a 2 pixel packed data format (pixel pair). It follows Table 18 and Table 19. The application must rearrange the pixels according the pixel-field orientation.

The readout sequence is: 3 SPI readouts / pixel pair, 4 pair readouts / row, 8 row readouts / frame = 96 SPI readouts in total.

|     | No sum readout:<br>A pair of even and odd column pixels are packed into 3 SPI data bytes. Read 3x register P2[0x0C] per pixel pair |     |      |       |      |     |     |     |                                                       |      |      |    |       |       |     |  |  |     |      |      |      |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|-----|-----|-----|-------------------------------------------------------|------|------|----|-------|-------|-----|--|--|-----|------|------|------|--|--|

|     | 1 <sup>st</sup> SPI data byte: MSByte     2 <sup>nd</sup> SPI data byte     3 <sup>rd</sup> SPI data byte: LSByte                  |     |      |       |      |     |     |     |                                                       |      |      |    |       |       |     |  |  |     |      |      |      |  |  |

| D23 | D22                                                                                                                                | D21 | D20  | D19   | D18  | D17 | D16 | D15 | D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |      |      |    |       | D0    |     |  |  |     |      |      |      |  |  |

|     |                                                                                                                                    | PIX | EL_E | VEN[1 | 1:4] |     |     | PIX | EL_E                                                  | VEN[ | 3:0] | PĽ | XEL_C | DDD[3 | :0] |  |  | PIX | EL_O | DD[1 | 1:4] |  |  |

Table 18: Pixel data SPI readout: Pixel pair read; refer to Figure 26

|                          | 1 <sup>st</sup> pair read / row | 2 <sup>nd</sup> pair read / row | 3 <sup>rd</sup> pair read / row | 4 <sup>th</sup> pair read / row |

|--------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| 1 <sup>st</sup> row read | Pixels row 3 / column 0 & 1     | Pixels row 3 / column 2 & 3     | Pixels row 3 / column 4 & 5     | Pixels row 3 / column 6 & 7     |

| 2 <sup>nd</sup> row read | Pixels row 4 / column 0 & 1     | Pixels row 4 / column 2 & 3     | Pixels row 4 / column 4 & 5     | Pixels row 4 / column 6 & 7     |

| 3 <sup>rd</sup> row read | Pixels row 2 / column 0 & 1     | Pixels row 2 / column 2 & 3     | Pixels row 2 / column 4 & 5     | Pixels row 2 / column 6 & 7     |

| 4 <sup>th</sup> row read | Pixels row 5 / column 0 & 1     | Pixels row 5 / column 2 & 3     | Pixels row 5 / column 4 & 5     | Pixels row 5 / column 6 & 7     |

|                          |                                 |                                 |                                 |                                 |

| 7 <sup>th</sup> row read | Pixels row 0 / column 0 & 1     | Pixels row 0 / column 2 & 3     | Pixels row 0 / column 4 & 5     | Pixels row 0 / column 6 & 7     |

| 8 <sup>th</sup> row read | Pixels row 7 / column 0 & 1     | Pixels row 7 / column 2 & 3     | Pixels row 7 / column 4 & 5     | Pixels row 7 / column 6 & 7     |

Table 19: Pixel-field SPI double-row readout order; refer to Figure 26, based on pixel-field coordinates Figure 25

| Validity parameter | Embedded data <sup>1</sup> | Data bit                                         |

|--------------------|----------------------------|--------------------------------------------------|

| Pixel saturation   | 0x 07 FF                   | Read register P2[0x0D] and P2[0x0E] <sup>2</sup> |

| ADC overflow       | 0x 07 FE                   | Read register P2[0x10] and P2[0x11] <sup>2</sup> |

| ADC underflow      | 0x 08 00                   | Read register P2[0x12] and P2[0x13] <sup>2</sup> |

| Valid pixel data   | 0x 08 01 < < 0x 07 FD      | [11:0]                                           |

Table 20: Data validity table

Note 1: Default is embedded data format. Can be switched off by bit 6 of the register P4[0x15]. Note 2: More details can be found in the corresponding register description.

| Action                    | Command                                                                | MOSI                                             | MISO                    | Page     | Reg          | Value | Comment                                                                                                   |

|---------------------------|------------------------------------------------------------------------|--------------------------------------------------|-------------------------|----------|--------------|-------|-----------------------------------------------------------------------------------------------------------|

|                           |                                                                        | 11001                                            |                         | 1 age    | i teg        | Fund  |                                                                                                           |

| Power up                  | NOP                                                                    | 0x 00 00                                         | 0x                      |          |              |       | After startup                                                                                             |

|                           | - repeat until IDLE:                                                   |                                                  |                         |          |              |       |                                                                                                           |

|                           | NOP                                                                    | 0x 00 00                                         | 0x 00 00                |          |              |       | IDLE; ready for communication                                                                             |

|                           | - load sequencer program                                               |                                                  |                         |          |              |       |                                                                                                           |

|                           |                                                                        |                                                  |                         |          |              |       |                                                                                                           |

| Adjust default settings 1 | Page select                                                            | 0x 81 00                                         | 0x 00 00                | 1        |              |       | Page 1                                                                                                    |

| (all chip versions)       | Adjust 1                                                               | 0x 5A 00                                         | 0x 81 00                | 1        | 0x1A         | 0x00  |                                                                                                           |