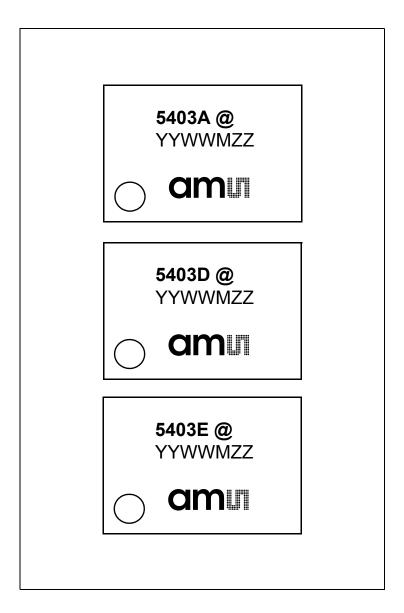

# AS5403A/D/E

## 3D Hall Position Sensor for Linear and Off-Axis Applications

## **General Description**

The AS5403 can measure magnetic fields components in all three dimensions and converts the magnetic field information into absolute position information.

Only a simple 2-pole magnet is required as the magnetic field source.

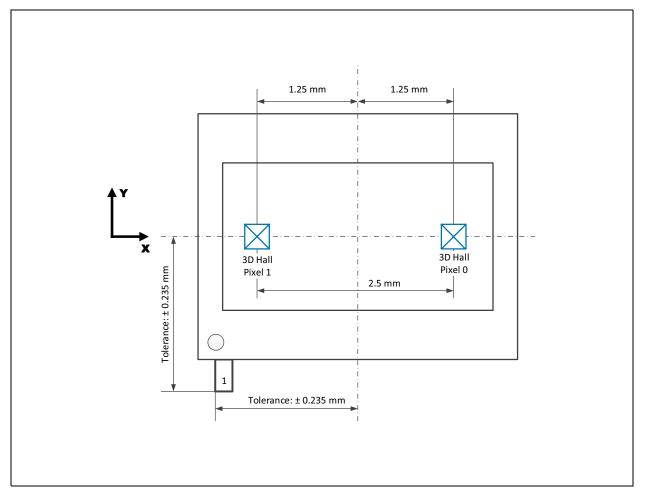

Using two 3D-Hall cells allows absolute (single pixel) as well as differential (double pixel) 3D magnetic field measurement.

The differential measurement makes the AS5403 ideal for use in rough automotive position sensing applications that include not only dust, dirt or moisture but also unwanted magnetic stray fields.

All the signal conditioning, including compensation of temperature effects as well as linearization of the output is included in the IC.

The absolute position information of the magnet is directly accessible over a SPI interface and a programmable PWM or analog output. The build in diagnostic functions makes the AS5403 suitable for safety critical applications.

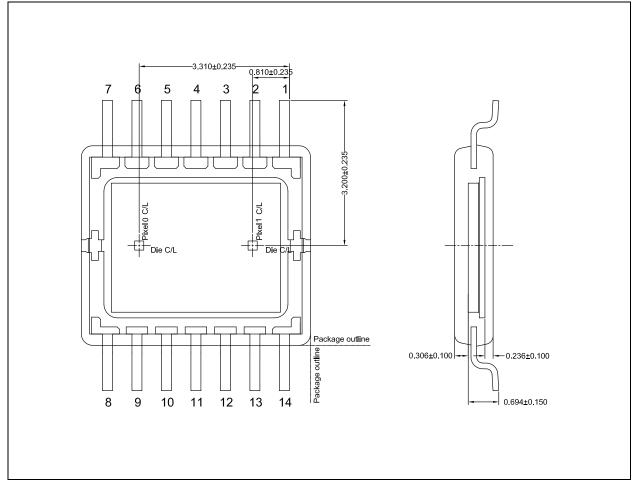

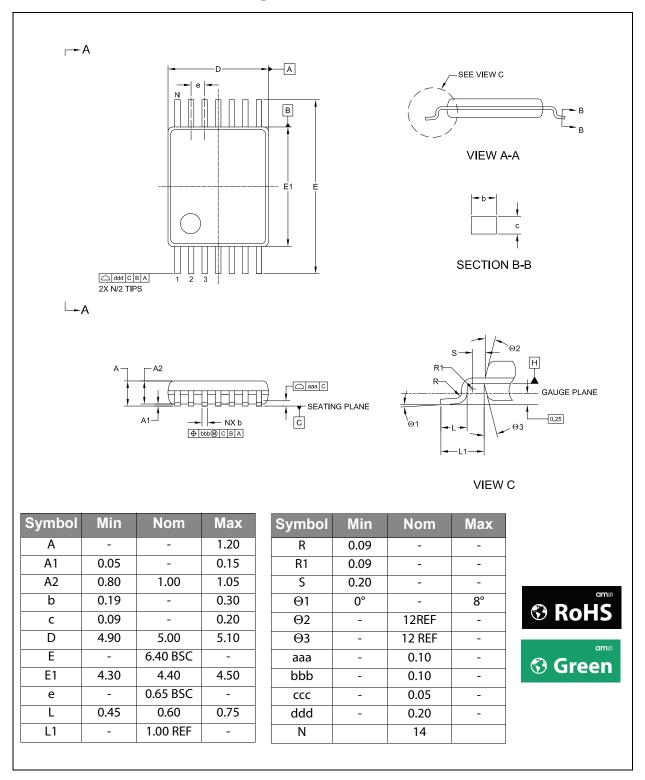

The AS5403 is available in a 14-pin TSSOP package and is qualified according AEC-Q100 for an ambient temperature range from -40°C to 150°C. It operates at a supply voltage of 5V  $\pm 10\%$ .

The programming of the AS5403 is done over the single wire UART interface.

The AS5403 is overvoltage protected up to 18V on the supply and output pins. In addition the supply pins are reverse polarity protected up to -18V.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of AS5403A/D/E, 3D Hall Position Sensor for Linear and Off-Axis Applications are listed below:

#### Figure 1: Added Value of Using AS5403A/D/E

| Benefits                                   | Features                                         |

|--------------------------------------------|--------------------------------------------------|

| High flexibility in magnet selection       | High magnetic input range                        |

| Suppression against magnetic stray fields  | Dual 3D pixel principle                          |

| Suitable for high temperature applications | Temperature range from -40 to 150°C (ambient)    |

| Flexibility in choice of interface         | Analog or PWM output, SPI as alternative         |

| Best in class performance parameters       | Offset and sensitivity accuracy over temperature |

| Flexible mechanical arrangement of magnet  | Flexible configuration registers                 |

| External calculations of raw data          | 3D raw data assessment possible                  |

| High linearity after teaching              | 33 linearization points                          |

| Supporting safety critical applications    | Integrated diagnostic functions                  |

### Applications

Linear position:

- Clutch/brake pedal

- Gearbox sensor

#### Off-Axis:

- Steering angle sensor

- Gearbox shift link

#### Figure 2: Typical Set-Up of AS5403A/D with Magnet (Linear)

Figure 3: Typical Set-Up of AS5403E with Magnet (Off-Axis)

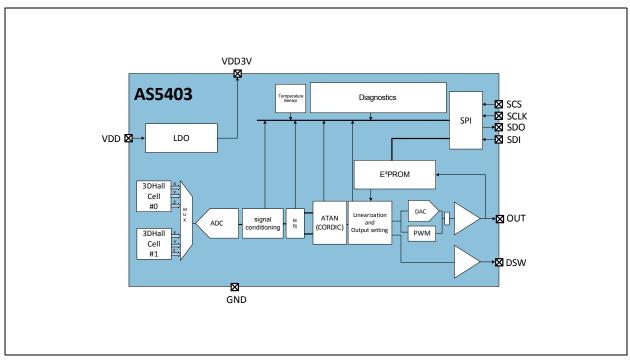

## **Block Diagram**

The functional blocks of this device are shown below:

| 3D Hall pixels:      | The AS5403 contains two 3D Hall pixels, spaced 2.5mm apart.                                                                                                        |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUX:                 | The multiplexer pre-selects depending on the AS5403 variant and chosen mode two/four magnetic components.                                                          |

| ADC:                 | The Sigma-Delta ADC samples the Hall sensors signals selected by the MUX. The sampling of the sensors is done sequentially.                                        |

| Signal conditioning: | This block includes offset and temperature compensation as well as amplitude matching.                                                                             |

| Bi/Bj:               | Preparation of the input signal for the ATAN calculation. Inversion and offset adjustment functions.                                                               |

| ATAN:                | Angle calculation.                                                                                                                                                 |

| Linearization:       | A 33-point linearization of the ATAN output. In addition output settings for gain an clamping.                                                                     |

| Temperature:         | An on-chip temperature sensor is available. It can be read over the SPI interface. This sensor is also used for signal conditioning                                |

| PWM interface:       | The linearized measurement data is available over a single pin in the form of a pulse width modulated (PWM) signal.                                                |

| SPI interface:       | A bi-directional SPI interface allows communication with the chip, including reading measurement data, E <sup>2</sup> PROM contents or writing configuration data. |

| E <sup>2</sup> PROM: | The on-chip E <sup>2</sup> PROM contains the configuration data of the chip.                                                                                       |

| Diagnostics:         | Monitor functions on different blocks to check the correctness of the internal signals.                                                                            |

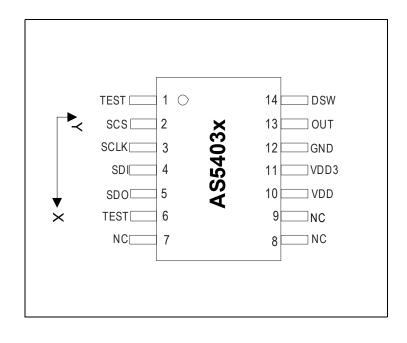

## **Pin Assignments**

Figure 5: AS5403 Pin Configuration

AS5403 Pin Configuration, TSSOP-14 Package (Top View): X indicates the axis of lateral position measurement; z axis is perpendicular to the package surface

## amu

Figure 6: Pin Description

| Pin | Symbol | Туре  | Description                                                                                                                                                                     |

|-----|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TEST   | DI_PD | Test pin connect to GND on PCB                                                                                                                                                  |

| 2   | SCS    | DI_PD | SPI chip select (active high), connect to GND if not used in application                                                                                                        |

| 3   | SCLK   | DI_PD | SPI clock, connect to GND if not used in application                                                                                                                            |

| 4   | SDI    | DI_PD | SPI input data line, connect to GND if not used in application                                                                                                                  |

| 5   | SDO    | DO    | SPI output data line, leave open if not used in application                                                                                                                     |

| 6   | TEST   | DO    | leave open on PCB                                                                                                                                                               |

| 7   | NC     |       | Not connected, Set to GND in application                                                                                                                                        |

| 8   | NC     |       | Not connected, Set to GND in application                                                                                                                                        |

| 9   | NC     |       | Not connected, Set to GND in application                                                                                                                                        |

| 10  | VDD    | S     | Supply Voltage 5 V                                                                                                                                                              |

| 11  | VDD3   | AIO   | Regulator output                                                                                                                                                                |

| 12  | GND    | S     | Ground                                                                                                                                                                          |

| 13  | OUT    | AIO   | Analog/PWM Output, programming option over output.                                                                                                                              |

| 14  | DSW    | AIO   | Programmable digital switch output, connect to pull-up resistor<br>and switch to open-drain <sup>(1)</sup> if not used in application (not<br>applicable in SPI communication). |

#### Note(s):

1. Open-drain configuration: Write DSW\_CFG=0x2 in register EEPROM DSW 0x1FA

#### **PIN Types:**

- S: Supply pad

- AIO: Analog I/O

- DI\_PD: Digital input with internal pull down

- DO: Digital output push-pull

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 7: Absolute Maximum Ratings

| Symbol             | Parameter                                      | Min  | Max | Unit   | Comments                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|------------------------------------------------|------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD                | DC supply voltage at pin VDD                   | -18  | 18  | V      |                                                                                                                                                                                                                                                                                                                                                                                       |

| OUT_OV             | Voltage at pin OUT and DSW                     | -0.3 | 18  | V      |                                                                                                                                                                                                                                                                                                                                                                                       |

| VREG               | DC voltage at VDD3 pin                         | -0.3 | 5   | V      |                                                                                                                                                                                                                                                                                                                                                                                       |

| VDIG               | DC voltage at digital input<br>and output pins | -0.3 | 5   | V      |                                                                                                                                                                                                                                                                                                                                                                                       |

| lscr               | Input current<br>(latchup immunity)            | -100 | 100 | mA     | AEC-Q100-004                                                                                                                                                                                                                                                                                                                                                                          |

| ESD                | Electrostatic discharge                        |      | ± 2 | kV     | AEC-Q100-002                                                                                                                                                                                                                                                                                                                                                                          |

| EEP <sub>cyc</sub> | EEPROM endurance cycles                        |      | 100 | cycles | A part of EEPROM is reserved for<br>factory settings. This part is<br>pre-programmed and locked by<br><b>ams</b> .<br>The customer area of EEPROM can<br>be programmed up to 100 times at<br>$T_{ambient} = 27^{\circ}C$ .<br>EEPROM is intended to be<br>programmed at 0h only in the<br>customer production line and shall<br>not be reprogrammed during<br>operation in the field. |

| T <sub>strg</sub>  | Storage temperature                            | -55  | 150 | °C     | Min – 67°F; Max 302°F                                                                                                                                                                                                                                                                                                                                                                 |

## amu

| Symbol            | Parameter                        | Min | Max | Unit | Comments                                                                                                                                                                                                                                                                                                    |

|-------------------|----------------------------------|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>Body</sub> | Body temperature                 |     | 260 | °C   | The reflow peak soldering<br>temperature (body temperature)<br>specified is in accordance with<br>IPC/JEDEC J-STD-020<br>"Moisture/Reflow Sensitivity<br>Classification for Non-Hermetic<br>Solid State Surface Mount<br>Devices". The lead finish for Pb-free<br>leaded packages is matte tin<br>(100%Sn). |

| RH <sub>NC</sub>  | Relative humidity non-condensing | 5   | 85  | %    |                                                                                                                                                                                                                                                                                                             |

| MSL               | Moisture Sensitivity Level       | 3   |     |      | Represents a maximum floor life time of 168h                                                                                                                                                                                                                                                                |

## **Operating Conditions**

**Operating Conditions:** Operating temperature =  $-40^{\circ}$ C to  $150^{\circ}$ C, VDD = 4.5 - 5.5V unless otherwise noted.

Figure 8: Electrical Characteristics

| Symbol               | Parameter               | Min | Тур | Max | Unit | Comments |

|----------------------|-------------------------|-----|-----|-----|------|----------|

| T <sub>ambient</sub> | Operating temperature   | -40 |     | 150 | °C   |          |

| IDD                  | Supply current          |     | 20  | 25  | mA   |          |

| VDD                  | Positive supply voltage | 4.5 | 5   | 5.5 | V    |          |

| T <sub>STUP</sub>    | Power up time           |     |     | 10  | ms   |          |

## **Magnetic Sensor Conditions**

**Operating Conditions:** Operating temperature =  $-40^{\circ}$ C to  $150^{\circ}$ C, VDD = 4.5 - 5.5V unless otherwise noted.

#### Figure 9: Magnetic Characteristics

| Symbol          | Parameter                     | Min               | Тур | Max              | Unit                | Comments         |

|-----------------|-------------------------------|-------------------|-----|------------------|---------------------|------------------|

|                 |                               | ±5 <sup>(1)</sup> |     | ±50              | mT                  | AS5403A (Bx, Bz) |

| B <sub>IR</sub> | Magnetic Range X,Y,Z          | ±5 <sup>(1)</sup> |     | ±100             | mT                  | AS5403D (Bx, Bz) |

|                 |                               | ±5 <sup>(1)</sup> |     | ±100             | mT                  | AS5403E (Bx, By) |

| SRDxz_temp      | Sensitivity ratio drift Bx/Bz | -3                |     | 3                | %                   | Temperature only |

| SRDxy_temp      | Sensitivity ratio drift Bx/By | -3                |     | 3                | %                   | Temperature only |

| ODx             | Offset drift Bx               | -1 <sup>(3)</sup> |     | 1 <sup>(3)</sup> | %FSR <sup>(2)</sup> |                  |

| ODy             | Offset drift By               | -1 <sup>(3)</sup> |     | 1 <sup>(3)</sup> | %FSR <sup>(2)</sup> |                  |

| ODz             | Offset drift Bz               | -0.5              |     | 0.5              | %FSR <sup>(2)</sup> |                  |

#### Note(s):

1. Minimum condition is valid if both input components are above 5mT.

2. 50mT AS5403A, 100mT AS5403D and AS5403E.

3. Parameter is valid for version AS5403E and AS5403D. AS5403A  $\pm 1.5\% FSR.$

## DC/AC Characteristics for Digital Pads

Figure 10: DC/AC Characteristics

| Symbol | Parameter                 | Min      | Тур | Max | Unit  | Comments |

|--------|---------------------------|----------|-----|-----|-------|----------|

| VIH    | High level input voltage  | 70       |     |     | %VDD3 |          |

| VIL    | Low level input voltage   |          |     | 30  | %VDD3 |          |

| IPD    | Pull-Down input current   | 30       |     | 100 | μΑ    |          |

| ILPD   | Input leakage current PD  | -5       |     | 5   | μΑ    |          |

| VOH    | High level output voltage | VDD3-0.5 |     |     | V     | IL=-4mA  |

| VOL    | Low level output voltage  |          |     | 0.4 | V     | IL=4mA   |

| CL     | Capacitive load           |          |     | 100 | pF    |          |

## **Output Driver Parameters**

Figure 11: Output Driver Characteristics OUT

| Symbol    | Parameter                                   | Min | Тур | Max | Unit     | Comments                                                          |  |  |  |  |

|-----------|---------------------------------------------|-----|-----|-----|----------|-------------------------------------------------------------------|--|--|--|--|

|           | GENERAL                                     |     |     |     |          |                                                                   |  |  |  |  |

| ILIMITLSD | Short circuit output<br>current (LSD)       | 5   | 10  | 20  | mA       | VOUT=+18V                                                         |  |  |  |  |

| ILIMITHSD | Short circuit output<br>current (HSD)       | -20 | -10 | -5  | mA       | VOUT=0V                                                           |  |  |  |  |

| TSCDET    | Short circuit detection time                | 20  |     | 600 | μs       | Output stage turned OFF                                           |  |  |  |  |

| TSCREC    | Short circuit recovery time                 | 2   |     | 20  | ms       | Output stage turned ON                                            |  |  |  |  |

| ILEAK     | Output leakage                              | -20 |     | 20  | μΑ       | VOUT=5V; VDD=5V<br>Limited to T <sub>ambient</sub> =-40°C to 95°C |  |  |  |  |

| BGNDPU    | Output voltage broken<br>GND with pull-up   | 96  |     | 100 | %<br>VDD | Guaranteed by design                                              |  |  |  |  |

| BGNDPD    | Output voltage broken<br>GND with pull-down | 0   |     | 4   | %<br>VDD | Limited to T <sub>ambient</sub> =-40°C to 95°C                    |  |  |  |  |

| BVDDPU    | Output voltage broken<br>VDD with pull-up   | 96  |     | 100 | %<br>VDD | Limited to T <sub>ambient</sub> =-40°C to 95°C                    |  |  |  |  |

| BVDDPD    | Output voltage broken<br>VDD with pull-down | 0   |     | 4   | %<br>VDD | Guaranteed by design                                              |  |  |  |  |

## amu

| Symbol   | Parameter                            | Min  | Тур    | Max | Unit     | Comments                                                                                      |

|----------|--------------------------------------|------|--------|-----|----------|-----------------------------------------------------------------------------------------------|

|          |                                      |      | ANALOG |     |          |                                                                                               |

| OUTVOH   | Output level high                    | 96   |        |     | %<br>VDD | IOUT=-3mA                                                                                     |

| OUTVOL   | Output level low                     |      |        | 4   | %<br>VDD | IOUT=3mA                                                                                      |

| OUTINL   | Output integral non<br>linearity     |      |        | 10  | LSB      | Between 4% and 96% of VDD                                                                     |

| OUTDNL   | Output differential non<br>linearity | -10  |        | 10  | LSB      | Between 4% and 96% of VDD                                                                     |

| OUTOFF   | Output offset                        | -25  |        |     | mV       | Best fit line offset; evaluated between 4% and 96% of VDD                                     |

| OUTUD    | Update rate of the<br>Output         |      | 1000   |     | μs       |                                                                                               |

| OUTSTPR  | Output step response<br>(rising)     |      |        | 150 | μs       | From step on DAC input to<br>90% of VDD on the OUT pin;<br>RPUOUT=4.7KΩ; CLOUT=1nF;<br>VDD=5V |

| OUTSTPF  | Output step response<br>(falling)    |      |        | 150 | μs       | From step on DAC input to<br>10% of VDD on the OUT pin;<br>RPUOUT=4.7KΩ; CLOUT=1nF;<br>VDD=5V |

| OUTDRIFT | Output Voltage<br>Temperature drift  | -0.5 |        | 0.5 | %        | of value at mid code                                                                          |

| OUTRATE  | Output ratiometricity<br>error       | -1.5 |        | 1.5 | %<br>VDD | Between 4% and 96% of VDD                                                                     |

| OUTNOISE | Noise                                |      |        | 25  | mVpp     | 1kHz to 30kHz;<br>at 2048 LSB level, lab<br>characterization only                             |

#### AS5403A/D/E – Electrical Characteristics

## amu

| Symbol             | Parameter                          | Min | Тур        | Max | Unit     | Comments                                                                                                      |  |  |  |  |

|--------------------|------------------------------------|-----|------------|-----|----------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PWM                |                                    |     |            |     |          |                                                                                                               |  |  |  |  |

| PWMF               | PWM frequency                      |     | 1000       |     | Hz       | PWM frequency for version<br>AS5403A and AS5403D and<br>AS5403E 125 Hz in table<br>selection 2. See Figure 44 |  |  |  |  |

| T <sub>SYNCH</sub> | PWM sync time                      |     | 0.1*1/PWMF |     | S        |                                                                                                               |  |  |  |  |

| PWMVOH             | Output voltage high                | 4.6 |            |     | V        | VDD=5V; IOUT=-5mA                                                                                             |  |  |  |  |

| PWMVOL             | Output voltage low                 | 0   |            | 0.4 | V        | VDD=5V, IOUT=5mA                                                                                              |  |  |  |  |

| PWMSRR             | PWM slew rate<br>(rising edge)     | 1   | 2          | 4   | V/µs     | Between 25% and 75%<br>RPUOUT=10kΩ; CLOUT=4.7nF<br>VDD=5V                                                     |  |  |  |  |

| PWMSRF             | PWM slew rate<br>(falling edge)    | 1   | 2          | 4   | V/µs     | Between 75% and 25%<br>RPUOUT=10kΩ; CLOUT=4.7nF<br>VDD=5V                                                     |  |  |  |  |

|                    |                                    |     | PROGRAMMIN | NG  | 1        |                                                                                                               |  |  |  |  |

| OUTVIH             | High level input<br>voltage at OUT | 70  |            |     | %<br>VDD | VDD=5V                                                                                                        |  |  |  |  |

| OUTVIL             | Low level input voltage<br>at OUT  |     |            | 30  | %<br>VDD | VDD=5V                                                                                                        |  |  |  |  |

| BRATE              | UART baud rate                     | 2.4 |            | 9.6 | kHz      | VDD=5V                                                                                                        |  |  |  |  |

## Figure 12: Output Driver Characteristics DSW

| Symbol    | Parameter                             | Min | Тур | Max | Unit          | Comments                                                                                         |  |  |  |  |

|-----------|---------------------------------------|-----|-----|-----|---------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

|           | GENERAL                               |     |     |     |               |                                                                                                  |  |  |  |  |

| DSWISCLS  | Short circuit output current<br>(LSD) | 5   | 10  | 20  | mA            | VDSW=+18 V                                                                                       |  |  |  |  |

| DSWISCHS  | Short circuit output current<br>(LSD) | -20 | -10 | -5  | mA            | VDSW=0V                                                                                          |  |  |  |  |

| DSWTSCDET | Short circuit detection time          |     |     | 5   | %PWM          |                                                                                                  |  |  |  |  |

| DSWTSCRC  | Short circuit recovery time           |     | 16  |     | PWM<br>cycles |                                                                                                  |  |  |  |  |

| DSWVOH    | Output voltage high                   | 4.6 |     |     | V             | VDD=5V; IDSW=-5mA                                                                                |  |  |  |  |

| DSWVOL    | Output voltage low                    | 0   |     | 0.4 | V             | VDD=5V; IDSW=5mA                                                                                 |  |  |  |  |

| DSWSRR    | DSW slew rate<br>(rising edge)        | -4  | -2  | -1  | V/µs          | Between 25% and 75%;<br>RPUDSW = $10k\Omega$ ;<br>CLDSW=4.7nF; VDD=5V<br>(PP with pullup)        |  |  |  |  |

| DSWSRF    | DSW slew rate<br>(falling edge)       | 1   | 2   | 4   | V/µs          | Between 75% and 25%;<br>RPUDSW = $10k\Omega$ ;<br>CLDSW= $4.7nF$ ; VDD= $5V$<br>(PP with pullup) |  |  |  |  |

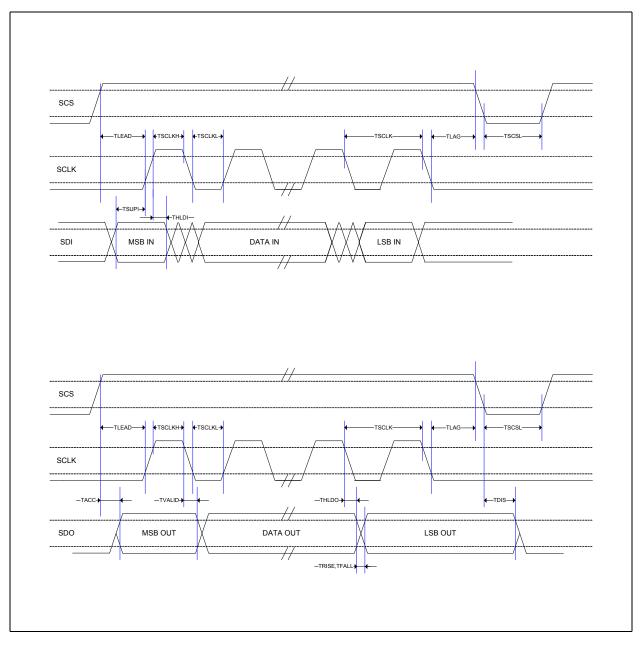

## **SPI Timing**

#### Figure 13: SPI Timing

| Symbol | Parameter               | Min  | Тур | Max | Unit | Note       |

|--------|-------------------------|------|-----|-----|------|------------|

| TSCLK  | SCLK period             | 250  |     |     | ns   |            |

| TSCLKH | SCLK high phase         | 125  |     |     | ns   |            |

| TSCLKL | SCLK low phase          | 125  |     |     | ns   |            |

| TLEAD  | SCS lead time           | 100  |     |     | ns   |            |

| TLAG   | SCS lag time            | 100  |     |     | ns   |            |

| TSCSL  | SCS low phase           | 2500 |     |     | ns   |            |

| TSUPI  | SDI input setup time    | 50   |     |     | ns   |            |

| THLDI  | SDI input hold time     | 50   |     |     | ns   |            |

| TVALID | SDO output valid time   |      |     | 50  | ns   | CL = 100pF |

| THLDO  | SDO output hold time    | 0    |     |     | ns   | CL = 100pF |

| TACC   | SDO output access time  |      |     | 100 | ns   | CL = 100pF |

| TDIS   | SDO output disable time |      |     | 50  | ns   | CL = 100pF |

| TRISE  | SDO output rise time    |      |     | 60  | ns   | CL = 100pF |

| TFALL  | SDO output fall time    |      |     | 60  | ns   | CL = 100pF |

#### Figure 14: SPI Timing Diagram

Figure 15: UART Timing

| Symbol | Parameter      | Min | Тур | Мах | Unit |

|--------|----------------|-----|-----|-----|------|

| UARTF  | UART baud rate | 2.4 |     | 9.6 | kHz  |

dm

## **Functional Description**

The AS5403 is manufactured in a CMOS process and uses lateral and vertical Hall sensor technology for sensing the magnetic field distribution in all 3D directions. The integrated 3D-Hall pixels are placed with a pixel pitch of 2.5 mm and deliver a voltage representation of the magnetic field at the surface of the IC.

Through Sigma-Delta Analog / Digital Conversion and Digital Signal-Processing (DSP) algorithms, the AS5403 provides accurate high-resolution absolute angular position information. For this purpose a Coordinate Rotation Digital Computer (CORDIC) calculates the angle and the magnitude.

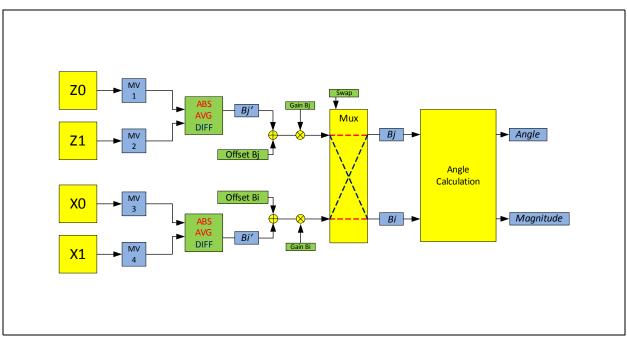

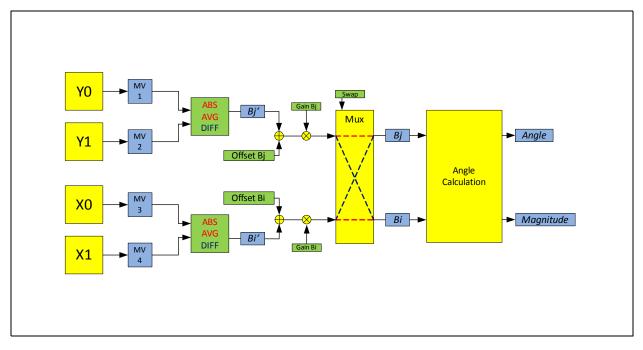

## **Signal Processing Path Front**

The AS5403 can be configured in different operation modes. These are absolute (ABS), average (AVG) and differential (DIFF). The internal calculation scene is changed automatically with the selected mode.

Figure 16: Signal Processing Path AS5403A and AS5403D (Bx and Bz)

#### Note(s):

1. Yellow  $\rightarrow$  Functional block

2. Blue  $\rightarrow$  Readable register

3. Green  $\rightarrow$  Write/Readable EEPROM parameter

## amu

#### Figure 17: Signal Processing Path AS5403E (Bx and By)

#### Note(s):

1. Yellow  $\rightarrow$  Functional block

2. Blue  $\rightarrow$  Readable register

3. Green  $\rightarrow$  Write/Readable EEPROM parameter

The individual component from 3D Hall pixel 0 and 3D Hall pixel 1 are measured sequentially. Refer to Figure 4. This sequence is predefined and depends also on the mode selection (absolute, average or differential). The digital values after conversation are stored in the measurement value registers MV1 to MV4. These values represent the raw data. The pre-calculation leads to internal result values of Bi' and Bj'. The final Bi and Bj values are available after further manipulation possibilities like offset or gain manipulation. In addition is an exchange of Bi and Bj possible over the swap function. The calculated angle and magnitude can be read out too.

### **Internal Calculation Formulas**

| Absolute Mode (ABS)               | Average Mode (AVG)                | Differential Mode (DIFF)          |

|-----------------------------------|-----------------------------------|-----------------------------------|

| Bj' = MV1                         | Bj' = (MV1 + MV2)/2               | Bj' = -(MV1 - MV2)/2              |

| Bi' = MV3                         | Bi' = (MV3 + MV4)/2               | Bi' = (MV3 - MV4)/2               |

| Bj = Gain Bj * (Bj' + Offset Bj ) | Bj = Gain Bj * (Bj' + Offset Bj ) | Bj = Gain Bi * (Bi' + Offset Bi ) |

| Bi = Gain Bi * (Bi' + Offset Bi ) | Bi = Gain Bi * (Bi' + Offset Bi ) | Bi = Gain Bj * (Bj' + Offset Bj ) |

| $ATAN2(-B_{i^{\prime}}B_{j})$     | $ATAN2(-B_{i^{i}}B_{j})$          | $ATAN2(-B_{i^{j}}B_{j})$          |

|                                   |                                   |                                   |

Figure 18: Formulas for Calculation

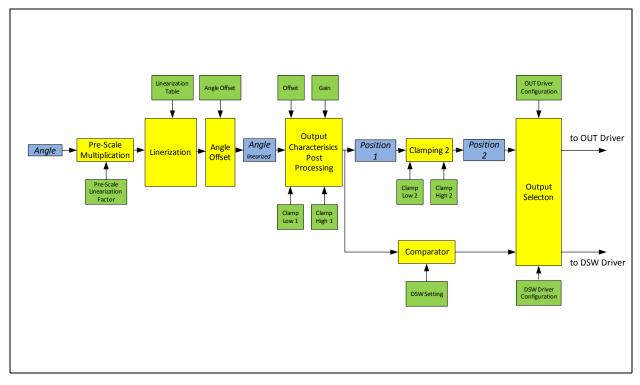

## **Signal Processing Path Backend**

#### Note(s):

- 1. Yellow  $\rightarrow$  functional block

- 2. Blue  $\rightarrow$  Readable register

- 3. Green  $\rightarrow$  Write/readable EEPROM parameter

A pre-scale function can be used to extend the angle range. This is in particular needed in sector applications (off-axis) or small linear strokes. This function optimizes the usage of the linearization function in the following step. The linearization takes maximum 33 supporting point. These points are equally spread over the angular range. The post-processing function is able to manipulate the output characteristic in gain, offset and clamping. The digital output switch function uses a comparator. The switching value and hysteresis can be defined.

Finally the configuration of the output defines the operation of the output drivers.

## Operation

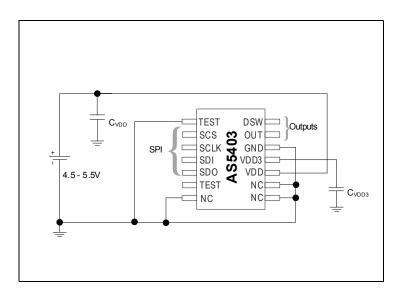

The AS5403 operates at 5V  $\pm$ 10%, using one internal Low-Dropout (LDO) voltage regulator. For operation, the 5V supply is connected to pin VDD. While VDD3 (LDO output) must be buffered by 1µF capacitor, the VDD requires a 1µF capacitor. All capacitors (low ESR ceramic) are supposed to be placed close to the supply pins (see Figure 20).The VDD3 output is intended for internal use only. It must not be loaded with an external load.

#### Figure 20: Connections for 5V Supply Voltages

#### Note(s):

- 1. The pin VDD3 must always be buffered by a capacitor. It must not be left floating, as this may cause instable internal supply voltages which may lead to larger output jitter of the measured angle.

- The supply pin is over voltage protected up to 18V. In addition the device has a reverse polarity protection.

## **External Components**

#### Figure 21:

External Components in the System

| Symbol             | Parameter                | Min | Тур | Max | Unit | Note |

|--------------------|--------------------------|-----|-----|-----|------|------|

| C <sub>VDD</sub>   | VDD Buffer Capacitance   | 0.8 | 1   | 1.2 | μF   |      |

| ESRCBVDD           | ESR of VDD Capacitance   |     |     | 0.3 | Ω    |      |

| C <sub>VDD3</sub>  | VDD3 Buffer Capacitor    | 0.8 | 1   | 1.2 | μF   |      |

| ESRREG3            | ESR of VDD3 Capacitance  |     |     | 0.3 | Ω    |      |

| C <sub>LOUT</sub>  | OUT Load Capacitance     | 0   |     | 20  | nF   |      |

| R <sub>PUOUT</sub> | OUT Pull-Up Resistance   | 4.7 |     | 10  | kΩ   |      |

| R <sub>PDOUT</sub> | OUT Pull-Down Resistance | 4.7 |     | 10  | kΩ   |      |

| C <sub>LDSW</sub>  | DSW Load Capacitance     | 0   |     | 20  | nF   |      |

| R <sub>PUDSW</sub> | DSW Pull-Up Resistance   | 4.7 |     | 10  | kΩ   |      |

| R <sub>PDDSW</sub> | DSW Pull-Down Resistance | 4.7 |     | 10  | kΩ   |      |

## **Built-In Safety**

Figure 22: Diagnostic Functions of the AS5403

| Monitoring                         | Error Type                     | Source           | Comments                           |

|------------------------------------|--------------------------------|------------------|------------------------------------|

| VDD undervoltage                   | Hardware Error <sup>(1)</sup>  | Power management | Recoverable                        |

| VDD overvoltage                    | Hardware Error <sup>(1)</sup>  | Power management | Recoverable                        |

| VREG undervoltage                  | Hardware Error <sup>(1)</sup>  | Power management | Recoverable                        |

| Oscillator failure                 | Hardware Error <sup>(1)</sup>  | CLK management   | Not recoverable                    |

| Loss of GND                        | Hardware Error <sup>(1)</sup>  | Output driver    |                                    |

| Loss of VDD                        | Hardware Error <sup>(1)</sup>  | Output driver    |                                    |

| Output short circuit               | Hardware Error <sup>(1)</sup>  | Output driver    | Recoverable after 16<br>PWM period |

| PWM/Digital switch readout failure | Hardware Error <sup>(1)</sup>  | Output driver    | Recoverable after 16<br>PWM period |

| Signature failure                  | Hardware Error <sup>(1)</sup>  | EEPROM           | Not recoverable                    |

| Linearization overflow             | Algorithm Error <sup>(2)</sup> | Digital DSP      |                                    |

| Range warning                      | Algorithm Error <sup>(2)</sup> | Digital DSP      |                                    |

| Sensitivity correction overflow    | Algorithm Error <sup>(2)</sup> | Digital DSP      |                                    |

| Normalization overflow             | Algorithm Error <sup>(2)</sup> | Digital DSP      |                                    |

| Magnet lost                        | Algorithm Error <sup>(2)</sup> | Digital DSP      |                                    |

| Self monitoring error              | Hardware Error <sup>(1)</sup>  | Digital DSP      | Not recoverable                    |

| PWM synchronization error          | Hardware Error <sup>(1)</sup>  | PWM engine       | Not recoverable                    |

#### Note(s):

1. Hardware Error output to high impedance (HZ).

2. Algorithm Error PWM at 5%DC and /PWM at 95%DC depending on Diag\_High, digital switches in high impedance (HZ), analog output insight upper or lower failure band depending on Diag\_High. All algorithm errors are recoverable.

## **Output Drivers**

AS5403 has two output stages, with different characteristics. The output driver on pin OUT can be programmed as analog output or low side driver PWM (/PWM), and includes a receiver for the bidirectional communication used to configure the device at module level. The driver on pin DSW is a low side only and can be configured as /PWM (PWM) or digital switch but doesn't have the receiver and in communication behaves as programmed in the EEPROM. Possible configurations for OUT selectable from EEPROM bits are:

Figure 23: Possible Configurations of OUT Pin

| Mode                             | OUT<br>CFG <2> | OUT<br>CFG <1>                                                               | OUT<br>CFG <0>                                                              | Note                                                                                                   |

|----------------------------------|----------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Analog output<br>mode            | 0              | 0                                                                            | 0                                                                           | Push-Pull analog output driver external pull up or pull down required                                  |

|                                  |                | Pulse width modulated output with push/pull driver external pull up required |                                                                             |                                                                                                        |

| PWM open drain                   |                |                                                                              | Pulse width modulated output with low side driver external pull up required |                                                                                                        |

| PWMn push/pull                   | 1              | 0                                                                            | 0                                                                           | Inverted pulse width modulated output<br>with push/pull driver external pull up<br>required            |

| PWMn push/pull                   | 1              | 0                                                                            | 1                                                                           | Inverted pulse width modulated output<br>with low side driver external pull up<br>required             |

| PWM open drain reduced slew rate | 1              | 1                                                                            | 0                                                                           | Pulse width modulated output with low<br>side driver external pull up required<br>reduced falling edge |

#### Note(s):

1. All other not specified combinations are reserved and not allowed. To avoid floating situation in diagnostic case a pull up resistor is recommended also in push/pull mode.

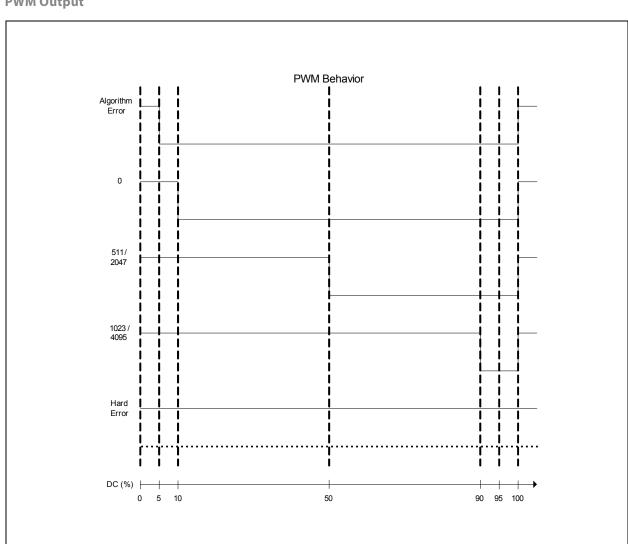

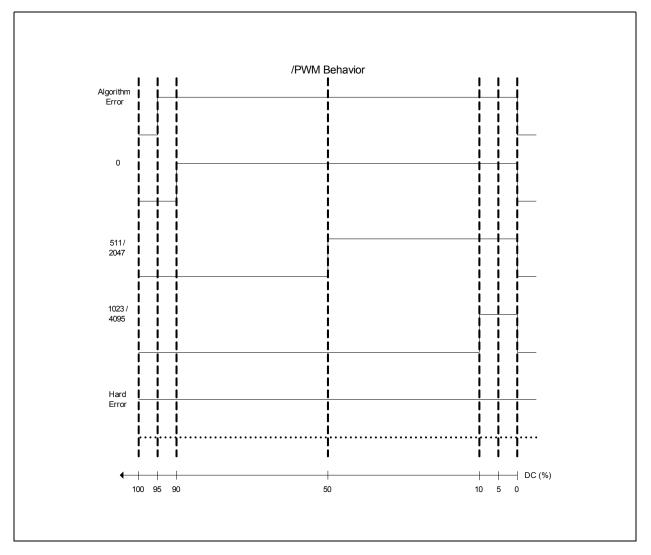

#### **PWM Output**

When the PWM mode is selected the measured position is proportional to the duty cycle. A range of 10% to 90% of the PWM period is used to carry the information and the remaining ranges are used as a fail signal (a 5% PWM means Algorithm Error, no change over a whole period means a Hard Error). The 80% of the PWM period contains the position information. Depending on the AS5403 version (A/D/E) and mode selection the PWM frequency can change between 1.0 kHz and 0.125 kHz. The PWM resolution can also change between 10 bit (1024 positions) for 1.0 kHz and 12 bit (4096 positions) for 0.125 kHz. The behavior of PWM and /PWM is shown in the following figures.

Figure 24: PWM Output

#### Figure 25: /PWM Output Signal

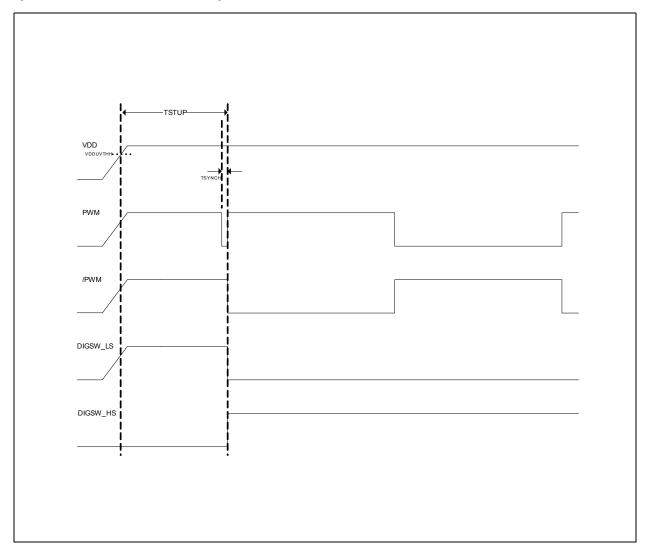

At the end of the power up phase, after an under voltage recovery and after the transition from sleep to normal mode a synch pulse with duration  $T_{SYNCH}$  precedes the PWM wave as shown in the following picture. Only after the pulse the digital switches leave the HZ state.

#### Figure 26: Sync Pulse at PWM After Power-Up

## **Digital Switch**

The AS5403 provides a digital output switch function. This signal can be defined by settings in the EEPROM. The switching point DSW SW POINT <11:0> are compared to the calculated linearized sensor position. The polarity is selectable and the hysteresis is configurable. Possible configurations for DSW selectable from EEPROM bits are:

Figure 27: Possible Configurations of DSW Pin

| Mode                         | DSW<br>CFG<2> | DSW<br>CFG <1> | DSW<br>CFG <0> | Comments                                                                                    |

|------------------------------|---------------|----------------|----------------|---------------------------------------------------------------------------------------------|

| Digital switch<br>push/pull  | 0             | 0              | 0              | Push-Pull digital output driver external pull up required                                   |

| Digital switch open source   | 0             | 0              | 1              | High side digital driver external pull<br>down required                                     |

| Digital switch<br>open drain | 0             | 1              | 0              | Low side digital driver external pull up required                                           |

| PWMn push/pull               | 0             | 1              | 1              | Inverted pulse width modulated output<br>with push/pull driver external pull up<br>required |

| PWMn open drain              | 1             | 0              | 0              | Inverted pulse width modulated output<br>with low side driver external pull up<br>required  |

| PWM push/pull                | 1             | 0              | 1              | Pulse width modulated output with low side driver external pull up required                 |

| PWM open drain               | 1             | 1              | 0              | Pulse width modulated output with low side driver external pull up required                 |

#### Note(s):

1. All other not specified combinations are reserved and not allowed.

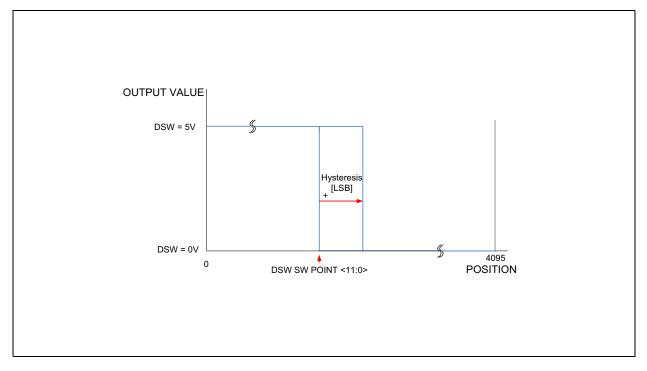

DSW\_POL= 1:

Figure 28: DSW Characteristic with Positive Polarity

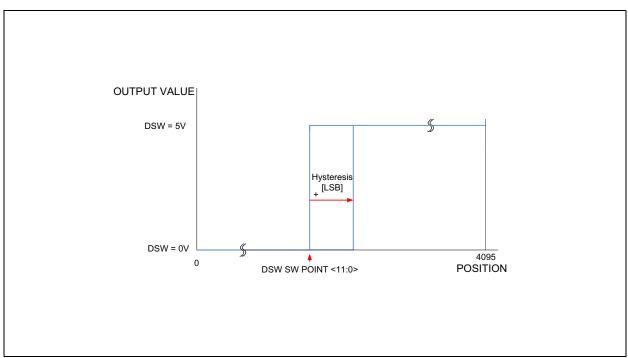

DSW\_POL=0:

Figure 29: DSW Characteristic with Negative Polarity

## 4-Wire Serial Peripheral Interface (SPI)

AS5403 is equipped with a 4wire serial peripheral interface (SPI) to access the EEPROM memory and the read /write registers. SCS input pin (active high) selects the device for serial transfers. Register data is shifted in from the external master on the SDI pin or shifted out from the device on the SDO pin on each subsequent SCLK, in both the cases MSB first. Data are captured on the rising edge and shifted on the falling edge of SCLK for receiving command and transmitting command. An even parity bit is used to check the consistency of the frame. SPI protocol is built by frames; each frame is composed by 4 bytes and it is detected only when SCS pin is high. If a frame contains a number of bits different from the expected the command is not executed.

Valid commands for the SPI interface are the following:

Figure 30: Commands SPI

| CMD Name | CMD<br>Value | Note                           | AS5403<br>Communication Mode |

|----------|--------------|--------------------------------|------------------------------|

| Write    | 0            | Write data in the memory area  | SLAVE                        |

| Read     | 1            | Read data from the memory area | SLAVE/MASTER                 |

### Write (0)

The first byte of the write command is composed by the command identifier (CMD) the even parity bit (PAR) and the MSBs of the address AD<10:8>.

The second byte of the command is the remaining part of the address AD<7:0>, the third and the fourth byte contains the data word we want to write (D<15:0>) on address AD<10:0>. The device forces the SDO pin low. With this command it is possible to access the EEPROM locations and the read/write registers area.

Figure 31: SPI Write

## Read (1)

The read command is composed by 2 frames, in the first one the external master sends the command, the even parity and the address to be read on the SDO line (the last 16 bits are ignored). The device forces the SDO pin low.

#### Figure 32: SPI Read

> After the switching time (TSCSL) the device drives the SDO line and when the SCS pin goes high starts to send out the answer. The first byte of the second frame is composed by the command the device is executing, the even parity and the MSBs of the address required in the previous frame (AD<10:8>). The second byte of the command is the remaining part of the address AD<7:0>, the third and the fourth bytes are the data word at the required address (AD<10:0>). With this command it is possible to access the EEPROM locations and the read/write registers area.

## Programming the AS5403

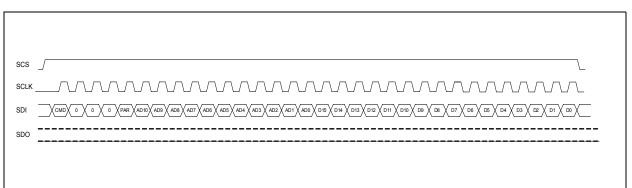

A standard half duplex UART protocol is used to exchange data with the device in the communication mode.

### **UART Interface for Programming**

The AS5403 uses a standard UART interface with two bytes for address and two bytes for the data content. The read or write mode is selected in the first byte. An even parity for every byte is included. The timing (baud-rate) is selected by the AS5403 over an initial command from the master. The baud rate register can be read and overwritten. The keep synchronization it AS5403 synchronizes art every Start bit. This happens during a standard write access 3 times. A time out function detects not complete commands and resets the AS5403 UART after the timeout period.

Figure 33: Valid Commands

| CMD Name | Description                           | AS5403 Communication Mode |

|----------|---------------------------------------|---------------------------|

| Write    | Write data in the EEPROM/ SFR memory  | SLAVE                     |

| Read     | Read data from the EEPROM/ SFR memory | SLAVE/MASTER              |

In case of Write command the request is followed by the frames containing the data to write. In case of Read command the communication direction will change and the device will answer with the frames containing the data requested.

#### Frame Organization

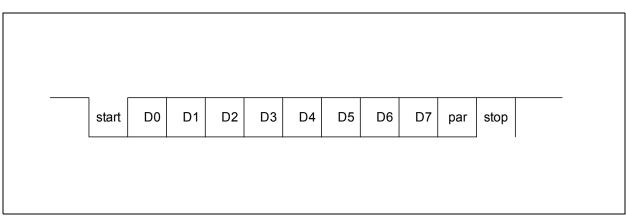

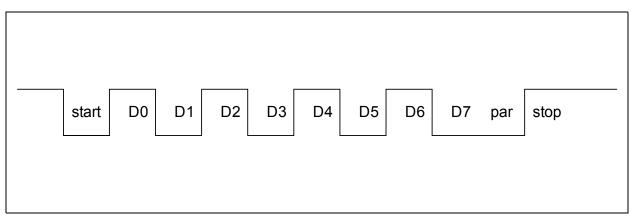

The UART frame consists of 1 start bit (low level), 8 data bit, 1 even-parity bit and 1 stop bit (high level). Data are transferred from LSB to MSB.

In case of read command the idle phase between the command and the answer is TSW.

#### Figure 35: Bit Assignment in Frame

| Symbol | Parameter                | Min | Тур | Мах | Unit |

|--------|--------------------------|-----|-----|-----|------|

| START  | Start bit                |     | 1   |     | TBIT |

| Dx     | Data bit                 |     | 1   |     | TBIT |

| PAR    | Parity bit               |     | 1   |     | TBIT |

| STOP   | Stop bit                 | 1   |     |     | TBIT |

| TSW    | Slave/Master Switch Time |     | 7   |     | TBIT |

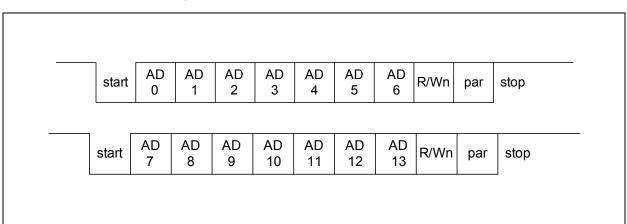

Each communication starts with the reception of a request from the external controller. The request consists of 3 frames: one synchronization byte and 1 word for the command.

The synchronization frame contains the data 0x55 and allows the UART to measure the external controller baud-rate.

#### Figure 36: Synchronization Frame 0x55 Hex

The 2nd and 3rd frames contain the command Read/ Write (1 bit) and the address (7+7 bits):

#### Figure 37: 2nd and 3rd Frame Addressing

### Write Command

Figure 38: Write Command Frames

|          |          | frame:       |                      |          |          |          |          |          |           |     |      |

|----------|----------|--------------|----------------------|----------|----------|----------|----------|----------|-----------|-----|------|

|          | start    | D0           | D1                   | D2       | D3       | D4       | D5       | D6       | D7        | par | stop |

| Write co | mmand f  | rame lov     | v addres             | s:       |          |          |          | -        |           |     | -    |

|          | start    | AD<br>0      | AD<br>1              | AD<br>2  | AD<br>3  | AD<br>4  | AD<br>5  | AD<br>6  | R/<br>Wn  | par | stop |

| Write co | mmand f  | rame hig     | ah addre             | ss:      |          |          |          | •        | · · · · · |     | ,    |

|          | start    | AD<br>7      | AD<br>8              | AD<br>9  | AD<br>10 | AD<br>11 | AD<br>12 | AD<br>13 | R/Wn      | par | stop |

|          |          |              |                      | write or | address  | s AD<13  | :0>):    |          |           |     |      |

| Data L f | rame (LS | Bs of the    | e data to            | write of |          |          |          |          |           |     |      |

| Data L f | rame (LS | Bs of the D0 | e data to<br>D0<br>1 | D0<br>2  | D0<br>3  | D0<br>4  | D0<br>5  | D0<br>6  | D0<br>7   | par | stop |

|          |          | D0<br>0      | D0<br>1              | D0<br>2  | 3        | 4        |          |          |           | par | stop |

**Read Command**

#### Figure 39: Read Command Frames

|                 | ization 1 | frame:   |           |          |          |          |          |          |          |     |      |

|-----------------|-----------|----------|-----------|----------|----------|----------|----------|----------|----------|-----|------|

|                 | start     | D0       | D1        | D2       | D3       | D4       | D5       | D6       | D7       | par | stop |

| Read con        | nmand f   | rame lov | w addres  | s:       |          |          |          |          |          |     |      |

|                 | start     | AD<br>0  | AD<br>1   | AD<br>2  | AD<br>3  | AD<br>4  | AD<br>5  | AD<br>6  | R/<br>Wn | par | stop |

| Read con        | nmand f   | rame hig | gh addre  | ss:      | 11       | L        |          |          | •        |     | -    |

|                 | start     | AD<br>7  | AD<br>8   | AD<br>9  | AD<br>10 | AD<br>11 | AD<br>12 | AD<br>13 | R/Wn     | par | stop |

| Data L fra      | ame (LS   | Bs of th | e data re | ad at th | e addres | s AD<1   | 3:0>):   |          | 1        |     | J    |

|                 | start     | D0<br>0  | D0<br>1   | D0<br>2  | D0<br>3  | D0<br>4  | D0<br>5  | D0<br>6  | D0<br>7  | par | stop |

| ∟<br>Data H fra | me (MS    | Bs of th | e data re | ad at th | e addres | s AD<1   | 3:0>):   | I        | I.       |     |      |

|                 | start     | D0       | D0<br>9   | D0<br>10 | D0<br>11 | D0<br>12 | D0<br>13 | D0<br>14 | D0<br>15 | par | stop |

### **BAUD RATE Automatic Detection**

The UART includes a built-in baud-rate monitor that uses the synchronization frame to detect the external controller baud rate. This baud-rate is used after the synchronization byte to decode the following frame and to transmit the answer and it is stored in the BAUDREG register.

### **Programming Procedure**

The EEPROM programming is possible over the SPI or UART interface. A page write/read mode with 64 pages 8 words each is implemented.

Figure 40: Page Mode Address

| Address       | Page |

|---------------|------|

| 0x000 - 0x007 | 1    |

| 0x008 - 0x00F | 2    |

| :             | :    |

| 0x1F8 - 0x1FF | 64   |

Page Write mode procedure:

- 1. Write 0x00 on address 0x2FF (START DSP = 0)

- 2. Write the EEPROM words (SPI/UART) inside a page (min 1 max 8 words)

- 3. Write 0x0003 on address 0x2FF (CFG\_EPP=11)

- 4. Wait for 10 ms

- 5. Repeat from 2. for further programming.

It is important that the write access to the selected EEPROM page are consecutive: a write command in a different page or a read command before writing CFG\_EPP will delete the data. A writing to factory reserved area will be ignored.

After programming it is mandatory to read back the EEPROM content and to download again the EEPROM to avoid misalignment with the mirror registers. This can be done with a power up or writing 0x0004 on address 0x2FF (EE\_DWNL SFR).

The programming procedure is not allowed in case Customer Lock word is 0x55AA after EEPROM download (mask\_fuse=1).

## Lock Procedure and Signature Calculation

The AS5403 contains a signature diagnostic function for the EEPROM. This signature is calculated in the AS5403 during power up and is compared to the calculated signature directly after the end of line calibration by the customer. A deviation leads to an error indication in the diagnostic flag or into the failure band mode at the output. The signature check is enabled in case of a locked device by the user.

## **Device Configuration**

AS5403 is equipped with a 1kx8 EEPROM memory to store the factory settings and the customer configuration data. The device can be configured using the UART or 4wire Serial Peripheral Interface (SPI).

#### **EEPROM Memory Map**

**Note(s):** Write 0x0000 hex to register address 0x2FF (START DSP = 0) before a read or write access to EEPROM.

Figure 41: EEPROM Memory Map

| ADDRESS (HEX) | EEPROM Location Name                 |

|---------------|--------------------------------------|

| 0x00B         | Sequencer Control                    |

| 0x00F         | Magnet Lost threshold and hysteresis |

| 0x019         | Offset Bj                            |

| 0x01A         | Gain Bj                              |

| 0x01E         | Gain Bi                              |

| 0x01F         | Offset Bi                            |

| 0x05F         | Linearization table entry 16         |

| 0x060         | Linearization table entry 0          |

| 0x061         | Linearization table entry 1          |

| 0x062         | Linearization table entry 2          |

| 0x063         | Linearization table entry 3          |

| 0x064         | Linearization table entry 4          |

| 0x065         | Linearization table entry 5          |

| 0x066         | Linearization table entry 6          |

| 0x067         | Linearization table entry 7          |

| 0x068         | Linearization table entry 8          |

| 0x069         | Linearization table entry 9          |

| 0x06A         | Linearization table entry 10         |

| 0x06B         | Linearization table entry 11         |

| 0x06C         | Linearization table entry 12         |

| 0x06D         | Linearization table entry 13         |

| 0x06E         | Linearization table entry 14         |

| 0x06F         | Linearization table entry 15         |

| 0x070         | Linearization table entry -16        |

## amu

| ADDRESS (HEX) | EEPROM Location Name                   |

|---------------|----------------------------------------|

| 0x071         | Linearization table entry -15          |

| 0x072         | Linearization table entry -14          |

| 0x073         | Linearization table entry -13          |

| 0x074         | Linearization table entry -12          |

| 0x075         | Linearization table entry -11          |

| 0x076         | Linearization table entry -10          |

| 0x077         | Linearization table entry -9           |

| 0x078         | Linearization table entry -8           |

| 0x079         | Linearization table entry -7           |

| 0x07A         | Linearization table entry -6           |

| 0x07B         | Linearization table entry -5           |

| 0x07C         | Linearization table entry -4           |

| 0x07D         | Linearization table entry -3           |

| 0x07E         | Linearization table entry -2           |

| 0x07F         | Linearization table entry -1           |

| 0x1CF         | Pre-Scale linearization                |

| 0x1D0         | Post-Processing offset                 |

| 0x1D1         | Post-Processing gain                   |

| 0x1D2         | Clamp Low 1                            |

| 0x1D3         | Clamp High 1                           |

| 0x1F5         | Clamp High 2 (MSBs), Clamp Low 2       |

| 0x1F6         | Clamp High 2 (LSBs)                    |

| 0x1F7         | Angle offset                           |

| 0x1F8         | Customer LOCK                          |

| 0x1F9         | Output configuration and PWM frequency |

| 0x1FA         | DSW driver configuration               |

| 0x1FB         | DSW settings                           |

| 0x1FC         | Customer ID                            |

| 0x1FD         | Customer ID                            |

| 0x1FE         | Customer ID                            |

| 0x1FF         | EEPROM signature + customer ID         |

# amu

# Figure 42:

| EEPROM | Sequencer | Control | 0x00B |

|--------|-----------|---------|-------|

|--------|-----------|---------|-------|

| Register<br>Hex | Access | Bit      | Function         | Default | Note                                                                                                             |  |

|-----------------|--------|----------|------------------|---------|------------------------------------------------------------------------------------------------------------------|--|

|                 |        |          | D15 (MSB)        |         |                                                                                                                  |  |

|                 |        | D14      | Reserved         | 0       |                                                                                                                  |  |

|                 |        | D13      |                  |         |                                                                                                                  |  |

|                 |        | D12      | ExtRng           | 0       | Extended Range (for differential<br>mode):<br>0 = disabled<br>1 = enabled                                        |  |

|                 |        | D11      | Reserved         | 0       |                                                                                                                  |  |

|                 |        | D10      | Swap             | 0       | Swap Bi and Bj before angle calculation                                                                          |  |

|                 |        | D9       | Reserved         | 0       |                                                                                                                  |  |

|                 |        | D8       | Reserved         | 0       |                                                                                                                  |  |

|                 |        | D7       | Table Select <1> | 0       | These bits allow the selection of 3 different operating modes, stored in                                         |  |

| 0x00B           | R/W    | D6       | Table Select <0> | 1       | 3 individual sequencer tables.<br>Do not use 11> no operation                                                    |  |

|                 |        | D5       | Reserved         | 0       |                                                                                                                  |  |

|                 |        | D4       | DIFF             | 0       | Differential mode:<br>0 = absolute measurement of one<br>pixel<br>1 = differential measurement of<br>both pixels |  |

|                 |        | D3       | Reserved         | 0       |                                                                                                                  |  |

|                 |        | D2       | SeqEn            | 1       | 1 = sequencer enabled<br>0 = sequencer disabled                                                                  |  |

|                 |        | D1       | AVG              | 1       | Average mode:<br>0 = absolute measurement of one<br>pixel,<br>1 = average measurement of both<br>pixels          |  |

|                 |        | D0 (LSB) | Reserved         | 0       |                                                                                                                  |  |

## Figure 43:

Possible Table Selection AS5403A and AS5403D

|                             | Table 0<br>Table Select 00                  | Table 1<br>Table Select 01                       | Table 2<br>Table Select 10                       |  |

|-----------------------------|---------------------------------------------|--------------------------------------------------|--------------------------------------------------|--|

| Sensor<br>arrangement       | X/Z                                         | X/Z                                              | X/Z                                              |  |

| EEPROM<br>0x00B<br>settings | Absolute Mode Pixel0<br>1 kHz Sampling Rate | Differential/Average Mode<br>1 kHz Sampling Rate | Differential/Average Mode<br>1 kHz Sampling Rate |  |

| Magnet<br>orientation       |                                             |                                                  |                                                  |  |

|                             | <u>م</u>                                    |                                                  |                                                  |  |

Figure 44:

Possible Table Selection AS5403E

|                             | Table 0<br>Table Select 00                       | Table 1<br>Table Select 01           | Table 2<br>Table Select 10               |  |  |  |

|-----------------------------|--------------------------------------------------|--------------------------------------|------------------------------------------|--|--|--|

| Sensor<br>arrangement       | X/Y                                              | X/Y                                  | X/Y                                      |  |  |  |

| EEPROM<br>0x00B<br>settings | Differential/Average Mode<br>1 kHz Sampling Rate | Absolute Mode<br>1 kHz Sampling Rate | Absolute Mode<br>0.125 kHz Sampling Rate |  |  |  |

| Magnet<br>orientation       | Off-axis (ring magnet or sector magnet)          |                                      |                                          |  |  |  |

#### Figure 45: **EEPROM Magnet Lost 0x00F**

| Register<br>Hex | Access | Bit       | Function       | Default | Note                                                      |

|-----------------|--------|-----------|----------------|---------|-----------------------------------------------------------|

|                 |        | D15 (MSB) |                | 0       |                                                           |

|                 |        | :         | Reserved       | :       |                                                           |

|                 |        | D11       |                | 0       |                                                           |

|                 |        | D10       | MgnLostHyst<2> | 1       |                                                           |

| 0x00F           | R/W    | :         | :              | :       | Magnet Lost hysteresis                                    |

|                 |        | D8        | MgnLostHyst<0> | 0       |                                                           |

|                 |        | D7        | MgnLostLmt<7>  | 0       |                                                           |

|                 |        | :         | :              | :       | Magnet Lost threshold value<br>compared to register 0x520 |

|                 |        | D0 (LSB)  | MgnLostLmt<0>  | 0       | 1                                                         |

The magnitude information is compared with the magnet lost threshold value calculated with following formula:

MagnetLostLimit = MgnLostLmt <7:0>\*64

The hysteresis is calculated using following formula:

Hysteresis = MagnetLost Limit  $*\frac{1}{2^{MgnLostHys \ i<2.0>}}$

*MgnLostHyst*<2:0>=0 disables the hysteresis

Figure 46: EEPROM Offset Bj 0x019

| Register<br>Hex | Access | Bit       | Function  | Default | Note                                 |

|-----------------|--------|-----------|-----------|---------|--------------------------------------|

|                 |        | D15 (MSB) |           |         | Offset to the Bj value to improve    |

| 0x019           | R/W    | :         | Offset Bj | 0       | performance                          |

|                 |        | D0 (LSB)  |           |         | Signed integer, range [-32768;32767] |

#### Figure 47: EEPROM Offset Bi 0x01F

| Register<br>Hex | Access | Bit       | Function  | Default | Note                                 |

|-----------------|--------|-----------|-----------|---------|--------------------------------------|

|                 |        | D15 (MSB) |           |         | Offset to the Bi value to improve    |

| 0x01F           | R/W    | :         | Offset Bi | 0       | performance                          |

|                 |        | D0 (LSB)  |           |         | Signed integer, range [-32768;32767] |

Figure 48: EEPROM Gain Bj 0x01A

| Register<br>Hex | Access | Bit       | Function | Default       | Note                                                 |

|-----------------|--------|-----------|----------|---------------|------------------------------------------------------|

|                 |        | D15 (MSB) |          |               |                                                      |

| 0x01A           | R/W    | :         | Gain Bj  | +1<br>decimal | Gain to the Bj value<br>Signed integer, range [-1;1] |

|                 |        | D0 (LSB)  |          |               |                                                      |

Figure 49: EEPROM Gain Bi 0x01E

| Register<br>Hex | Access | Bit       | Function | Default       | Note                                                 |

|-----------------|--------|-----------|----------|---------------|------------------------------------------------------|

|                 |        | D15 (MSB) |          |               |                                                      |

| 0x01E           | R/W    | :         | Gain Bi  | +1<br>decimal | Gain to the Bj value<br>Signed integer, range [-1;1] |

|                 |        | D0 (LSB)  |          |               |                                                      |

### Figure 50: EEPROM Linearization Table 0x05F to 0x07F

| Register<br>Hex | Access | Bit       | Content                              | Default | Note           |

|-----------------|--------|-----------|--------------------------------------|---------|----------------|

| 0x05F           |        |           | Angle linearization table, value 16  |         |                |

| 0x060           |        |           | Angle linearization table, value 0   |         |                |

| 0x061           |        |           | Angle linearization table, value 1   |         |                |

| :               |        |           |                                      |         |                |

| 0x06F           | R/W    | D15 to D0 | Angle linearization table, value 15  | 0000    | Signed integer |

| 0x070           | Π/ Ψ   | 013 10 00 | Angle linearization table, value -16 | 0000    | [-1;1]         |

| 0x071           |        |           | Angle linearization table, value -15 |         |                |

| :               |        |           |                                      |         |                |

| 0x07E           |        |           | Angle linearization table, value -2  |         |                |

| 0x07F           |        |           | Angle linearization table, value -1  |         |                |

#### Figure 51: EEPROM Pre-Scale Linearization 0x1CF

| Register<br>Hex | Access | Bit       | Function      | Default       | Note                  |

|-----------------|--------|-----------|---------------|---------------|-----------------------|

|                 |        | D15 (MSB) | Pre-Scale     |               |                       |

| 0x1CF           | R/W    | :         | Linearization | +1<br>decimal | Signed integer [-8;8] |

|                 |        | D0 (LSB)  | Factor        |               |                       |

Figure 52:

EEPROM Post-Processing Offset 0x1D0

| Register<br>Hex | Access | Bit       | Function                  | Default | Note                          |

|-----------------|--------|-----------|---------------------------|---------|-------------------------------|

|                 |        | D15 (MSB) |                           |         |                               |

| 0x1D0           | R/W    | :         | Post Processing<br>Offset | 0       | Signed integer [-32768;32767] |

|                 |        | D0 (LSB)  |                           |         |                               |

am

## Figure 53:

EEPROM Post-Processing Gain 0x1D1

| Register<br>Hex | Access | Bit       | Function                | Default       | Note                  |  |

|-----------------|--------|-----------|-------------------------|---------------|-----------------------|--|

|                 | R/W    | D15 (MSB) |                         |               |                       |  |

| 0x1D1           |        | :         | Post Processing<br>Gain | +1<br>decimal | Signed integer [-4;4] |  |

|                 |        | D0 (LSB)  |                         |               |                       |  |

Figure 54: EEPROM Clamp Low 1 0x1D2

| Register<br>Hex | Access | Bit       | Function    | Default           | Note                          |

|-----------------|--------|-----------|-------------|-------------------|-------------------------------|

|                 | R/W    | D15 (MSB) | Clamp Low 1 | -32768<br>decimal | Signed integer [-32768;32767] |

| 0x1D2           |        | :         |             |                   |                               |

|                 |        | D0 (LSB)  |             |                   |                               |

# Figure 55:

EEPROM Clamp High 1 0x1D3

| Register<br>Hex | Access    | Bit       | Function     | Default          | Note                          |

|-----------------|-----------|-----------|--------------|------------------|-------------------------------|

|                 | 0x1D3 R/W | D15 (MSB) | Clamp High 1 | 32767<br>decimal | Signed integer [-32768;32767] |

| 0x1D3           |           | :         |              |                  |                               |

|                 |           | D0 (LSB)  |              |                  |                               |

Figure 56:

EEPROM Clamp Low 2 and Clamp High 2 (LSBs) 0x1F5

| Register<br>Hex | Access | Bit       | Function                              | Default | Note                                                                                                                                                                  |

|-----------------|--------|-----------|---------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |        | D15 (MSB) |                                       | 0       | Clamp High 2 (LSBs) value for PWM                                                                                                                                     |

|                 | R/W    | :         | Clamp High 2<br>(LSBs)<br>Clamp Low 2 | :       | and analog output. DSW not<br>effected.<br>4 lower LSBs [0;16]<br>Clamp Low 2 value for PWM and<br>analog output. DSW not effected.<br>12 bit unsigned value [0;4096] |

| 0x1F5           |        | D12       |                                       | 0       |                                                                                                                                                                       |

| UXII S          |        | D11       |                                       | 0       |                                                                                                                                                                       |

|                 |        | :         |                                       | :       |                                                                                                                                                                       |

|                 |        | D0 (LSB)  |                                       | 0       |                                                                                                                                                                       |

#### Figure 57: EEPROM Clamp High 2 (MSBs) 0x1F6

| Register<br>Hex | Access | Bit                          | Function | Default                              | Note                              |

|-----------------|--------|------------------------------|----------|--------------------------------------|-----------------------------------|